ATtiny26_Analog-Digital-Wandler_ADC_8

Werbung

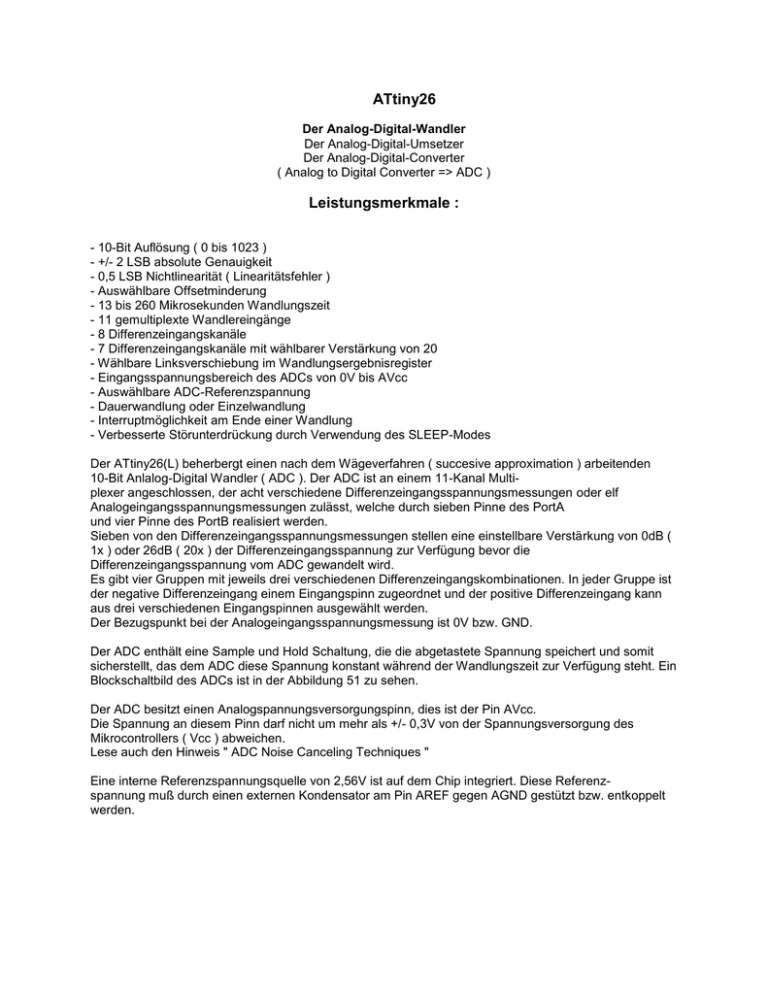

ATtiny26 Der Analog-Digital-Wandler Der Analog-Digital-Umsetzer Der Analog-Digital-Converter ( Analog to Digital Converter => ADC ) Leistungsmerkmale : - 10-Bit Auflösung ( 0 bis 1023 ) - +/- 2 LSB absolute Genauigkeit - 0,5 LSB Nichtlinearität ( Linearitätsfehler ) - Auswählbare Offsetminderung - 13 bis 260 Mikrosekunden Wandlungszeit - 11 gemultiplexte Wandlereingänge - 8 Differenzeingangskanäle - 7 Differenzeingangskanäle mit wählbarer Verstärkung von 20 - Wählbare Linksverschiebung im Wandlungsergebnisregister - Eingangsspannungsbereich des ADCs von 0V bis AVcc - Auswählbare ADC-Referenzspannung - Dauerwandlung oder Einzelwandlung - Interruptmöglichkeit am Ende einer Wandlung - Verbesserte Störunterdrückung durch Verwendung des SLEEP-Modes Der ATtiny26(L) beherbergt einen nach dem Wägeverfahren ( succesive approximation ) arbeitenden 10-Bit Anlalog-Digital Wandler ( ADC ). Der ADC ist an einem 11-Kanal Multiplexer angeschlossen, der acht verschiedene Differenzeingangsspannungsmessungen oder elf Analogeingangsspannungsmessungen zulässt, welche durch sieben Pinne des PortA und vier Pinne des PortB realisiert werden. Sieben von den Differenzeingangsspannungsmessungen stellen eine einstellbare Verstärkung von 0dB ( 1x ) oder 26dB ( 20x ) der Differenzeingangsspannung zur Verfügung bevor die Differenzeingangsspannung vom ADC gewandelt wird. Es gibt vier Gruppen mit jeweils drei verschiedenen Differenzeingangskombinationen. In jeder Gruppe ist der negative Differenzeingang einem Eingangspinn zugeordnet und der positive Differenzeingang kann aus drei verschiedenen Eingangspinnen ausgewählt werden. Der Bezugspunkt bei der Analogeingangsspannungsmessung ist 0V bzw. GND. Der ADC enthält eine Sample und Hold Schaltung, die die abgetastete Spannung speichert und somit sicherstellt, das dem ADC diese Spannung konstant während der Wandlungszeit zur Verfügung steht. Ein Blockschaltbild des ADCs ist in der Abbildung 51 zu sehen. Der ADC besitzt einen Analogspannungsversorgungspinn, dies ist der Pin AVcc. Die Spannung an diesem Pinn darf nicht um mehr als +/- 0,3V von der Spannungsversorgung des Mikrocontrollers ( Vcc ) abweichen. Lese auch den Hinweis " ADC Noise Canceling Techniques " Eine interne Referenzspannungsquelle von 2,56V ist auf dem Chip integriert. Diese Referenzspannung muß durch einen externen Kondensator am Pin AREF gegen AGND gestützt bzw. entkoppelt werden. Die Arbeitsweise des ADC ( Operation ) Der ADC wandelt eine analoge Eingangsspannung mittels Wägeverfahren ( succesive approximation ) in einen 10-Bit Digitalwert um. Dabei entspricht der kleinste Wert GND und der höchste, der Spannung die am AREF-Pin minus ein LSB. Wahlweise kann die Referenzspannung von AVcc, die interne 2,56V oder eine externe Spannungsquelle die mit dem AREF-Pin verbunden wird stammen. Diese wird durch die REFS-Bits im Register ADMUX eingestellt. Um Störeinflüsse auf die interne Referenzspannungsquelle zu verringern, sollte extern an dem AREF-Pin ein Kondensator gegen AGND geschaltet werden. Die Auswahl eines Analogeingangsspannungskanals oder eines Differenzeingangsspannungskanals wird mit den MUX-Bits im ADMUX-Register bestimmt. Außer den ADC Eingangskanalpinnen ADC10 bis ADC0 können noch das GND-Potential, sowie eine Bandgap ( VBG ) von 1,18V als Analogeingangsspannung gewählt werden. Eine festgelegte Auswahl von ADC-Eingängen, kann als positiver und negativer Anschluß des Differenzspannungsverstärkers verwendet werden. Falls die Eingangskanäle auf den Differenzspannungsverstärker geschaltet sind, bestimmt der eingestellte Verstärkungsfaktor die höhe der Differenzspannung die der ADC wandelt. Zu beachten ist hierbei das der positive Anschluß größer sein muß als der negative, ansonsten geht der Differenzspannungsverstärker in die negative Sättigung von 0V ( GND ). Bei der Analogeingangsspannungsmessung ( Single ended ) gibt es keine Verstärkung. Der ADC kann in zwei Betriebsarten arbeiten. Die Einzelwandlung ( Single Conversation ) und die Dauerwandlung ( Free running ). Die Einzelwandlung muß immer neu gestartet werden. Im Dauerwandlungsbetrieb starten die Wandlungszyklen automatisch und die Wandlungsergebnisse werden immer erneuert. Im ADCSR-Register wird mit dem Bit ADFR zwischen diesen beiden Betriebsarten ausgewählt. Weiterhin wird in diesem Register durch das setzen des Bits ADEN der ADC eingeschaltet. Das auswählen der Referenzspannung oder eines Eingangskanals ist ohne das Einschalten des ADCs durch das ADEN-Bit wirkungslos. Da der ADC keine Leistung aufnimmt, solange das ADEN-Bit nicht gesetzt ist, sollte der ADC durch dieses Bit immer ausgeschaltet werden, bevor der Mikrocontroller in einen der Energiesparmodi geht.Die Wandlung wird gestartet, wenn das ADSC-Bit gesetz wird. Dieses Bit bleibt während der Wandlung gesetzt und wird nach Abschluß der Wandlung durch die Hardware wieder rückgesetzt. Wird während einer Wandlung der Eingangskanal gewechselt, wird erst am Ende der laufenden Wandlung der Kanal umgeschaltet. Der ADC erzeugt ein 10-Bit Wandlungsergebnis, welches im ADC Datenregisterpaar ADCH und ADCL zur Verfügung steht. Standardmäßig wird dieses Ergebnis rechtbündig aus dem Registerpaar gelesen. Es besteht aber auch die Möglichkeit das Ergebnis linksbündig auszulesen. Dies geschieht durch das setzen des ADLAR-Bits im Register ADMUX. Falls das Ergebnis linksbündig ausgelesen wird und nicht mehr als 8-Bit Genauigkeit benötigt wird, reicht es nur das ADCH Ergebnisregister auszulesen. Ansonsten ist es nötig zuerst das ADCL-Register und sofort danach das ADCH-Register auszulesen. Ansonsten wird der Zugriff auf das ADC-Ergebnisregister so lange geblockt, bis das ADCH-Register gelesen wurde. Danach ist der Zugriff auf das Ergebnisregisterpaar ADCH und ADCL wieder freigegeben. Der ADC besitzt eine eigene Interrupt, die ausgelöst wird wenn die Wandlung beendet ist und somit das Ergebnis im Registerpaar ADCH und ADCL vorliegt. Die Interrupt wird auch dann ausgelöst, falls dies zum Zeitpunkt des Zugriffblockens auf das ADC-Ergebnisregisterpaar stattfindet. Hierbei geht jedoch das aktuelle Wandlungsergebnis verloren. Vorteiler und Wandlungsablaufreihenfolge ( Prescaling and Conversion Timing ) Der nach dem Wägeverfahren arbeitende Analog-Digital-Wandler braucht eine Taktfrequenz von 50kHz bis 200kHz. Falls eine geringere Auflösung als 10-Bit genügt, kann die Taktfrequenz des ADCs höher als 1MHz sein. Somit erhält man eine höhere Abtastrate. Das ADC-Modul besitzt einen Vorteiler, mit dem man den Systemtakt auf einen für den ADC brauchbaren Wert herunterteilen kann. Ab eines Systemtaktes von 100kHz, läßt sich mit den ADPS-Bits im Register ADCSR ein brauchbarer Takt für den ADC ableiten. Der Vorteiler beginnt seine Arbeit, sobald das ADEN-Bit im Register ADCSR gesetzt wird. Der Vorteiler arbeitet solange wie das ADEN-Bit gesetzt ist und bleibt solange im Resetzustand wie dieses Bit rückgesetzt bzw. gelöscht ist. Eine Wandlung startet bei der nachfolgenden steigenden Flanke des ADC-Taktes, nach dem das ADSC-Bit im Register ADCSR gesetzt wurde.********************* Eine Wandlung dauert 13 ADC-Takte. In bestimmten Situationen braucht der ADC mehrere Takte zum initialisieren und um Offsetfehler zu minimieren. Die erweiterte Wandlung ( Dummy Conversation ) braucht 25 ADC-Takte und ist die erste Wandlung nachdem der ADC eingeschaltet wurde, d.h. nachdem das ADEN-Bit im Register ADCSR gesetzt wurde. Besondere Beachtung gilt bei dem Wechsel eines Differenzeingangs. Wenn ein Differenzeingang ausgewählt wurde, braucht die Verstärkerstufe mehr als 125 Mikrosekunden um sich auf den Wert einzustellen. Deshalb sollte eine Wandlung nach einem Differenzeingangswechsel nicht vor diesen 125 Mikrosekunden gestartet werden. Ansonsten sollte dieses Wandlungsergebnis verworfen werden. Gleiches gilt bei dem Wechsel der Referenzspannung bei der Differenzeingangsspannungswandlung ( REFS 1:0 in ADMUX ). The actual sample-and-hold takes place 1.5 ADC clock cycles after the start of a normal conversion and 13.5 ADC clock cycles after the start of an extended conversion. Wenn eine Wandlung beendet ist, gelangt das Ergebnis in das ADC Datenregisterpaar und ADIF wird zeitgleich gesetzt. Im Einzelwandelmode wird auch zu diesem Zeitpunkt das ADSC-Bit gelöscht. Danach kann durch die Software das ADSC-Bit erneut gesetzt werden und die nächste Wandlung beginnt mit der ersten steigenden Flanke des ADC-Taktes nach dem setzen dieses Bits. Im Dauerwandelbetrieb startet die nächste Wandlung direkt nach Abschluß der vorherigen. Das ADSC-Bit bleibt hierbei ständig gesetzt. Die verwendung des Dauerwandelbetriebs bei einem 200kHz ADC-Takt ergibt die kürzeste Wandlungszeit von 65 Mikrosekunden, was 15.000 Wandlungen pro Sekunde ergibt. Eine Aufstellung der verschiedenen Wandlungszeiten ist in Tabelle 43 zu sehen. Kanalwechsel oder Referenzspannungsauswahl ( Changing Channel or Reference Selection ) Die MUXn und REFS1:0 Bits sind in einem Temporären Register zwischengespeichert auf welches die CPU zugreifen kann. Dies stellt sicher, das ein Kanalwechsel oder das ändern der Referenzspannung zu einem sicheren Zeitpunkt während der Wandlung geschieht. Der Kanalwechsel oder eine Änderung der Referenzspannung wird vor beginn jeder Wandlung erfasst. Vor dem Wandlungsstart wird die Kanalauswahl sowie das ändern der Referenz geblockt, damit dem ADC genügend Abtastzeit bleibt. Das kontinurierliche erfassen der Änderungen geschieht im letzten ADC-Takt bevor die Wandlung vollständig abgeschlos-sen ist ( Bevor das ADIF-Bit im ADCSR-Register gesetzt ist ). Es gilt zu beachten, das eine Wandlung mit der ersten steigenden Flanke des ADC-Taktes erfolgt, nachdem das ADSC-Bit gesetzt wurde. Somit hat der Programmierer darauf zu ach- ten, das keine Änderung des Kanals oder der Referenzspannung in ADMUX geschrieben wird, bevor nicht ein ADC-Takt nach dem setzen des ADSC-Bits vergangen ist. Besondere Vorsicht ist geboten, wenn ein Differenzkanal gewechselt werden soll. Beim Wechsel auf einen anderen Differenzkanal braucht die Verstärkerstufe mindestens 125 Mikrosekunden, um sich zu stabilisieren. Somit sollte eine Wandlung frühestens 125 Mikro- sekunden nach einem Differenzkanalwechsel erfolgen. Ansonsten wird das Wandlungsergeb- nis während dieser Phase unbrauchbar. Die selbe Wartezeit sollte auch nach dem Wechsel der Referenz vergehen, bevor eine Wandlung gestartet wird. ADC Störunterdrückungsfunktion ( ADC Noise Canceler Function ) Die ADC Störunterdrückungsfunktion ermöglicht es Wandlungen im " ADC Noise Reductions mode " auszuführen. Lese dazu Seite 38 " Power Management and Sleep Modes ". Hierdurch werden Signalstörungen die durch den CPU-Kern oder andere Ein,- Ausgabemodule erzeugt werden vermindert. Falls andere Ein,- Ausgabemodule während einer Wandlung aktiv sein müssen, arbeitet dieser Mode ähnlich dem IDLE-Mode. Um die ADC Störunterdrückungsfunk- tion zu nutzen müssen folgende Punkte eingehalten werden : 1. Sicherstellen, das der ADC freigegeben ist und sich nicht in einer Wandlung befindet. Der Einzelwandlungsmode und die Wandlung-beendet Interrupt müssen eingestellt sein. ( ADEN =1, ADSC =0, ADFR =0, ADIE =1 ) 2. In dem ADC Noise Reduction Mode oder IDLE-Mode eintreten. Der ADC startet dann einmal die Wandlung, wenn die CPU steht. 3. Falls vorher keine andere Interrupt auftritt, weckt die ADC-Interrupt die CPU auf und die Wandlung-beendet Unterbrechungsroutine ( ADC Conversion Complete Interruptroutine ) wird ausgeführt. ADC Wandlungsergebnis ( ADC Conversion Result ) Nachdem Wandlungsende d.h., wenn das ADIF-Bit gesetzt ist, findet sich das Wandlungser- gebnis im Registerpaar ADCH und ADCL. Bei der Einzelwanlung kommt das Ergebnis nach folgender Formel zu stande : ADC = Vin * 1024 / Vref Vin ist die Spannung am ausgewähltem Eingangskanal und Vref ist die ausgewählte Referenzspannung. Siehe Tabelle 45 auf der Seite 103 und Tabelle 46 auf der Seite 104. Ein Wandlungsergebnis von $3FF entspricht der ausgewählten Referenzspannung minus einem LSB. Bei der Differenzeingangsspannungswandlung kommt das Ergebis nach dieser Fomel zu stande : ADC = ( Vpos - Vneg ) * GAIN * 1024 / Vref Vpos ist die Spannung am positiven Eingang des Differenzverstärkers, Vneg ist die Spannung am negativen Eingang des Differenzverstärkers, GAIN ist der ausgewählte Verstärkungsfaktor und Vref die ausgewählte Referenzspannungsquelle. Daran denken das Vpos eine höhere Spannung aufweisen sollte als Vneg, weil sonst der Differenzverstärker in die negative Säti- gung geht und das ADC Wandlungsergebnis null beträgt. Bild 56 zeigt die Spannungs zu Digitalumsetzung bei der Differenzspannungsmessung. In der Tabelle 44 sind die Wandlungsergebnisse mit den Differenzeingängen ADCn und ADCm, der ausgewählten Verstärkung des Verstärkers ( GAIN ) und der ausgewählten Referenzspannung ( VREF ) dargestellt. Beispiel : ADMUX = $EB (ADC0 - ADC1, 20-fache Verstärkung, 2,56V interne Referenzspannung, linksbündiges Ergebnis ) Die Spannung am ADC0-Kanal ist 400mV, die Spannung am ADC1-Kanal ist 300mV. ADC = 1023 * 20 * ( 400 - 300 ) / 2560 = 800 => $320 ADCL wird als null gelesen und ADCH als $C8. Ist das ADLAR-Bit gelöscht, wird das Ergebnis rechtbündig ausgelesen und ergibt ADCL = $20, ADCH = $03. ADMUX ADC Multiplexer Selection Register # Bit 7, 6 REFS1, REFS0 Reference Selections Bits Diese Bits wählen die Spannungsrefenzquelle für den ADC aus. Siehe Tabelle 45. Werden diese Bits geändert, während eine Wandlung läuft, wird die Änderung erst nach der Wandlung aktiv ( ADIF-Bit im ADCSR-Register ist gesetzt ). Nachdem Ändern dieser Bits sollte das erste Ergebnis der Wandlung ignoriert werden, um eine bestmögliche Genauigkeit zu erreichen. Falls Differenzeingänge benutzt werden, ist es nicht ratsam AVcc oder eine externe Aref zu benutzen, die höher ist als AVcc - 0,2V, da dies die ADC Genauigkeit beeinträchtigt. Die interne Referenzspannungsquelle darf nicht benutzt werden, wenn eine externe am Pin Aref angeschlossen ist. # Bit 5 ADLAR ADC Left Adjust Result Das ADLAR-Bit ist für die Ausrichtung des Wandlungsergebnisses beim auslesen im ADC Datenregister zuständig. Falls es gesetzt ist, wird es linksbündig ausgelesen ansonsten rechtsbündig. Eine Änderung dieses Bits wirkt sich sofort auf das ADC-Datenregister aus, unabhängig davon, ob eine Wandlung gerade läuft oder nicht. Eine vollständige Beschreibung dieses Bits ist auf der Seite 106 unter " ADC Data Register ADCL and ADCH " vorhanden. # Bit 4..0 MUX4..MUX0 Analog Channel and Gain Selection Bits Mit diesen Bits wird eingestellt, welche von den ADC zugehörigen Eingangspins bzw. Eingangspinkombinationen an den ADC angekoppelt werden. Dies beinhaltet auch die Verstärkungsfaktorauswahl bei der Differenzspannungsmessung. Weitere Details sind der Tabelle 46 zu entnehmen. Eine Änderung dieser Bits, während einer Wandlung wirken sich erst am Ende dieser aus ( Das Ende einer Wandlung zeigt das gesetzte ADIF-Bit im Register ADCSR an ). ADCSR ADC Control and Status Register # Bit 7 ADEN ADC Enable Wird das Bit gesetzt, so wird der ADC eingeschaltet und wird es gelöscht, so wird er ausgeschaltet. Wird der ADC während einer Wandlung abgeschaltet, so wird die Wandlung abgebrochen. Der abgeschaltete ADC verbraucht keine Leistung. # Bit 6 ADSC ADC Start Conversation Eine Einzelwandlung wird jedesmal durch setzen dieses Bits gestartet. Im Dauerwandlungsmode muß dieses Bit nur für die erste Wandlung gesetzt werden. Das erste mal, wenn dieses Bit gesetzt wird, nachdem der ADC eingeschaltet ist oder dieses Bit zeitgleich mit dem einschalten des ADCs gesetzt wird, erfolgt vorangehend eine Dummy-Wandlung. Diese Dummy-Wandlung dient der initialisierung des ADCs. Das Auslesen des ADSC-Bits während einer Wandlung ergibt eine Eins. Nach der Wandlung kehrt es auf Null zurück. Bei einer vorangehenden Dummy-Wandlung bleibt das ADSC-Bit so lange auf high bis die darauf folgende richtige Wandlung beendet ist. Ein rücksetzen dieses Bits ist nicht möglich. # Bit 5 ADFR ADC Free Running Select Falls dieses Bit gesetzt wird, arbeitet der ADC im Dauerwandlungsmode. In diesem Mode werden die Wandlungen automatisch nach Wandlungsende neu gestartet, sowie das Datenregister aktualisiert. Durch löschen dieses Bits wird der Dauerwandlungsmode abgebrochen. # Bit 4 ADIF ADC Interrupt Flag Dieses Bit wird gesetzt, wenn eine ADC Wandlung beendet ist und das ADC Datenregister aktualisiert wurde. Die dazugehörige ADC Wandlung-beendet Unterbrechungsroutine wird angesprungen, wenn das Bit ADIE und das I-Flag gesetzt sind. Das ADIF-Bit wird beim Einsprung in die IRQ-Vektor-Tabelle durch die Hardware wieder zurückgesetzt. Alternativ kann das ADIF-Bit auch druch schreiben einer Eins gelöscht werden. Dies gilt es zu beachten, falls eine read-modify-write sequenz auf das ADCSR-Register angewendet wird, da hierdurch eine laufende Interrupt abgebrochen werden kann. Gleiches gilt für die Befehle SBI und CBI. # Bit 3 ADIE ADC Interrupt Enable Wenn dieses Bit und das I-Flag im Statusregister SREG gesetzt werden, so wird die ADC Wandlung-beendet Unterbrechungsroutine freigegeben. # Bit 2..0 ADPS2..0 ADC Prescaler Select Bits Diese Bits legen den Teilungsfaktor des Systemtaktes für den ADC-Takt fest. ADCH und ADCL ADC Data Register Am Wandlungsende ist das Ergebnis in diesen beiden Registern zu finden. Das ADLAR-Bit im Register ADMUX bewirkt wie das Ergebnis aus diesen Registern gelesen wird. Falls das ADLAR-Bit gesetzt ist, wird das Ergebnis linksbündig ausgerichtet. Falls das ADLAR-Bit gelöscht ist ( Grundeinstellung ), wird das Ergebnis rechtsbündig ausgelesen. Wenn das Ergebnis linksbündig ausgerichtet ist und als Genauigkeit 8-Bit ausreichen, dann reicht es nur das ADCH-Register auszulesen. Sonst ist wie üblich zuerst das ADCL und direkt danach das ADCH-Register auszulesen. # ADC9..0 ADC Conversion Result Diese Bits stellen das Ergebnis der Wandlung dar. Bei der Differenzeingangsspannungsmessung ist dies das Ergebnis nach der wählbaren Verstärkung, wie in der Tabelle 46 auf der Seite 104 gezeigt. Bei der normalen Wandlung ( Single ended ) bedeutet ein Ergebnis von $000 die analoge Masse und ein Ergebnis von $3FF stellt die ausgewählte Referenzspannung minus einem LSB dar. Einlesen mehrerer Analogeingänge Scanning Multiple Channels Der Wechsel eines Analogeingangs ist solange verzögert, bis eine Wandlung beendet ist. Der Dauerwandlungsmode ( Free Running Mode ) kann dazu genutzt werden um mehrere Analogeingänge nacheinander einzulesen ohne den Wandler dabei zu unterbrechen. Zum nacheinander Einlesen der Anlalogeingänge wird normalerweise die Wandlung-beendet Unterbrechungsroutine ( ADC Conversion Complete Interrupt ) genutzt. Folgende Dinge gibt es noch zu Berücksichtigen. Bei der Wandlung-beendet Interruptroutine steht das Ergebnis bereit zum auslesen. Im Dauerwandlungsmode beginnt die nächste Wandlung sofort nachdem die Wandlungsende Flagge ( ADIF ) gesetz wurde. Das bedeutet, das wenn der Eingangskanal gewechselt wurde, erst noch eine Wandlung mit dem vorher eingestelltem Eingangskanal vorgenommen wird. ADC Störsignalunterdrückungstechniken ADC Noise Canceling Techniques Digitalschaltungen innerhalb und außerhalb des ATtiny26(L) erzeugen Störsignale, welche evtl. die Genauigkeit des Analogsignals beeinflussen. Falls die Wandlungsgenauigkeit sehr wichtig ist, kann mit folgenden Mitteln der Störsignaleinfluss verringert werden. 1. Der analoge Teil des ATtiny26(L) und alle anderen analogen Schaltungsteile der Gesamten Schaltung, sollten eine gemeinsame Massefläche auf der Platine haben. Diese analoge Massefläche sollte nur an einem einzigen Punkt mit der digitalen Massefläche auf der Platine verbunden werden. 2. Anlaloge Leiterbahnen so kurz wie möglich halten. Sicherstellen, das analoge Leiterbahnen über die analoge Massefläche geführt werden und weit weg von digital schaltenden Leiterbahnen. 3. Der AVcc Pin des ATtiny26(L) sollte über eine LC-Netzwerk mit dem digitalen Versorgungsspannungsanschluß ( Vcc ) verbunden werden. Siehe Zeichnung 57 auf der Seite 108. 4. Benutze die ADC noise Canceler funktion um die von der CPU erzeugten Störsignale zu minimieren. 5. Falls einige an den ADC angekoppelten Pins des selben Ports als Ausgang geschaltet sind, ist es wichtig das diese während einer Wandlung nicht schalten. Offset Kompensationseinrichtung Offset Compensation Schemes Die Verstärkerstufe hat einen Schaltungsteil integriert, welcher den Offset bei Differenzeingangskanälen soweit wie möglich gegen Null herabsetzt. Der übrige Offset im analogen Pfad, kann direkt gemessen werden, indem der selbe Eingangskanal für beide Differenzeingänge benutzt wird. Dieser Offset kann dann in der Software vom Wandlungsergebnis abgezogen werden. Der Gebrauch dieser Softwaremäßigen Offsetkorrektur kann den Offsetfehler auf unter einem LSB bei einem beliebigen Differenzeingangskanal halten.