Logikfamilien 1.CMOS Familie

Werbung

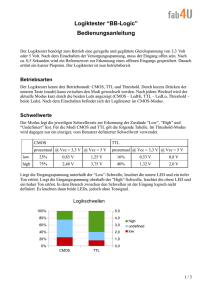

Seitel 1.EDTReferat Logikfamilien ; Logikfamilien 1.CMOS Familie: CMOS steht für Complementary Symmetry Metal Semiconductor. 1.1Inverter: Wie man aus der Schaltung 1 ersieht besteht ein CMOS Nicht Glied( Inverter) aus einem P-Kanal ( Tl)und einem N- Kanal (T2) Transistor (MOSFET ). ·-t~- Legt man am Eingang A einen High Pegel von z. B. 5V an, so steuert der Transistor ( T2 ) durch. Der Source - und Substrat - Anschluß liegt auf OV. => UGs=5V. => Der Transistor T1 spent. Wenn T1 sperrt und T2 durchsteuert, so liegt am Ausgang Z ein Low - Pegel von OV. Legt man am Eingang OV an, so sperrt T2, weil UG~=OV ist. Für T1 ergibt sich jedoch eine Gate Source Spannung von -5V, da der Sourceanschluß auf -t5V und der Gate Anschluß auf OV liegen. => T1 steuert durch und T2 sperrt und der Ausgang Z geht auf High. Hat das Glied den Ausgangspegel 0, fließt praktisch kein Strom von Us nach Masse, da T1 gesperrt ist. Hat das Glied den Ausgangspegel High, nießt ebenfalls kein Strom, da jetzt T2 gespent ist. Zum Ansteuern nachgeschalteter Glieder wird auch kein Strom benötigt, da die Feldeffektransistoren praktisch leistungslos gesteuert werden. Nur während des Umschaltens von einem Zustand in den anderen muß die Spannungsquelle einen geringeren Strom liefern, da beide Transistoren eine kurze Zeit lang leiten. Der eine Transistor geht vom leitenden in den gesperrten Zustand über und ist noch nicht vollständig gesperrt, der andere geht vom gesperrten in den leitenden Zustand über und ist nicht mehr vollständig gesperrt. Es müssen auch die Transistorkapazitäten umgeladen werden. Cmos Glieder sind so aufgebaut, daß ausgenommen im Umschaltzeitpunkt kein Strom durch die Schaltung nießt. => Der Leistungsbedarf von CMOS Gliedern ist extrem gering, steigert sich aber mit der Frequenz ( f steigt => P steigt ). 5HNA96 ************* I.EDT Referat Wien am 07.11.1995 Logikfamilien '.2 Übertraeuneskennlinie: 7~r-r7 ~tnlrrunp 6utch 1 ;, I t·'"" I~Pi~ IILb:<rc·JIllut(·rl Michael Hacker SeiteZ U· K) U,~15V Tt~lkr lo u, ro ao la-~livlc Wie man aus der vorhergehenden Schaltung sieht, sind in der Schaltung keine Widerstände vorhanden, so daß der Ausgang U, auf +U, ( Betriebsspannung ) und auf OV gehen kann. Aus der Übertragungskennlinie ist ersichtlich, daß die logischen Pegel von der Betnebsspannung abhängig sind. Der zulässige Betriebsspannwngsbereich ist bei CMOS Schalh~ngen sehr groß. Bei Silcon Gate Schaltungen liegt er zwischen 3 und 6V, bei Metal Gate Schaltungen zwischen 3 und IsV. Dies ist besonders für battenebetriebene Schaltungen von großer Bedeutung, da die Schwankung der Versorgungspannung m einem großen Bereich zulässig ist. Der Umschaltpegel liegt aus Symetnegründen genau bei der halben Betriebsspannung. Dies hat den Vorteil, daß man dadurch eine gute Rauschunterdriickung erzielt. 1.3 Besonderheiten der CMOS Familie: - die Eingänge haben fast einen unendlich hohen Eingangswiderstand - der Stromverbrauch ist gleich null außer beim Umschalten - der Umschaltpegel liegt bei der halben Betriebspannung => gute Rauschunterdrückung - breiter Betriebsspannungsbereich von 3 -18V - der Logikhub geht von Masse bis Betriebsspannung - die Ausgangsstufen erzeugen keine großen Stromspitzen auf den Versorgungsleitungen d~ h~ sie tragen selber nichts zum Rauschen bei - die Übergangszeiten( Ausgangsänderungen) sind bei CMOS so ausgelegt daß sie länger als die Laufieit ( Verzögerung zwischen Ein und Ausgang) sind und dadurch Spannungsspitzen und Rauschen unterdrücken 5HNA96 ************* 1.EDT Referat Wien am07.11.1995~-~-~-~-[ic"-'Logikfamilien Seite3 1.4 CMOS Familien: Derzeit gibt es verschiedene Serien wobei meist die nächstfolgende Familie Verbesserungen gegenüber der vorhergehenden Serie enthält. Diese sind die Senen CD4000, 74C00, 74HC00, 74HCT00 und 74AC/ACT00. 1.4.1 CD 4000 Serie: Bei dieser Baureihe von der Firma RCA stehen etwa 150 verschiedene Bausteine zur Verfügung. Grundschaltung ist der Inverter; den großen Nachteil bildet allerdings die wesentlich größere Verzögerung als bei TTL ( CMOS typisch 80ns TTL typisch 30ns) Unterschiede gibt es auch zwischen den Typen CD 4000A und CD 4000B. Der neuere Typ CD 4000B hat im Gegensatz zu Typ CD 4000A zusätzlich am Ausgang noch eine Treiberstufe (Pu~erstufe ). Die empfohlene Positive Betriebsspannung ( kann auch negativ sein ) kann zwischen +3 und ~18V liegen. Die Mindestspannung für logisch 1 ( High) am Eingang muß 70% der Betriebsspannung betragen, der maximale Logikpegel für logisch 0 ( Low ) darf 30% der Betriebsspannung nicht überschreiten. +U +V \I II 8u -·· UnO·pvll·ct I~ (8) 2 (rJ \( unwamm (r9 (tll / I ,O·pul(rrl U +U ~wo~no 2 zlln (r)Ob·r(ngunO,Cu~lllon (8) Rs·kllo~urll(O( ·In·n ~kh I·r~l·m ~ndMIII Clngly) Die Sene 4000 ist im allgemeinen nicht pinkompatibel mit den entsprechenden TTL Bausteinen. Weiters ist für ein zusammenschalten von TTL mit CMOS Logik eine Interface Schaltung notwendig. 5HNA96 **************** 1.EDT Referat Wien am 07.11.1995 Logikfamilien Michael Hacker Seite4 1.4.2 74C00 Serie: Diese Serie wurde völlig pinkompatibel zu den Serien 7400 und 74LS00 ( LS = Low Power Schottky ) entwickelt. Der Vorteil in dieser Serie liegt bei der wesentlich niedrigeren Leistungsaufnahme gegenüber der Standart TTL Familie. Obwohl sie sich mit der Betriebsspannung von +3 bis +15V betreiben läßt, kann sie direkt 74LS00 Bausteine bei der Venvendung einer Betriebsspannung von +5V ersetzen. In diesem Fall können 74C Bausteine typisch zwei 74LS00 Lasten treiben. 1.4.3 74HC/HCT 00, 74HC/HCT4000 und 74AC/ACT Familie: Sowohl die Familien 74HC00 (High speed CMOS )und 74HCT00 (High speed CMOS und TTL kompatibel) sind gleich schnell wie die 74LS Serie und verbrauchen weniger Leish~ng abhängig von der Arbeitsfrequenz. Sie sind ebenfalls pinkompatibel mit den TTL Familien. Die Serien 74HC/HCT4000 sind pinkompatibel mit der ursprünglichen 4000er Sene, die Spannungspegel sind jedoch TTL kompatibel, wenn sie an +5V betrieben werden. Die Familien 74AC/ACT (Advanced CMOS ) besitzt die gleiche Pinbelegung wie TTL und erreicht Taktfrequenzen bis über 1SOMHz. 1.5 Log;ik und Transmissionsgatter: Alle logischen Funktionen kann man ja im Gn~nde durch Zusammenschalten von Invertern bzw. von N und P - Kanal Transistoren erreichen. Drei der wichtigsten sind das NOR, NAND Gatter mit zwei Eingängen und das Transmissionsgatter. 5HNA96 Wien am 07.11.1995 ****************** 1.EDT Referat Logikfamilien Michael Hacker SeiteS 1.5.1 NOR Gatter: Die zwei N - Kanal Transistoren sind parallel angeordnet, damit jeder Ausgang nach Masse ziehen kann, wenn eine positive Eingangsspannung vorliegt. Die beiden P - Kanal Transistoren smd in Serie geschalten, so daß beide zusammen arbeiten müssen, um den Awsgang auf U+ zu ziehen, wenn die Eingänge auf Masse liegen. Wenn entweder A oder B Positiv ist, wird der Weg zu U+ getrennt und der Weg zur Masse gelegt. Der Ausgang wird nur dann auf U+ gehen, wenn sowohl A und B an Masse liegen. *U O +U I X· · s\ X· *USGANO 1 AUSG~NC ( I I(+U I +u II +U II I n +U +U II (Al ~ch·llune 1.5.2 NAND Gatter: (s) Aguhn~nlr Bch·ll·c·L~glC (q W·hrM(,T~b·lk Bei dieser Schaltung sind die N - Kanal Transistoren in Serie gegen Masse geschalten und die P - Kanal Transistoren parallel zu U+. Wird einer der Eingänge auf Masse gelegt, so bewirkt dies, daß der Ausgang auf High geht. Der Ausgang geht nur dann auf Low, wenn beide Eingänge gleichzeitig auf High sind. ~ff I I +V n I I ~vxuJJc~ Cf-,AUXIAHG +U I +U EINGINGE ~ (A)~h·mni~ I +U I ~U ·i +U +U II (g) ~qu)v·leola Schal(srL00(1 (q W·hmat,Tlb·lla. 5HNA96 **************** 1.EDT Referat Wien am 07.11.1995 Logikfamilien Michael Hacker Seiteo 1.5.3 Transmissionsg;atter: Das Transmissionsgatter verbindet den Anschluß X mit dem Anschluß Y, wenn A positiv ist. Es trennt den Anschluß X vom Anschluß Y wenn A an Masse liegt. X und Y können sowohl Eingänge als auch Ausgänge darstellen, sie können digitale oder analoge Signale in jeder Richtung steuern. Die einzige Einschränkung besteht darin, daß die an X und Y liegende Spannung niemals höher als U+ oder negativer als das Massepotenial sein darf. +U x ~fJI I INGANClr EINGUJ<Y VSO*NO N I AUGMNO +U =4 1 ~i~ L4 I XZU~YZUX X 0·--b- ^Y I ~us *us ~i 1.6 Versorg;ung;: ! . (~Sch·ltung. (B) ~pu~nl·n,·c Sch.ll·r. (C1 Wlhrh~t,Tlkt~. CMOS Bausteine arbeiten über einen Bereich von +3 bis +15V ( B - Serie mit +18 bis +20V ). Mit Ausnahme 74HC/HCT die die Betriebsspannung von +5V venvenden ist die optimale Versorgungsspannung für CMOS +9 bis +12V. Bei dieser Spannung erhält man eine sehr schnelle Arbeitsweise und sehr gute Rauschunterdrückung. Sehr hohe Betriebsspannungen von 15 bis 18V sollten nicht venvendet werden, sie könnten zu Wärme und Verlustleistungsproblemen führen . IOnrA Vkrl·ehQ·t~r LS-TTL. 5V (mA ~ L~ur, a lo,, IlrA Vint~ch-Glttsr CMOS, 10V '01 .L ItHj Ió ,m ,,, ,~, Illd (·1L thonoumohnw vor,CMOI In ~h(k0101<·n ron d·r ~b·n~nqrnru. 5HNA96 Wien am 07.11.1995 ****************** Seite7 1.EDTReferat Logikfamilien ; Michael Hacker Dieses Bild zeigt wie sich die Stromau~ahme mit der Frequenz ändert. Mit Ausnahme für Systeme mit rmnimalster Leistungsaufnahme ist der Strom nahezu vernachlässigbar bei Niederfrequenz. Er steigt allerdings mit der Frequenz. Wenn ein CMOS Baustein mit ca. 2 bis 10 MHz betrieben wird , dann verbraucht er etwa soviel Strom wie ein 74LS00 Baustein. Der Betriebsstrom verdoppelt sich bei doppelter Versorgungsspannung venvende ich statt 5V eine Betriebsspannung von 10V brauche ich den doppelten Strom und die vierfache Leistung . 1.7 Eing;angsschutz: Die Eingänge von MOS - FETs sind im wesentlichen offene Schaltungen. Gleichzeitig ist jedoch die dielektrische Isolationsschicht des Gate-Kondensators sehr dWm. Wenn statische Elektrizität auf das Gate-Dielektrium gelangt, können daraus sehr hohe Feldstiuken resultieren und das Gate kann zerstört werden. Deshalb haben CMOS Bausteine interne herstellerspezifische Schutzschaltungen. I~NE~Md ~' "T' ~ DoOp(t· Olob( lln0·n0 m~ n*Lpnr, (m lam-010d· 0·0·n U··U. Elng·ng MO iU und U··r Ilrg·n rurl·ch·n * UIV Und U··r 1UO"r EIH -f·· ~I I·nrdl~d· O·O·n +u. lng·nq rm· Irl·oh·n ID)Vnb··urt· bo9Plt· DlOdl Eln0·n0 mb ·V una-W)V11·glh iurHsHn rVUndUL···114·n. Zu Bild A: Es leitet eine der Dioden, wenn die Eingangsspannung U+ überschreitet und es leitet die andere Diode wenn die Eingangsspannung Masse unterschreitet. Zu Bild B: Die Zenerdiode leitet für Eingangsspannungen < als Masse als Diode und für Eingangsspannungen über 30V als Zenerdiode. Die in Bild C verwendete Schaltung verkraftet Spannungen welche um 50V negativer sind als U+. Die Diode leitet in Vorwärtsrichh~ng für Spannungen über U+ und leitet als Zenerdiode bei 50V negativer als U+. Bei der Schaltung C können die Eingangssignale etwas positiver als U+ und etwas negativer als Masse sein. Diese Schutzschaltungen sind sehr gut gegen Statische Aufladungen haben aber den Nachteil, daß die Dioden gegen Überslastung durch Ströme geschützt werden müssen. Es ist notwendig den Eingangsstrom mit einer Schutzdiode auf IOmA zu begrenzen. 5HNA96 Wien am 07.11.1995 ********************************* 1.EDT Referat Logikfamilien Michael Hacker Seiteg 1.8 Reg;eln für die Anwendung; von CMOS: - Alle Eingänge müssen angeschlossen sei, entweder an Masse oder U, - Die Schutzschaltungen sollten im Betriebszustand keine Funktion ausüben. Sollte der Diodenstrom trotzdem venvendet, werden ist er auf IOmA zu begrenzen. - Venvendung von Testeingängen mit hoher Impedanz => wenn die Stromversorgung unterbrochen ist, ohne die Eingangsignale zu entfemen kann man die Schutzbeschaltung zerstören. - Statische Aunadungen müssen vermieden werden - Alle getakteten Eingangsignale die zur Logik gehen, sollten aufbereitet sein z.B. alle Schalter müssen entprellt sein. - Venvendung von kurzen Anstiegs und Abfallszeiten für den Takt (<5Cls) 2. TTL Logik: Die TTL Technik ist eine Weiterentwicklung der DTL Logik. Das wesentliche Merkmal der TTL Schaltungen ist der Multiemittertransistor am Gattereingang ( Bild a ). Liegen alle Eingänge des Multieminertransistor auf High, so arbeitet er invers. Die dargestellte Schaltung mit einer Gegentaktendstufe stellt ein NAND Gatter dar. Die Schaltung arbeitet wie folgt. Liegt mindestens ein Eingang ( Emitter ) auf Low, so wird der Eingangstransistor gesättigt leitend. Sein Basisstrom wird stets so groß gewählt, daß der Multiemittertransistor mit Sicherheit in den Sättigungszustand gesteuert wird d. h. er liegt in der Größenordnung von ImA. Als Kollektorstrom nießt jedoch nur ein aus der Basis des Transistors T2 austretender Sperrstrom, so daß der Emitterstrom nahezu gleich dem Basisstrom ist. Transistor T2 wird gesperrt, da seine Basis auf Low gezogen wlrd. Damit wird auch der Transistor T4 gesperrt, T3 dagegen wird leitend und zieht als Emitterfolger den Ausgang auf High. Sofem alle Emitter des Transistors T1 auf High Potential geschaltet werden, wird T1 invers leitend dabei ist zu, beachten daß die inverse Stromverst~irkung wesentlich kleiner als eins ist, so daß ein inverses Durchschalten vermieden wird; überzählige Emitter sind zweckmäßig auf High zu legen ). 5HNA96 Wien am 07.11.1995 ****************** 1.EDT Referat LogilGamilien br·rh"R ~Tb~- _t-" +UI 16V v r L-h~ I~M t· Y T1 ~P 12 I u~1 ~n I Michael Hacker Seite~ Y bl ·i OS-~U-~ iv C) I' 14 Pio-DIP Während der Umschaltzeit sind kurze Zeit( etwa IOns ) Transistor T3 und T4 gleichzeitig leitend, so daß in dieser Übergangszeit ein unvermeidlich großer Strom über beide Transistoren ( cwrent spike ) nießt, dessen Größenordnung einige mA sein kann; bei gleichzeitigem Umschalten mehrerer Gatter können die Stromspitzen zu einem Einbn~ch der Versorgungsspannwng führen. Abhilfe schaffen Schutzkondensatoren zwischen U+ wnd Masse. Die Diode in der Emitterleitung des Transistors T3 sorgt jedoch danach für ein sicheres sperren dieses Transistors. Sie vergrößert praktisch die Eingangsschwellspannung, indem sie sein Emitterpotential um ca 0,6V anhebt. Diese Funktion führt zu den typischen Übertragungskennlinien wie im Bild b auf dieser Seite, die für zwei verschiedene Belash~ngen und eine Temperatur Tu = 25"C dargestellt sind. Es handelt sich um mittlere Kennlinien innerhalb eines gewissen Streubandes, gemessen bei der normalen Betriebsspannung von 5V. Als Belastung sind TTL Grundschaltungen zugrunde gelegt, die den gleichen Eingang haben wie das Gatter selbst. Von diesem muß der auf L Potential befindliche Ausgang jeweils emen Strom von etwa I,lmA ( max 1,6mA ) aufnehmen. Der auf High Potential liegende Ausgang dagegen braucht nur einen Strom von jeweils 20CLA, in die umgekehrte Richtung zu liefern. Über die Kennlinien sind die, für alle TTL Gatter zulässigen Bereiche für den Eingangspegel angegeben, die mit Rücksicht auf einen eindeutigen Ausgangszustand genügend Abstand von der Schaltspannung Ut ca. 1,5V garantieren. Der dazwischen liegende Übergangsbereich umfaßt auch temperaturbedingte Kennlinienschwankungen und gilt als verbotene Zone. Er ist beim Umschalten eines Gatters möglichst schnell zu durchlaufen. Die Ansteuerflanke sollte kürzer als I~s sein, da innerhalb des Übergangsbereiches eine gewisse Schwingneigung besteht. Das Bild c zeigt ein vierfach NAND Gatter im DIL Gehäuse. Die darunterstehende Spalte gibt eine Übersicht über die Kenndaten. Kombiniert man zwei Nand Gatter (siehe Bild a ) bei gleichzeitiger Einsparung einer Ausgangsstufe so erhält man die invertierende UND ODER Schaltung wenn man nur jeweils einen Emitter der Eingangstransistoren T11 und T12 venvendet. Die mit dieser Schaltung realisierte UND ODER NICHT Funktion Iäßt sich durch die diskrete Schaltung ( WIRED AND ) nach Bild b realisieren. 5HNA96 Wien am 07.11.1995 ********************* SeitelO 1.EDTReferat Logikfamilien .. PuU-up-WldrCl~nd" ·u, Michacl Hacker * nmoal*d m ~S rtl NANWIW I I nJc a«mm mkomnm I~nn I · \I'L~" KDI~IOIA~ Wl~l~orAl Bild 2 Inwtrtisrende UNDODER-Çchaltungen (UND-ODER-NICHTSchaItungen) s) slr monolithi~her Barsteln·). b) alr Wired·AND-Sd~alNng·· ) Diese ist jedoch nur möglich bei TTL Schaltungen mit offenem Kollektorausgang, die mit einem gemeinsamen PULL UP Widerstand zusammengeschaltet werden können. Eme Zusammenschaltung der Ausgänge von Gegentakt-Ausgangstufen ( Totem Pole Schaltung w~ire nicht möglich, da in diesem Fall hohe Kurzschlußströme über die gleichzeitig leitenden Transistoren T3 und T4 verschiedener Gatter auftreten können. Die Zusammenschaltung von Gattern mit Gegentaktausgang nach Art der Wired AND Schaltung ist möglich, wenn die Ausgangstranslstoren über einen zusätzlichen Sperreingang gleichzeitig gesperrt werden können. Siehe unten. slgnac Si0"01- L Ekg~ng LH LLH HIH HIL SprcI LI· dLI~DIII P1ILuu A bat~bfr Ehpanp b.n C~, ~ I CwlllJI ·M(rrrr o~ ~L d* nn~b~ ~ob) CPII I VPY VIY· I Scblr~r ·i~ Stros YIM obr o) -2 b) ·d·lr·L Bild 3 ~ll-TRI-STATESctreltunQ a) Sc~ltung, b) Funktionnebelle Wegen des dritten moglichen Schaltzustandes spricht man von einer TRI STATE Logik. Bei einer Verbindung mehrerer Ausgänge derartiger Schaltungen darf nur j eweils ein Ausgang ~-eigegeben werden, der dann das Potential aller anderen bestimmt. Die Sperrfähigkat des Ausgangs ist von grundsätzlicher Bedeutung bei Sammelleitungen ( I2 C BUS ), wobei mehrere Gatter eine gemeinsame Ausgangsleitung( Datenbus) benutzen. 2.1 Low Power TTL ( L- TTL ): Die Bezeichnung Low Power bedeutet kleine Leistung. Diese Gatter nehmen nur etwa 1/10 des Strohmes von Standart TTL Gattem auf. Man erreicht die genngere Leistungsaufnahme durch Vergrößerung der Widerstände (Werte ca. 5HNA9h Wien am 07.11.1995 Michael Hacker ******************* 1.EDT Referat Logikfamilien Seite 11 10 mal so groß ) im inneren der Schaltung, ansonsten unterscheidet sich der Innenaufbau nicht. Ein LTTL Gatter benötigt etwa ImW. Die Schaltzeiten eines TTL Gatters hängen hauptsächlich von den Ladungs und Entladungs - Vorgängen der Transistor Kapazitäten ab => LTTL ist langsamer als TTL da bei LTTL Gatter die Ladung bzw. Entladung über größere Widerstände gemacht wird (langsamer als bei kleinen Widerständen ). 2.2 Hicrh Speed TTL(H -TTL ): High Speed TTL Gatter haben kwze Schaltzeiten. Der Aufbau entspricht dem der Standar TTL Serie. Verändert wurden die Widerstandswerte in den Stromkreisen. Geringer Widerstand => schnelles Laden und Entladen der Transistor Kapazitäten => hohe Strom Aufnahme ca. 2 mal sovlel wie Standart TTL. H TTL Gatter schalten ungef~ir 2 mal so schnell wie Standart TTL Gatter aber die Leistungsaufnahme ist mehr als 2 mal so groß wie bei Standart TTL Glieder. 2.3 Schottkv TTL ( S - TTL ): Um kürzere Schaltzeiten zu erreichen entwickelte man die Schottky TTL Schalh~ngen. Dabei handelt es sich um sogenannte ungesättigte Logikschaltungen, bei denen die einzelnen Transistoren nicht bis in die Sättigung hinein aufgesteuert werden, um die dadurch bedingten Verzögerungszeiten zu vermeiden. Bei der Schottky TTL Technik wird dies durch den Einsatz von Schottky Transistoren erreicht. Diese Sonderform des Transistors erhält man ( Bild 1) durch Kombination eines herkömmlichen Bipolartransistors mit einer Schottky Diode. Diese Diode entsteht ( Bild a) durch den Kontakt eines Metalls mit n dotierten Silizium bestimmter Leitfähigkeit. 'li o.,v r·lckmUY~-Y--eJIcholll·ich·. rr·toll 8iId 1 Sclro(rky-TTL·Technik a) Schottky-Diode, b) SChottky-Transistor, c) Schottky-NAND-Galter 5HNA96 Wien am 07. 11.1995 ***************** 1.EDT Referat Logikfamilien Michael Hacker Seite 12 Der Strom durch eine Schottky Diode wird nur durch MaJoritätsträger, nur durch Elektronen gebildet. Der Ubergang vom Durchlaßzustand in den Sperrzustand erfolgt sehr rasch, da keine Minoritätsträger ausgeräumt werden müssen. Das Schalten in den Durchlaßzustand erfordert ebenfalls wenig Zeit, da die Sperrschicht sehr schnell abgebaut ist, da praktisch keine Ladungsspeicherung auftntt. Die Schottky Diode gilt daher als extrem schnelle Schaltdiode ( typisch 100ps ). Durch Überlappung des Basisanschlusses aus Aluminium mit der Kollektorzone läßt sich die Schottky Diode unmittelbar in ernem NPN Transistor integrieren. Sie wirkt dann als Klemmdiode zwischen Basis und Kollektor ( Antisättigungsdiode ). Der Transistor( Schaltwng b )kann nur soweit zusteuem bis UCE aUf etwa 0,4V abgesunken ist, dann verhindert die Schottky Diode ein weiteres Durchsteuem. Sie wird bei der geringen Flußspannung von 0,3 ... 0,4V leitend. Vom Basisanschluß nießt ein Strom über die Schottky Diode und die Kollektor Emitter Strecke des Transistors zw Masse. Dieser Strom steht als B asi s strom nicht mehr zur Verfügung. D er Anfang de s Üb ersteuerungsb erei che s eines Transistors wird erreicht, wenn UCE aWf etwa 0,4V abgesunken ist. Bei UCE = 0,4V ist der Transistor schon leicht in den Übersteuen~ngsbereich hineingesteuert worden. Diese Übersteuerung ist allerdings sehr schwach. Nachteile der alten S - TTL Familie ist der hohe Stromverbrach und die große Verlustleistung. Für alle TTL Familien gilt die einheitliche Betriebsspannung von 5V, sowie Pin und Funktionskompalität bei Schaltungen gleichen Typs. S(nL-Stra (I,,) ~urc·-ltro~ (I~) I ~P~· "" 1o rrn-ar~ Y) · laJ 1, 1, 1·rtap·runrrl·cr I *~ ~, Icrlultl·(rtunp b·( 1IIHt (clp(.rhc v~rt~ pro Clltrr) ZO ~0 1~ 20 ~D~\\\\\\\\\\\~L\V\YI 10 *LS )0 1D Q 1Dm* 1I IL >) bl ~O r· r Bild 2 Eigenxhaften der Schottky-Familien 5HNA96 *************** 1.EDT Referat Wien am 07.11.1995 Logikfamilien Michael Hacker Seite 13 Das Bild a g~bt die zulässige Strombelastung für normale Gegentakt - Ausgänge an z.B. 20mA als Sinkstrom I,, und ImA als Source Strom I,b bei der S - Familie. Bei dieser Belastung bleiben die zugehörigen Ausgangspegel Low und High noch ungestört. Die absuluten Werte liegen höher. 3.ECL Log;ik Die Bezeichnung ECL ist die Akürzung für Emitter Coupled Logik, auf Deutsch stromgesteuerte Logik. Die ECL Schaltungen sind als integrierte Schaltungen mit bipolaren Transistoren aufgebaut. Damit man eine ungesättigte Logikschaltung erreicht wird bei dieser Technik das Prinzip Stromumschalters mit Emitterkopplung( Bild a) angewndt. Die G~undschaltung hat zwei Eingänge wie ein Differenzverst~irker, wobei ein Eingang auf ein fixes Potential zwische +U~ und -Ug gelegt wird. Durch den Widerstand RE wird der Summenstrom für das emittergekoppelte Transistorpar so begrenzt, daß eine Sättigung bei normaler Ansteuerung ausgeschlossen wird. Liegt der Eingang E gegenüber dem Referenzeingang auf einem genügend tiefen Potential, so ist der Transistor T1 gespen2, Strom nießt nw über den Transistor T2. Schaltet man dagegen den Eingang E auf ein höheres Potential, so übernimmt der Transistor T1 den Strom, währen T2 spent. ·uo Rc E (e Clrr~cuy T~ I r 1 ~ LMc·rl~gn ~hl -*~n·arg rl I r~ j" E1 EI E, ~rn -~u·gonp r13 r12 111 T1 ~l:-U.jS~ u~*~··i~* oi L·-155V Bild 3 ECL-Technik (Emitter Coupled _Logic) a) Stromumsct~slter, b) ECL-Gettsrrc~8l1ung Den Aufbau eines ECL Gatters zeigt Bild b. Die eingeführten Systeme nach dieser Schaltungsart arbeiten mit einer negativen Betriebsspannung UB=-5,2V und den angegebenen Pegelwerten. Wenn man am Eingang El oder E2 oder E3 ein High Potential erhält wird der betreffende Transistor leitend, T2 dagegen spent. Am Ausgang Al stellt sich dann ein High Potential und am Ausgang A2 ein Low Potential ein. Die beiden Emitterfolger sorgen dafür, daß ein niederohmiger belastungsfähiger Ausgang gebildet wird. Anderseits ergeben sich in Verbmdung mit ihrer Basis - Emitterspannungen ( 0,6 ... 0,7V ), die richtigen Pegelwerte am Ausgang. 5HNA96 Wien am 07.11.1995 Michael Hacker ******************** 1.EDT Referat Logikfamilien Seite 14 OPEN-COLLECTOR Bausteine: Mitunter tritt das Problem auf, daß man die Ausgänge sehr vieler Gatter logisch verknüpfen muß oder eine höhere Spannung am Gatterausgang benötigt. Bausteine mit open collector besitzen als Ausgangsstufe lediglich einen npnTransistor, dessen Emitter an Masse liegt. Solche Ausgänge kann man im Gegensatz zu den sonst venvendeten Gegentaktendstufen ohne weiteres parallel Schalten und mit einem gemeinsamen Kollektonviderstand versehen. Das Ausgangspotential geht nur dann in den H-Zustand, wenn alle Ausgänge im H-Zustand sind. In positiver Logik ergibt sich demnach eine UND-Verknüpfung. Andererseits erkennt man, daß die Ausgangsspannung dann in den L-Zustand geht, wenn einer oder mehrere der Ausgänge in den L-Zustand gehen. In negativer Logik erg~bt sich demnach eine ODER-Verknüpfung. Da die Verknüpfung dwrch die äußere Verdrahtung erreicht wird, spricht man von WIRED-AND bzw. WIRED-OR Verknüpfung. r·-·--fi 'T77 I ic, i(j, ~ i (G? ··· 1· P L._. "i i ._ Ij i Abb. 3.2X L~gic~che VcrknüpTunE von Gatter-Ausfiinfen mjt orrcnem Kollel;lor Open Collector Ausgänge können auch als Treiber venvendet werden. Bestimmte TTL-Bausteine können mit dem Open Collector höhere Spannungen als 5V schalten. Der Open Collector Baustein ist am Aussterben, da er zusehends durch Transistorarrays, welche an die Ausgänge von normalen Gattern geschalten werden können, ersetzt wird. Da Transistorarrays in größerer Stückzahl produziert werden, ist es billiger, ein normales Gatter (ohne open collector) und ein zusätzliches Transistorarray zu venvenden, als einen Open Collector Baustein . 5HNA96 Wien am 07.11.1995 Michael Hacker