Predictive Gate Drive - All

Werbung

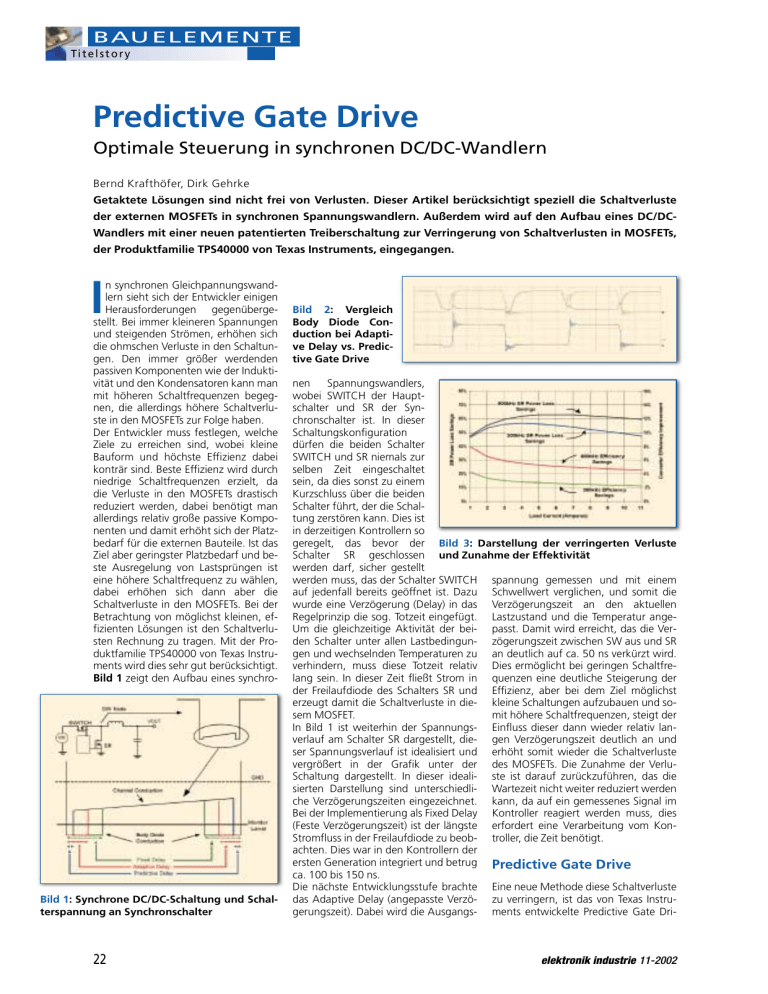

BAU ELEMENTE Ti t e l s t o r y Predictive Gate Drive Optimale Steuerung in synchronen DC/DC-Wandlern Bernd Krafthöfer, Dirk Gehrke Getaktete Lösungen sind nicht frei von Verlusten. Dieser Artikel berücksichtigt speziell die Schaltverluste der externen MOSFETs in synchronen Spannungswandlern. Außerdem wird auf den Aufbau eines DC/DCWandlers mit einer neuen patentierten Treiberschaltung zur Verringerung von Schaltverlusten in MOSFETs, der Produktfamilie TPS40000 von Texas Instruments, eingegangen. I n synchronen Gleichpannungswandlern sieht sich der Entwickler einigen Herausforderungen gegenübergestellt. Bei immer kleineren Spannungen und steigenden Strömen, erhöhen sich die ohmschen Verluste in den Schaltungen. Den immer größer werdenden passiven Komponenten wie der Induktivität und den Kondensatoren kann man mit höheren Schaltfrequenzen begegnen, die allerdings höhere Schaltverluste in den MOSFETs zur Folge haben. Der Entwickler muss festlegen, welche Ziele zu erreichen sind, wobei kleine Bauform und höchste Effizienz dabei konträr sind. Beste Effizienz wird durch niedrige Schaltfrequenzen erzielt, da die Verluste in den MOSFETs drastisch reduziert werden, dabei benötigt man allerdings relativ große passive Komponenten und damit erhöht sich der Platzbedarf für die externen Bauteile. Ist das Ziel aber geringster Platzbedarf und beste Ausregelung von Lastsprüngen ist eine höhere Schaltfrequenz zu wählen, dabei erhöhen sich dann aber die Schaltverluste in den MOSFETs. Bei der Betrachtung von möglichst kleinen, effizienten Lösungen ist den Schaltverlusten Rechnung zu tragen. Mit der Produktfamilie TPS40000 von Texas Instruments wird dies sehr gut berücksichtigt. Bild 1 zeigt den Aufbau eines synchro- Bild 1: Synchrone DC/DC-Schaltung und Schalterspannung an Synchronschalter 22 Bild 2: Vergleich Body Diode Conduction bei Adaptive Delay vs. Predictive Gate Drive nen Spannungswandlers, wobei SWITCH der Hauptschalter und SR der Synchronschalter ist. In dieser Schaltungskonfiguration dürfen die beiden Schalter SWITCH und SR niemals zur selben Zeit eingeschaltet sein, da dies sonst zu einem Kurzschluss über die beiden Schalter führt, der die Schaltung zerstören kann. Dies ist in derzeitigen Kontrollern so geregelt, das bevor der Bild 3: Darstellung der verringerten Verluste Schalter SR geschlossen und Zunahme der Effektivität werden darf, sicher gestellt werden muss, das der Schalter SWITCH spannung gemessen und mit einem auf jedenfall bereits geöffnet ist. Dazu Schwellwert verglichen, und somit die wurde eine Verzögerung (Delay) in das Verzögerungszeit an den aktuellen Regelprinzip die sog. Totzeit eingefügt. Lastzustand und die Temperatur angeUm die gleichzeitige Aktivität der bei- passt. Damit wird erreicht, das die Verden Schalter unter allen Lastbedingun- zögerungszeit zwischen SW aus und SR gen und wechselnden Temperaturen zu an deutlich auf ca. 50 ns verkürzt wird. verhindern, muss diese Totzeit relativ Dies ermöglicht bei geringen Schaltfrelang sein. In dieser Zeit fließt Strom in quenzen eine deutliche Steigerung der der Freilaufdiode des Schalters SR und Effizienz, aber bei dem Ziel möglichst erzeugt damit die Schaltverluste in die- kleine Schaltungen aufzubauen und sosem MOSFET. mit höhere Schaltfrequenzen, steigt der In Bild 1 ist weiterhin der Spannungs- Einfluss dieser dann wieder relativ lanverlauf am Schalter SR dargestellt, die- gen Verzögerungszeit deutlich an und ser Spannungsverlauf ist idealisiert und erhöht somit wieder die Schaltverluste vergrößert in der Grafik unter der des MOSFETs. Die Zunahme der VerluSchaltung dargestellt. In dieser ideali- ste ist darauf zurückzuführen, das die sierten Darstellung sind unterschiedli- Wartezeit nicht weiter reduziert werden che Verzögerungszeiten eingezeichnet. kann, da auf ein gemessenes Signal im Bei der Implementierung als Fixed Delay Kontroller reagiert werden muss, dies (Feste Verzögerungszeit) ist der längste erfordert eine Verarbeitung vom KonStromfluss in der Freilaufdiode zu beob- troller, die Zeit benötigt. achten. Dies war in den Kontrollern der ersten Generation integriert und betrug Predictive Gate Drive ca. 100 bis 150 ns. Die nächste Entwicklungsstufe brachte Eine neue Methode diese Schaltverluste das Adaptive Delay (angepasste Verzö- zu verringern, ist das von Texas Instrugerungszeit). Dabei wird die Ausgangs- ments entwickelte Predictive Gate Dri- elektronik industrie 11-2002 BAU ELEMENTE Ti t e l s t o r y ve. Hierbei wird der Spannungsabfall an der Freilaufdiode des Schalters SR gemessen. Wird hier festgestellt das der Strom durch die Freilaufdiode des MOSFETs fliesst, wird die Wartezeit für den nächsten Schaltzyklus verringert und umgekehrt. Damit wird den Schaltverlusten in der Freilaufdiode aktiv entgegen gesteuert. Durch diese Technik, wird, wie in Bild 2 im rechten Abschnitt zu sehen ist, der Stromfluss durch die Freilaufdiode nahezu komplett verhindert. In dem linken Teil des Bildes 2 ist das bereits verbesserte Adaptive Delay gegen das optimierte Predictive Gate Drive mit den Spannungsverläufen dargestellt. Bild 3 zeigt wie sich diese neue Treibertechnik positiv auf die Effizienz und Schaltverluste im Schalter SR über eine weiten Strombereich und im Vergleich bei einer Schaltfrequenz von 300 kHz und 600 kHz auswirken. Die beiden oberen Kurven zeigen um wie viel sich die Verluste im Schalter SR verringert haben. Dabei sind die Verbesserungen bei der höheren Schaltfrequenz (600 kHz), ca. 60% im Vergleich zu immer noch beachtlichen 50% (300 kHz), mehr ausgeprägt, da wie vorher beschrieben hierbei die Verluste ohne Predictive Gate Drive größer wären. Die beiden unteren Kurven stellen die Verbesserung der Gesamteffizienz der Schaltung dar. Dies ist auch wieder bei der höheren Schaltfrequenz von 600 kHz am deutlichsten mit 4%. Ein wesentlicher Punkt ist aber die geringere Belastung der MOSFETs. Durch die Verringerung der Schaltverluste in den MOSFETs sind auch die Wärmeverluste deutlich kleiner. Dem im Bild 4 zugrundeliegendem Versuch wurden zwei Schaltungen mit den selben externen Komponenten und Kontrollern, sowie gleicher Belastung und Umgebungsbedingungen verglichen. In der linken Schaltung wurde das bereits verbesserte Adaptive Delay verwendet und in der rechten Schaltung das Predictive Gate Drive. Das Bild 4 zeigt bei Verwendung des Predictive Gate Drive eine Verringerung der Wärmeverluste um ca. 21 °C. Dies führt zu geringerer Aufheizung der Schaltung und verbesserter Zuverlässigkeit, da der Stress auf den externen MOSFETs deutlich verringert wird. Mit dem Predictive Gate Drive steht dem Entwickler aber auch die Möglichkeit offen kleinere und damit günstigere MOSFETs zu verwenden, dabei verliert er dann aber diesen Wärmevorteil und Verbesserung der Effektivität. Beispielrechnung Für einen Point-of-Load-Schaltwandler, der z.B. aus einem 3,3-V- oder 5-V-Bus elektronik industrie 11-2002 Bild 4: Vergleich Wärmeverluste Adaptive Delay vs. Predictive Gate Drive Bild 5: Der Schaltplan der Gesamtschaltung. Die blau eingefärbten Bauteile sind für die Kompensation zuständig. gespeist wird, soll eine Ausgangsspannung von 2,5 V mit bis zu 10 A realisiert werden. Die Ausgangsspannungswelligkeit soll in diesem Fall <2% sein. Eine hohe Effizienz steht hier im Vordergrund, um die Schaltverluste gering zu halten und somit die Eigenerwärmung zu reduzieren. gangsstrom von 10 A einem IRIPPLE von 4 A entspricht. Externe Komponenten Aus Gleichung [1] errechnet sich ein Induktivitätswert von 1 µH. Sollte das Ergebnis ein krummer Wert sein, so sollte immer der nächst niedrigere Standardwert gewählt werden. Bei den Standardtypen sollte auf eine kleine Bauform geachtet werden. In der Regel haben kleinere Bauformen einen geringeren Serienwiderstand. Dies trifft auch auf die Spule von Vishay zu, die mit einem Standardwert von 1 µH verfügbar ist und einen Serienwiderstand von 35 mΩ aufweist. Dies bedeutet bei einem max. Ausgangsstrom von 10 A eine Spulenverlustleistung von 0,35 W. Bei einer max. Ausgangsleistung von 25 W betragen hierbei die Spulenverluste nur 1,4%. Ein weiterer Vorteil ist ihre voll geschirmte Bauart. Als nächstes wird der benötigte Minimalwert des Eingangskondensators ermittelt. Der Eingangskondensator muss der maximalen Stromwelligkeit und der max. Eingangsspannungswelligkeit genügen. In der Realität ist oft der Point-of-Load-Wandler einem DC/DCWandler nachgeschaltet. Dieser erste Schaltwandler ist i.d.R. mit genügend Vor der Auswahl der Komponenten muss die Schaltfrequenz für den Schaltwandlerbetrieb festgelegt werden. In diesem Fall kommt der TPS40001 zum Einsatz, dessen Schaltfrequenz bei 300 kHz liegt. Bei Bedarf könnte auch ein TPS40003 zum Einsatz kommen, der mit einer Schaltfrequenz von 600 kHz arbeitet. Die höhere Schaltfrequenz hätte den Vorteil, dass die Spule kleiner dimensioniert und eine Platzeinsparung realisiert werden könnte. Der TPS40001 arbeitet im CCM (Continuous Current Mode), was bedeutet, dass die Synchrongleichrichtung auch ohne Last aktiv ist und somit als Stromsenke agiert. Bei der Dimensionierung der Bauteile beginnt man der Einfachheit halber mit der Spule. Als Berechnungsgrundlage zur Bestimmung der Induktivität muss man den maximalen Wert der Stromwelligkeit festlegen. In diesem Beispiel wurde dieser auf 40% des maximalen Ausgangsstroms festgelegt, was bei einem maximalen Aus- [1] 23 BAU ELEMENTE Ti t e l s t o r y großer Ausgangskapazität ausgestattet, um der Eingangsspannungswelligkeit und Stromwelligkeitsansprüchen zu genügen. In diesem Beispiel handelt es sich um ein Referenzboard, um im Labor Messungen vornehmen zu können. Daher wird hier auch die benötigte Eingangskapazität berechnet. Für die Ausgangsleistung von 25 W ist eine Eingangsspannungswelligkeit von 150 mV ein realistischer Wert. Die hierzu minimal erforderliche Kapazität lässt sich nach Gleichung [2] berechnen. Der Wert ∆t entspricht dem Einschaltzeitraum des Highside-FET bei minimaler Eingangsspannung. Des weiteren wird die Stromwelligkeit berechnet, mit der der Eingangskondensator beaufschlagt wird. Bedingt durch das breite Puls-Pausenverhältnis entsteht eine Stromwelligkeit, die nahezu der des Ausgangsstromes entspricht. Die Stromwelligkeit entspricht im Beispiel einem sägezahnähnlichen Verlauf. Mit Gleichung [3] errechnet sich hieraus eine Stromwelligkeit von 9,1 A. Die errechneten 9,1 A entsprechen nicht hundertprozentig der Realität, sind jedoch für die Betrachtung exakt genug. Um nun einen Kondensator mit der erforderlichen Kapazität und der benötigten Stromwelligkeit zu realisieren, wird nach einer preisgünstigen Realisation gesucht. Hierzu werden drei 22 µF Keramikkondensatoren vom Typ [2] [3] X5R parallelgeschaltet. Jeder der Kondensatoren kann mit einer maximalen Stromwelligkeit von je 2 A beaufschlagt werden. Um nun dem Ziel von 9,1 A zu entsprechen, werden noch zwei 330 µF POSCAPS-Kondensatoren nachgeschaltet, die je mit einer Stromwelligkeit von 4,4 A beaufschlagt werden können. In der Praxis würden die beiden POSCAPKapazitäten entfallen, da die vorgeregelte Spannung in der Regel ausreichend genug gesiebt und stabilisiert ist. Die Auswahl des Ausgangskondensators basiert auf verschiedenen Auswahlkriterien wie Funktion, Verfügbarkeit, Größe und Kosten. Als erstes wird die minimal benötigte Ausgangskapazität mit Hilfe der maximal zulässigen Spulenstromwelligkeit und der Hälfte der maximalen Ausgangsspannungswelligkeit berechnet. Das Ergebnis aus Gleichung [4] spiegelt die benötigte Kapazität wieder, um die Ausgangsspannungswelligkeit zu realisieren. Zusätzlich muss der ESR des Kondensators berechnet werden. [5] Um diesen geringen Wert zu realisieren und dennoch die Kosten und den Platzbedarf nicht aus den Augen zu verlieren, wurden ein 470 µF POSCAP und zwei 22 µF Keramikkondensatoren eingesetzt. Für die Auswahl der MOSFETs wurden SO8-Typen mit geringer Gateladung von nur 30 nC gewählt. Auch der Einschaltwiderstandswert liegt bei einem Wert von nur 8 mΩ. Dies ist wichtig, da bedingt durch den geringen Spannungsunterschied zwischen Eingangsund Ausgangsspannung die Einschaltperiode des Highside-FET recht lang ausfällt. Ein Highside-FET mit geringem RDS(on) kann dazu beitragen, die Verluste im eingeschalteten Zustand zu reduzieren. Der gleiche N-Kanal MOSFET wird auch für den Synchrongleichrichter verwendet. Kurzschlussschutz Der Kurzschlussschutz besteht in erster Linie darin, den Controller abzuschalten, falls ein wesentlich größerer Strom als vom Anwender zugelassen fließt. Die interne Schaltung funktioniert folgendermaßen: Eine 15 mA Stromsenke ist intern mit dem ILIM-Pin verbunden und verursacht an dem daran angeschlossenen Widerstand einen Spannungsabfall. Dieser Spannungswert wird mit der im eingeschalteten Zustand über dem RDS(on) des Highside-FET abfallenden Spannung verglichen. Diese Messmethode wird auch als „cycle by cycle current limit“ bezeichnet. Wenn dieser Wert nun größer oder gleich der am Widerstand abfallenden Spannung ist und für sieben aufeinan- [4] [5] [6] [7] [8] 24 derfolgende Schaltzyklen besteht, so wird dies als Überstrombedingung erkannt und dadurch die MOSFET-Treiber deaktiviert. Die Zeitspanne bis zu einem Neustart wird durch den Sanftstartkondensatorwert bestimmt. Sechs Sanftstartkondensatorzeitspannen müssen verstreichen, bevor beim siebten Ladevorgang die zuvor verriegelten Treiberausgänge wieder freigegeben werden. Da die interne Stromquelle und der gewählte externe Widerstand mit Toleranzen behaftet sind und zudem der externe Highside-FET über die Temperatur seinen RDS(on) ändert, kann dieser Schutz nur als Kurzschlussschutz betrachtet werden. Der Widerstand sollte so berechnet werden, dass er dem Zweifachen des maximalen Ausgangsstromes entspricht. Kompensationsnetz Für den Frequenzgang eines Pulsbreitenmodulators mit Synchrongleichrichtung sind drei Parameter ausschlaggebend: Die Induktivität der Filterspule, die in dieser Rechnung als verlustfrei betrachtet wird, die Ausgangskapazität, die sich in diesem Beispiel aus einer Parallelschaltung von Kapazitäten zusammensetzt, und der daraus resultierende Gesamtwiderstand (ESR), der sich aus den drei parallel geschalteten ESR-Werten zusammensetzt. Um nun eine stabile Ausregelung bei Lastsprüngen zu gewährleisten, wird mit Hilfe des Kompensationsnetzwerks über die Spannungsgegenkopplungsschleife ein stabiler Regelkreis realisiert. Bild 5 zeigt in blau eingefärbt die für die Kompensation verantwortlichen passiven Bauteile. Die Ausgangsspannung wird hier über den Spannungsteiler bestehend aus R13 und R14 mit der internen Referenzspannung verglichen und auf den mit dem Spannungsteiler programmierten Wert mit Hilfe des PWM-Signals auf die 2,5 V ausgeregelt. Der PWM-Komparator vergleicht die Ausgangsspannung am FB-Pin des Regelverstärkers mit der Sägezahnspannung des Oszillators und bewirkt über die Ausgangstreiberstufen und Ansteuerung der externen Leistungs-FETs eine Pulsbreitenmodulation. Der Ausgangstiefpassfilter, bestehend aus L2, und der Kondensatorbank, bestehend aus C19, C20 und C24, glätten das PWM-Signal zu der Ausgangsspannung von 2,5 V. Als Übertragungsfunktion des Modulators gilt die Kleinsignal-Übertragungsfunktion VOUT/VFB. Diese Übertagungsfunktion setzt sich zusammen aus einem statischen Verstärkungsfaktor VIN/VOSC und der Filterfunktion des Ausgangsfilters. Der Ausgangsfilter weist eine Doppelpolstelle bei der Frequenz FLC und ei- elektronik industrie 11-2002 ne einfache Nullstelle bei der Frequenz FESR auf. Die Doppelpolstelle und die ESR-Nullstelle können nach den Gleichungen [6] und [7] bestimmt werden. Das Kompensationsnetz besteht aus dem Regelverstärker, der im TPS4000x integriert ist und dem Impedanznetzwerk. Das Impedanznetzwerk kann in zwei Teile aufgegliedert werden. Da wäre zunächst das Eingangsnetzwerk ZIN, bestehend aus R14, C15 und R12, und das Rückführungsnetzwerk ZFB, bestehend aus C21, C22 und R16. Dieses Netzwerk sorgt dafür, dass bei einer möglichst hohen Frequenz beim Schneiden der 0-dB-Linie der Phasenrand des Regelkreises zum stabilen Arbeiten ausreicht. Die Gleichungen drei bis sechs definieren die Pole und Nullstellen des Kompensationsnetzwerkes. Das hier eingebundene Kompensationsnetzwerk wird als Kompensationsnetzwerk Typ III bezeichnet und weist zwei Nullstellen und drei Polstellen auf. Die erste Polstelle wird nahe an den Anfang gelegt, um die Gleichspannungsregelung zu verbessern. Die Polstelle wurde hier bei 5,7 kHz festgelegt. [8] Die zweite Nullstelle wird kurz vor der 7 kHz Nullstelle des LC-Filters bei ca. 6,2 kHz platziert. derstand RDS(on) aufweisen. Durch die hohen Änderungsgeschwindigkeiten der Ströme in den einzelnen Bauteilen entstehen über die Leiterbahnimpedanzen und parasitären Schaltkreiselemente unter Umständen hohe Spannungsspitzen oder gar rasch abklingende Einschwingvorgänge. Ein gut ausgearbeitetes Layout und die zielgerichtete Anordnung der Bauteile tragen zu einem einwandfrei arbeitenden Schaltwandler maßgeblich bei. Die in diesem Zusammenhang kritischsten Bauteile sind die MOSFETs, da sie zum einen hohe Energieniveaus schalten und somit große Störsignale erzeugen können. Zum zweiten sind die Eingänge des Regelkreises sehr empfindlich auf Störungen, da hier kleine Änderungen verstärkt und in die Regelung miteinbezogen werden. Auch Störungen, die über die Versorgungsspannung an den Controller eingekoppelt werden, können die interne Regelung negativ beeinflussen. Um Fehlschläge beim Layout zu vermeiden, sollte mit dem Platzieren des Controllers und der Schaltelemente (MOSFETs) begonnen werden. Nachdem der Controller platziert wurde, ist es sinn- [9] Die erste Polstelle wird nahe der Nullstelle FESR platziert. voll die Eingangsentkoppelkondensatoren nahe an den MOSFETs zu platzieren. [10] Die zweite Polstelle wird bei der halben Schaltfrequenz platziert. [11] Nachdem der Spannungsteiler bestehend aus R14 und R13 dimensioniert wurde, wird der Verstärkungsfaktor durch das Teilverhältnis von R16 zu R14 festgelegt. Layout Die beim TPS4000x eingesetzten externen MOSFETs schalten sehr schnell und effizient, da sie eine geringe Gatekapazität QG und einen geringen Schaltwi- elektronik industrie 11-2002 Dabei sollen die Leiterbahnen so ausgelegt werden, dass der Eingangsstrom an den Kondensatoren vorbeifließen muss, bevor er auf die MOSFETs trifft. Das Gleiche gilt für die Platzierung der Spule und der Ausgangskondensatoren. Ein im Layout vorgegebener Pfad ist hier von äußerster Wichtigkeit. Texas Instruments 705 Bernd Krafthöfer ist Market Development Engineer und Dirk Gehrke, Field Application Engineer Power Management Products High Performance Analog bei Texas Instruments in Freising 25