05 projekte mit assembler geloest

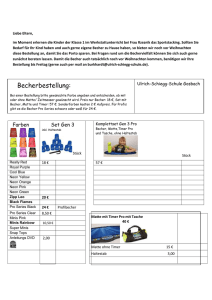

Werbung

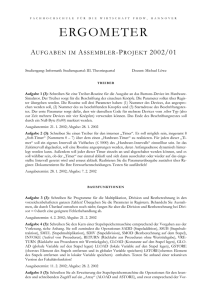

5 Projekte mit Assembler gelöst Mikrocomputertechnik 1 Stand November 2007 Herzlich Willkommen Jürgen Walter Prof. J. Walter Mikrocomputertechnik 2 Stand November 2007 Projekt verwendete Einheiten 1. Blinklicht mit Blinkfrequenz Timer 0,1 Interrupt 2. A/D-Wandlung A/D-Wandler 3. Serielle Schnittstelle Serielle Schnittstelle 4. Effektivwertmessung Timer, A/D-Wandler, Serielle Schnittst. Prof. J. Walter Mikrocomputertechnik 5 Projekte mit Assembler gelöst Tabelle 5.1 Die verwendeten Einheiten in den Projekten 3 Stand November 2007 Nur dokumentierte Hardware und Software ist existent. Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Regel 1 4 Stand November 2007 Durchgängige Verwendung von Registern mit Herstellung des Ausgangszustands. Zuordnung von Tasks (Aufgaben - Prozesse) zu Registerbänken. Prof. J. Walter Mikrocomputertechnik 5 Projekte mit Assembler gelöst Regel 2 5 Projekte mit Assembler gelöst Mikrocomputertechnik 5 Hochsprache C / C++ verwenden. Stand November 2007 Bei umfangreicher Software unbedingt Prof. J. Walter Regel 3 $nomod51 Standardkopf ;der Modus fuer 8051 wird abgeschaltet $debug $nolist ;es wird kein Listing fuer reg535 erstellt $include(reg535.pdf) ;die 80535-spezifischen Daten $list ;es wird ein Listing erstellt $title () ;bitte ausfüllen ;--------------------------------------------------------------------;Programmbeschreibung ;Programm: ;Programmiert: Stand November 2007 ;Datum: Teamarbeiter 1 ; ;Verwendete Einspruenge: keine ;Verwendete Unterprogramme: keine ; ;Verwendete Register und Variable: ;Registerbank(0) ; ;Kommentar: ;Aenderungen: ;Datum: ;-----------------------------------------------------------------------;Initialisierungsteil fuer allgemeine Konstanten ;-----------------------------------------------------------------------CSEG AT 0H ;Legt absolute Codesegmentadresse auf 0h jmp INIT ;Sprung auf Initialisierungsroutine ;-----------------------------------------------------------------------;Interrupt-Vektoren ;-----------------------------------------------------------------------; ;-----------------------------------------------------------------------;Initialisierungsteil fuer On-Chip Peripherie ;-----------------------------------------------------------------------ORG 100H ;Programmstart bei 100H INIT: ;-----------------------------------------------------------------------;Programmbeginn 6 ;-----------------------------------------------------------------------ABFRAGE: Prof. J. Walter Mikrocomputertechnik 5 Projekte mit Assembler gelöst ;--------------------------------------------------------------------- Tabelle 5.3 TMOD BYTE 7 C/T# M1/M0 0 0 0 1 1 0 1 1 1 1 C/T# Timer 1 M1 M0 GATE C/T# Timer 0 M1 M0 TMOD Funktion Gating control "1" durchgeschaltet, wenn INTx#-Pin auf "1" und TRx Kontrollbit gesetzt. "0" => Timer x zählt, wenn TRx Kontrollbit gesetzt ist Counter or timer select bit. Zähler oder Zeitgeber Auswahlbit "1" Zähler Funktion ( Eingang am TxD Eingangspin vom Prozessor ) "0" Zeitgeber Funktion ( Eingang vom internen System Clock ) 8-bit timer / counter THx ist ein 8-bit Zähler / Zeitgeber - TLx dient als 5-bit Vorteiler 16-bit timer/counter "THx" und TLx" ergeben zusammen einen 16-bit-Zähler / Zeitgeber. 8-bit auto-reload timer / counter 8-bit automatisch ladender Zähler / Zeitgeber. THx enthält den Wert der in TLx bei jedem Überlauf geladen wird. Timer 0: TL0 ist ein 8-bit-Zähler / Zeitgeber der von den Kontrollbits von Timer 0 kontrolliert wird. TH00 ist ein 8 Bit Zeitgeber der nur von den Zeitgeber 1 Kontrollbits kontrolliert wird. Timer 1. Zähler / Zeitgeber hält Stand November 2007 Bit Gate GATE Prof. J. Walter Mikrocomputertechnik 5 Projekte mit Assembler gelöst 89H Abb. 5.1 Blockbild von Timer 0 und 1 im 16-Bit Modus C/T#=0 Takt Timer overflow flag TH0 TL0 C/T#=1 T0 / P 3.4 interner Bus TR0 Tim e r run control bit INT0# >1 & Stand November 2007 TF0 12 Gate 8 Interrupt Prof. J. Walter Mikrocomputertechnik 5 Projekte mit Assembler gelöst OSC 12 TF0 C/T#=0 Takt Timer overflow flag TH0 C/T#=1 T0 / P 3.4 TR0 Tim e r run control bit Gate INT0# 9 Interrupt >1 & Reload TL0 Stand November 2007 OSC im Chip Prof. J. Walter Mikrocomputertechnik 5 Projekte mit Assembler gelöst Abb. 5.2 Mode 2, Zähler / Zeitgeber 0,1 mit Wiederladen des TL0 Registers Abb. 5.3 Mode 3, Timer 1 Interrupt wird von Timer 0 mitbenutzt Interrupt 12 C/T#=0 Takt Timer 0 overflow flag TL0 C/T#=1 T0 / Timer 1 overflow flag P 3.4 TF1 interner Bus TR0 Tim e r run control bit Gate INT0# >1 & f /12 osc Takt Control 10 Stand November 2007 TF0 Interrupt TR1 TH0 Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik OSC Tabelle 5.4 TCON BITS Timer 0 - Timer 1 Control Bits 11 8DH 8CH 8B 8AH 89H 88H TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0 TCON Diese Bits werden nicht zur Kontrolle des Zeitgebers verwendet Bit Funktion TR0 Timer 0 run control bit. Bit zum Starten und Stoppen des Zeitgebers 0 TF0 Timer 0 overflow flag. Wird hardwaremäßig beim Zeitgeber / Zählerüberlauf gesetzt. Wird bei Aufruf des entsprechenden Interrupts zurückgesetzt. TR1 Timer 1 run control bit. Bit zum Starten und Stoppen des Zeitgebers 1 TF1 Timer 1 overflow flag. Wird hardwaremäßig beim Zeitgeber / Zählerüberlauf gesetzt. Wird bei Aufruf des entsprechenden Interrupts zurückgesetzt. Stand November 2007 8EH Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik 88H 8FH 12 0043H 004BH ADCI EXTI2 0053H EXTI3 005BH EXTI4 0063H EXTI5 006BH EXTI6 0083H 0093H SINT1 CMINT 009BH 00A3H COMPTIMER SETINT 00ABH CLRINT Erklärung Start Address after Reset1) External Interrupt 01) Timer 0 Overflow Interrupt1) External Interrupt 11) Timer 1 Overflow Interrupt1) Serial Channel 0 Interrupt1) Timer 2 Overflow/ External Reload Interrupt2)-6) A/D-Converter Interrupt3).....6) External Interrupt 2/ Compare Event with CC43).....6) Bei 80C515 External Interrupt only External Interrupt 3 / Compare Event with CRC3).....6) External Interrupt 4 / Compare Event with CC13).....6) External Interrupt 5 / Compare Event with CC23).....6) External Interrupt 6 / Compare Event with CC33).....6) Serial Channel 1 Interrupt4)6) CMx Compare Register Interrupt6) Compare Timer Overflow4)6) Compare Set Interrupt6) Compare Clear Interrupt6) Stand November 2007 Tabelle 5.5 InterruptVektorAdressen 002BH Interrupt-Name RESET EXTIO TIMER 0 EXTI1 TIMER1 SINT SINT04)6) TIMER2 Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik PC Adresse 0000H 0003H 000BH 0013H 001BH 0023H IE0 P3.2/INT0 TCON.0 TF0 TIMER 0 Overflow IE1 P3.3/INT1 TIMER 1 Overflow RI Receiver >1 Abb. 5.4 Erzeugen von Interrupts SERIAL PORT Transmitter TI TIMER 2 Overflow TF2 >1 P1.5/T2EX EF2 EXEN2 P1.4/INT2 IEX2 TCON.5 Compare 0 P1.0/INT3/CC0 IEX3 TCON.6 IEX4 P1.1/INT4/CC1 Compare 1 P1.2/INT5/CC2 IEX5 Compare 1 P1.3/INT6/CC3 C O N T R O L IADC A/D-Converter Compare 1 13 I N T E R R U P T Stand November 2007 TF1 Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik TCON.2 IEX6 Tabelle 5.6 IEN0 Interrupt 0 Control Bits ET2 ES ET1 EX1 ET0 EX0 IEN0 Wird nicht für Interrupt-Kontrolle genutzt Bit Funktion EX0 "0" Externer Interrupt 0 gesperrt "1" Externer Interrupt 0 freigegeben "0" Überlauf Timer 0 gesperrt "1" Überlauf Timer 0 freigegeben "0" Externer Interrupt 1 gesperrt "1" Externer Interrupt 1 freigegeben "0" Überlauf Timer 1 gesperrt "1" Überlauf Timer 1 freigegeben "0" Serieller Schnittstellen Interrupt gesperrt "1" Serieller Schnittstellen Interrupt freigegeben "0" Überlauf Timer 2 gesperrt "1" Überlauf Timer 2 freigegeben Wird nicht für Interrupt Kontrolle genutzt "0" Kein Interrupt wird erkannt "1" Jeder Interrupt wird entsprechend seiner Einstellung erkannt ET0 EX1 ET1 ES ET2 WDT EAL 14 WDT Stand November 2007 WDT EAL Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik 0A8H 0BEH 0BDH 0BCH 0BBH 0BAH 0B9H 0B8H EXEN2 SWDT EX6 EX5 EX4 EX3 EX2 EADC Bit Funktion EADC "0" A/D-Wandler Interrupt gesperrt. "1" A/D-Wandler freigegeben. "0" externer Interrupt 2 gesperrt. "1" externer Interrupt 2 / Übernahme- / Vergleichs-Interrupt 4 freigegeben. "0" externer Interrupt 3 gesperrt. "1" externer Interrupt 3 / Übernahme- / Vergleichs-Interrupt 4 freigegeben. "0" externer Interrupt 4 gesperrt. "1" externer Interrupt 4 / Übernahme- / Vergleichs-Interrupt 4 freigegeben. "0" externer Interrupt 5 gesperrt. "1" externer Interrupt 5 / Übernahme- / Vergleichs-Interrupt 4 freigegeben. "0" externer Interrupt 6 gesperrt. "1" externer Interrupt 6 / Übernahme- / Vergleichs-Interrupt 4 freigegeben. Wird nicht für Interrupt Kontrolle genutzt "0" Externer Reload Interrupt Timer 2 wird gesperrt. "1" Externer Reload Interrupt Timer 2 wird erkannt. EX2 EX3 EX4 EX5 EX6 SWDT EXEN2 15 IEN1 Stand November 2007 0A8H 0BFH Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Tabelle 5.7 Interrupt Control Bits 8EH 8DH 8CH 8B 8AH 89H 88H TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0 Bit IT0 IE0 IT1 IE1 TR0 TF0 TR1 TF1 16 Funktion Interrupt 0 type control bit. Auswahlbit für Arbeitsweise "1" Fallende Flanke löst externen Interrupt aus "0" 0-Pegel löst externen Interrupt aus "1" Falls externer Interrupt durch Hardware erkannt wird. "0" automatisch durch Interruptausführung Interrupt 1 type control bit. Auswahlbit für Arbeitsweise "1" Fallende Flanke löst externen Interrupt aus "0" 0-Pegel löst externen Interrupt aus "1" Falls externer Interrupt durch Hardware erkannt wird. "0" automatisch durch Interruptausführung Timer 0 Run Control - Wird nicht für Interrupt Kontrolle genutzt. Timer 0 overflow flag. "1" durch Hardware, wenn Zähler / Zeitgeber Überlauf. "0" automatisch durch Interruptausführung Timer 1 Run Control - Wird nicht für Interrupt Kontrolle genutzt Timer 1 overflow flag. "1" durch Hardware, wenn Zähler / Zeitgeber Überlauf. "0" automatisch durch Interruptausführung TCON Stand November 2007 88H 8FH Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Tabelle 5.8 TCON Interrupt Control Bits 17 Prof. J. Walter Stand November 2007 5 Projekte mit Assembler gelöst Mikrocomputertechnik Abb. 5.4 Zu viele Interrupts IP1.0 IP0.0 IEN 0.7 IEN 0.0 IE0 I Level 3 N Level 2 T Level 1 E R Level 0 R U R E Abb. 5.6 Prioritäten / Anforderungen von Interrupts Q U E S T IEN 0.1 TF0 IP 1.1 IP 0.1 IEN 1.1 IEX2 P R IEN 0.2 IE1 IP 1.2 IP 0.2 IEN 1.2 O IEX3 R I IEN 0.3 TF1 IP 1.3 IP 03 IEN 1.3 C IEN 0.4 >1 TI IP 1.4 IP 0.4 IEN 1.4 R IEN 0.5 18 EXF2 IEX6 >1 IP 1.5 IEN 1.5 O N T IEX5 TF2 T Y IEX4 RI I IP 0.5 O L Vector Locations Stand November 2007 IEN 1.0 IADC Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik P T 19 - WDTS IP0.5 IP0.4 IP0.3 IP0.2 IP0.1 IP0.0 IP0 0B9H - - IP1.5 IP1.4 IP1.3 IP1.2 IP1.1 IP1.0 IP1 IP1.x IP0.x Funktion 0 0 Priorität 0 (kleinste) 0 1 Priorität 1 1 0 Priorität 2 1 1 Priorität 3 Stand November 2007 0A9H Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Tabelle 5.9 IP0 Interrupt Priority Bits Programmbeschreibung Initialisierung TIMER_0 Welche Taste wurde betätigt ? ja Taster 1 TR0 aus Port 3.2 löschen Licht ein Taster 2 TR0 aus Port 3.2 setzen Licht aus Register 2 = 0 ? Taster 3 Blinken TR0 an TIMER_0 P 3.2 Komplement ret 20 Stand November 2007 Assembler Anweisungen nein Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Abb. 5.7 Struktogramm für Blink-Programm 21 Prof. J. Walter Stand November 2007 5 Projekte mit Assembler gelöst Mikrocomputertechnik Abb. 5.8 Die Schaltfläche „Zauberstab“ in der Keil Entwicklungsumgebung 22 Prof. J. Walter Stand November 2007 5 Projekte mit Assembler gelöst Mikrocomputertechnik Abb. 5.9 Die Einstellungen für den Simulator 23 Leuchte 2 AUS AUS EIN EIN Leuchte 3 AUS EIN AUS EIN Stand November 2007 Spannung 0V U 2 V 2V< U 3 V 3V< U 4 V 4V< U 5 V Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Tabelle 5.11 Codierung Abb. 5.11 Blockbild A/D-Wandler im 80535 P6 (0DBH) ADCON (0D8H) 7 6 5 4 3 2 1 0 ADDAT (0D9H) AN7/P 6.7 AN6/P 6.6 AN5/P 6.5 AN4/P 6.4 AN3/P 6.3 AN2/P 6.2 AN1/P 6.1 AN0/P 6.0 Multiplexer Sample & Hold A/D-Wandler V AREF V AGND 7 6 5 4 3 2 1 0 Internal Reference Voltages DAPR (0DAH) 7 6 5 4 3 2 1 0 24 Programmierung V intAREF Programmierung V intAGND Stand November 2007 Port 6 Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik ACMOS interner Bus 1 K VCC +5V VGA Pin 4 VAREF VGA Pin 26 AN0 VGA Pin 27 VAGND VGA Pin 31 VGA Pin 21 GND 0V 25 Stand November 2007 Anschluß EURO_535 Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Abb. 5.12 Anschluss eines Potentiometers an EURO_535 26 0 1 U in V 0 0,0196 …… 101 102 103 1,9803 2 2,0196 ….. 254 255 4,9804 5 Stand November 2007 Zahl Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Tabelle 5.12 Wert – Spannung VCC J3 1 2 3 4 5 6 7 8 IC1 DB0 V OUT DB1 V OUT SENSE DB2 V OUT SELECT DB3 GND DB4 GND DB5 +VCC DB6 CS DB7 CE AD558 R11 16 15 14 13 12 11 10 9 B1 1 1K R9 ANALOG OUT1 B13 JUMPER DA1 VCC 1 1K lin GND BNC1 R2 P4.1 P5.0 P5.1 P5.2 P5.3 P5.4 P5.5 P5.6 P5.7 1 2 3 4 5 6 7 8 IC2 DB0 V OUT DB1 V OUT SENSE DB2 V OUT SELECT DB3 GND DB4 GND DB5 +VCC DB6 CS DB7 CE AD558 R10 16 15 14 13 12 11 10 9 B2 1 1K 100 D2 ZD 5V6 PIN1 DA0 B14 VCC 1 GND 1 BNC2 R3 AN1 BNC 2 P4.0 Abb. 5.13 Schaltbild ADDA535Karte BNC 2 ANALOG OUT2 100 D3 ZD 5V6 PIN3 1 +5V VCC VSS X4 VCC R1 AN2 PIN5 2 P4.0 P5.0 P5.2 P5.4 P5.6 VCC AN0 AN2 AN4 AN6 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 VG1 A1 C1 A2 C2 A3 C3 A4 C4 A5 C5 A6 C6 A7 C7 A8 C8 A9 C9 A10 C10 A11 C11 A12 C12 A13 C13 A14 C14 A15 C15 A16 C16 A17 C17 A18 C18 A19 C19 A20 C20 A21 C21 A22 C22 A23 C23 A24 C24 A25 C25 A26 C26 A27 C27 A28 C28 A29 C29 A30 C30 A31 C31 A32 C32 VG_535Z 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 100 D1 ZD 5V6 1 R4 AN3 VDD X3 PIN6 2 P4.1 P5.1 P5.3 P5.5 P5.7 100 D4 ZD 5V6 1 R5 AN4 PIN7 2 100 D5 ZD 5V6 R6 AD/DA Zusatzkarte f uer 80535-Board AN5 PIN8 8 Analogeingaenge VCC 2 100 D6 ZD 5V6 2 Analogausgaenge 1 R7 Fachhochschule Karlsruhe, FB F AN6 PIN9 2 100 D7 ZD 5V6 1 R8 PIN10 2 1 100 D8 ZD 5V6 PIN5 PIN6 PIN7 PIN8 PIN9 PIN10 1 2 3 4 5 6 7 8 9 10 PL1 PIN1 PIN2 PIN3 PIN4 PIN5 PIN6 PIN7 PIN8 PIN9 PIN10 PINLEISTE_10 Joachim Juengst, Januar 1994 AN1 AN3 AN5 AN7 PIN1 PIN3 1 AN7 27 Stand November 2007 5 Projekte mit Assembler gelöst Mikrocomputertechnik AN0 Prof. J. Walter P5.0 P5.1 P5.2 P5.3 P5.4 P5.5 P5.6 P5.7 Tabelle 5.13 ADCON REGISTER 0DCH 0DBH 0DAH 0D9H 0D8H CLK BSY ADM MX2 MX1 MX0 Bit MX2 MX1 MX0 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 Funktion ADM "1" Kontinuierliche Wandlung. "0" Stop nach jeder Wandlung "1" Busy Flag / Wandlung findet statt. "0" Wandlung beendet frei CLK - Wird nicht für A/D-Wandler verwendet Baudrate - Wird nicht für A/D-Wandler verwendet BSY 28 - CLK BD MYMOS ACMOS Anlog Eingang 0 AN0 P6.0 Anlog Eingang 1 AN1 P6.1 Anlog Eingang 2 AN2 P6.2 Anlog Eingang 3 AN3 P6.3 Anlog Eingang 4 AN4 P6.4 Anlog Eingang 5 AN5 P6.5 Anlog Eingang 6 AN6 P6.6 Anlog Eingang 7 AN7 P6.7 ADCON Stand November 2007 0D8H BD 0DEH 0DDH Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik 0DFH 29 7 6 DAPR .3 - .0 DAPR .4 - .7 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 3 VintAGND 0. - 3. Bit 0,0 0,3125 0,625 0,9375 1,25 1,5625 1,875 2,1875 2,5 2,8125 3,125 3,4375 3,75 - 2 VintAREF 4. - 7. Bit 5,0 1,25 1,5625 1,875 2,1875 2,5 2,8125 3,125 3,4375 3,75 4,0625 4,375 4,68754 DAPR .0 - .3 1 0 DAPR Stand November 2007 0DAH DAPR .4 - .7 5 4 Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Tabelle 5.14 Erhöhung der Auflösung durch Einschränkung des Messbereiches 30 5 Projekte mit Assembler gelöst Mikrocomputertechnik Prof. J. Walter Stand November 2007 Abb. 5.14 Anzeige des ADDAT-Inhalts im DebugProgramm 0 1 0 0 0 0 0 0 0 Sender 0 0 1 0 0 Empfänger 0 1 1 1 0 1 0 0 31 0 0 1 1 1 zeitlich nacheinander 1 0 Stop Bit 1 1 1 0 1 0 0 0 Start Bit 0 1 1 1 0 1 0 0 Stand November 2007 0 1 1 1 Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Abb. 5.15 Umsetzung von parallel in seriell 32 Prof. J. Walter Stand November 2007 5 Projekte mit Assembler gelöst Mikrocomputertechnik Abb. 5.16 Einstellungen der seriellen Schnittstelle 33 Prof. J. Walter Stand November 2007 5 Projekte mit Assembler gelöst Mikrocomputertechnik Abb. 5.17. Einstellungen der seriellen Schnittstelle am „PC“ 34 5 Projekte mit Assembler gelöst Mikrocomputertechnik Prof. J. Walter Stand November 2007 Abb. 5.18 Einstellungen der seriellen Schnittstelle 80535 Tabelle 5.15 SCON Bits REN TB8 RB8 TI RI 35 09DH 09CH 09BH 09AH 099H 098H SM2 REN TB8 RB8 TI RI SCON Symbol SM1 0 1 0 1 Mode 0: Synchroner Modus, feste Baudrate fosc/12 Mode 1: 8-Bit UART, variable Baudrate Mode 2: 9-Bit UART, feste Baudrate fosc/64 oder fosc/32 Mode 3: 9-Bit UART, variable Baudrate Ermöglicht Multiprozessor-Kommunikation in Mode 2 und 3 Empfänger-Interrupt wird nicht ausgelöst, falls das neunte Datenbit "0" ist. In Mode 1 und SM2="1" wird der Interrupt ebenfalls nicht aktiviert falls kein gültiges Stopbit empfangen wird. In Mode 0 muß SM2="0" sein. Receiver enable. "1" Gibt den seriellen Empfang durch Software frei. "0" sperrt den Empfang. Übertragungsbit 8. Das neunte Bit für Mode 2 und 3 Wird durch Software gesetzt und rückgesetzt. Empfangsbit 8. Neunte Bit für Empfang in Mode 2 und 3 Übertragungsinterrupt. Wird durch die Hardware am Ende des achten Bits in Mode 0 gesetzt, oder am Beginn des Stop-Bits in den anderen Moden. Muss durch Software zurückgesetzt werden. Empfängerinterrupt. Ist das empfangene Interrupt-Flag. Wird am Ende des achten Bits in Mode 0 gesetzt, oder am Beginn des Stop-Bits in den anderen Modi. Muss durch Software zurückgesetzt werden. Stand November 2007 Bit SM0 0 0 1 1 SM2 09EH SM1 Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik 98H 09FH SM0 36 99H Stand November 2007 SBUF Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik SBUF Empfangs- und Senderegister für serielle Schnittstelle Abb. 5.19 Erzeugen der Baudrate 37 ADCON.7 (BD) Stand November 2007 Overflow fosc/2 SM0 SM1 SMOD *1/39 *1/2 Baud Rate Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Timer 1 38 SMOD Bit SMOD PCON Funktion "1" Baudrate wird in Mode 1,2,3 verdoppelt Stand November 2007 99H Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Baudraten im PCON Power Control Register Tabelle 5.16 ADCON REGISTER 39 0DDH CLK - 0DCH 0DBH 0DAH 0D9H 0D8H Bit Funktion BD Baudrate - Wird nicht für A/D-Wandler verwendet ADCON CLK "1" Der Takt wird nach außen an Pin P1.6/CLKOUT weitergeleitet Stand November 2007 0D8H BD 0DEH Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik 0DFH 40 fosc(MHz) SMOD TIMER 1 C/(/T) Mode Reload Value 62,5 Kbaud 19,5 Kbaud 9,6 Kbaud 4,8 Kbaud 2,4 Kbaud 1,2 Kbaud 110 Baud 110 Baud 12,0 11,059 11,059 11,059 11,059 11,059 6,0 12,0 0 0 0 0 0 0 0 0 1 1 0 0 0 0 0 0 2 2 2 2 2 2 2 1 0FFH 0FDH 0FDH 0FAH 0F4H 0E8H 72H 0FEEBH Stand November 2007 Baud Rate Mode 1,3 Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Tabelle 5.17 Allgemein verwendete Baudraten 41 Signalgenerator A/D-Wandler Zeitgeber Serielle Schnittstelle Ueff t Stand November 2007 µ-Controller Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Abb. 5.20 Blockschaltbild für Effektivwertmesser Stand November 2007 Sinus mit 100 Hz; abgetastet mit 1000 Hz 3 Prof. J. Walter 2,5 2 Ue 5 Projekte mit Assembler gelöst Mikrocomputertechnik Bild 5.21. Abgetasteter Sinus 1,5 1 0,5 0 0 5 10 15 20 25 t in ms 42 30 35 40 45 Timer 2 16 Bit Tim er 2 Interrupt Interrupts 16 Bit Komparator 16 Bit Komparator 16 Bit Komparator P1.0/CC0 E/ASteuerung 8 CCH3 CCL3 CCH2 CCL2 CCH1 CCL1 Interner Bus 8 Bit 43 16 Bit Komparator CRCH CRCL P1.1/CC1 P1.2/CC2 P1.3/CC3 Stand November 2007 P1.5/T2EX Fosc/12(24) Gegattertes Fosc/12(24) Fallende Flanke an P1.7/T2 Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Abb. 5.22 Blockschaltbild Zeitgeber 2 44 Bedeutung CRCH, CRCL Compare Reload Capture High / Low Register CCH1, CCL1 Compare Capture High / Low Register 1 CCH2, CCL2 Compare Capture High / Low Register 2 CCH3, CCL3 Compare Capture High / Low Register 3 Stand November 2007 Abkürzung Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Tabelle 5.18 Verwendetet Abkürzungen Tabelle 5.19 Timer 2 Control-Bits Bit T2I1 T2I0 0 0 0 1 1 0 1 1 T2R1 T2R0 0 X 1 0 1 1 T2CM I2FR I3FR 45 T2PS I2FR T2R1 T2R0 T2CM T2I1 T2I0 T2CON Funktion Timer 2 input selection. Auswahl des Eingangs. Kein Eingang gewählt. - Zeitgeber zählt nicht Zeitgeberbetrieb. Frequenz = fosc/12 (T2PS="0" ) - fosc/24 (T2PS="1" ). Zählerbetrieb. An Pin T2/P1.7 muss externes Signal anliegen. Zeitgeberbetrieb mit Gatterfunktion. Gatter wird über Pin T2/P1.7 gesteuert. Timer 2 reload mode selection. Zeitgeber 2 Wiederladebetrieb Wiederladen gesperrt. Modus 0: Wiederladen bei Timer 2 Überlauf ( TF2 ) Modus 1: Wiederladen bei fallender Flanke an Pin T2EX/P1.5 Compare mode / Vergleichsmodus für Register CRC, CC1, CC2, CC3. "0" Vergleich bei Überlauf des Timers 2 "1" Fallende Flanke an Pin T2EX/P1.5 löst Vergleich aus. Dieses Bit wird nicht zur Kontrolle des Zeitgebers 2 verwendet External Interrupt 3 falling / rising edge flag. Wird ebenso für die Übernahmefunktion in Kombination mit dem CRC Register benutzt. "0" Übernahme erfolgt bei negativer Flanke an P1.0. "1" Übernahme erfolgt bei Freigabe an positiver Flanke an P1.0. Prescaler select bit / Vorteiler Bit. "0" für die Zählerfunktion 1/12 der Oszillatorfrequenz Stand November 2007 0C8H T2PS I3FR Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik 0CFH 0CEH 0CDH 0CCH 0CBH 0CAH 0C9H 0C8H 46 Bit Erklärung Interrupt Timer 2 Enable Interrupt A/D-Converter Timer Flag 2 Interrupt A/D-Converter Stand November 2007 Aktion Bit Interruptfreigabe Timer 2 ET2 Interruptfreigabe A/D-Wandler EADC Interruptbestätigung Timer 2 TF2 Interruptbestätigung A/D-Wandler IADC Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Tabelle 5.20 Lösung der Aufgabe mit Interrupts Programmbeschreibung Initialisierung Interrupt A/D Timer2 Interrupt-Unterprogramm Wert von ADDAT in ext. Speicher Sind 40 Werte eingelesen ? Timer 2 sperren Leuchte 2 ausschalten 47 Stand November 2007 Assembler Anweisungen Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Abb. 5.23 Struktogramm für AD_40T2 Programmbeschreibung Timer 2 Initialisieren Warten auf TF2 Warten auf BSY Wert von ADDAT in ext. Speicher Sind 40 Werte eingelesen ? Neue Wandlung / Ende ? 48 Stand November 2007 Assembler-Anweisungen Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Abb. 5.24 Struktogramm für AD_40T2O A/D-Wandlung ohne Interrupts Abb. 5.25 Abgetastete Sinus mit Offset Stand November 2007 Sinus - Offset Sinus-Offset quadriert 2,5 Prof. J. Walter 2 1,5 1 0,5 0 0 0,005 0,01 0,015 0,02 -0,5 -1 Zeit T / [s] 49 abgetasteter Sinus mit Offset 3 Spannung u / [V] 5 Projekte mit Assembler gelöst Mikrocomputertechnik Abgetasteter Sinus mit Offset 0,025 0,03 0,035 0,04 50 80535 Signalgenerator 2000H 2001H 2002H 1. Wert 2. Wert 2027H 40. Wert A/D Stand November 2007 Speicher Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Abb. 5.26 Speicherinhalt nach A/D-Wandlung von 40 Werten, AD_40 51 5 Projekte mit Assembler gelöst Mikrocomputertechnik 80535 30H interner Speicher 57H 2027H 2028H 2029H 40. Wert 1. Wert LB 1. Wert HB 2077H 40. Wert HB CPU Quadrieren Prof. J. Walter externer Speicher 1. Wert 2000H 2. Wert 2001H 2002H Stand November 2007 Abb. 5.27 Speicherinhalt nach Quadrieren Abb. 5.28 Speicherinhalt nach Addition 52 2000H 2001H 2002H 1. Wert 2. Wert 2027H 2028H 2029H 40. Wert 1. Wert LB 1. Wert HB 2077H 2078H 2079H 207AH 207BH 40. Wert HB 1. Wert Addition 2. Wert Addition 3. Wert Addition 4. Wert Addition Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik 80535 Stand November 2007 externer Speicher CPU Addition LB+0 LB+1 LB+2 LB+3 53 Stand November 2007 externer Speicher 2077H 2078H 2079H 207AH 207BH 0F A0 58 02 bel. LB+0 LB+1 LB+2 LB+3 Prof. J. Walter 5 Projekte mit Assembler gelöst Mikrocomputertechnik Abb. 5.29 Speicherinhalt nach Addition