mc - HIT Karlsruhe

Werbung

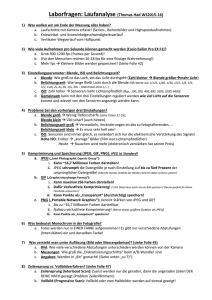

mc Mikrocomputertechnik - Kapitel 5 Herzlich Willkommen Prof. Jürgen Walter Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 1 mc Tabelle 5.1 Verwendete Einheiten - Projekte Projekt verwendete Einheiten 1. Blinklicht mit vorgegebener Blinkfrequenz Timer 0,1 Interrupt 2. A/D-Wandlung A/D-Wandler 3. Serielle Schnittstelle Serielle Schnittstelle 4. Effektivwertmessung Timer, A/D-Wandler, Serielle Schnittstelle Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 2 mc 3 Goldene Regeln für 8051 Programme Prof. J. WALTER Nur dokumentierte Hard- und Software ist existent. Durchgänge Verwendung von Registern mit Herstellung des Ausgangszustandes. Zuordnung von Tasks (Aufgaben – Prozesse) zu Registerbänken. Bei umfangreicher Software unbedingt Hochsprache C verwenden. Kurstitel Stand: Oktober 2001 Seite 3 mc Standardkopf für Programme Prof. J. WALTER Assembler Anweisungen Programmbeschreibung Initialisierungsteil für allgemeine Konstanten Initialisierungsteil für On-Chip Peripherie Kurstitel Stand: Oktober 2001 Seite 4 Assembler-Anweisungen mc $nomod51 ;der Modus fuer 8051 wird abgeschaltet $debug $nolist ;es wird kein Listing fuer reg535 erstellt $include(reg535.pdf) ;die 80535-spezifischen Daten $list ;es wird ein Listing erstellt $ title () Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 5 Programmbeschreibung mc ;-----------------------------------------------------------------------;Programmbeschreibung ;-----------------------------------------------------------------------;Programm: ;Datum: ;Programmiert: J. Walter ;Verwendete Einspruenge: keine ;Verwendete Unterprogramme: keine ;Verwendete Register und Variable: ;Registerbank(0) ;R2 ;Kommentar: ; ;Aenderungen: ;Datum: ; ; Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 6 mc Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 7 mc Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 8 mc Tabelle 5.11. Codierung Spannung 0V <=U <= 2 V 2V< U <=3 V 3V< U <=4 V 4V< U <= 5 V Prof. J. WALTER Kurstitel Stand: Oktober 2001 Leuchte 2 AUS AUS EIN EIN Leuchte 3 AUS EIN AUS EIN Seite 9 mc Bild 5.11. Blockbild A/D-Wandler P6 (0DBH) ACMOS Port 6 ADCON (0D8H) 7 6 5 4 3 2 1 0 ADDAT (0D9H) AN7/P 6.7 AN6/P 6.6 AN5/P 6.5 AN4/P 6.4 AN3/P 6.3 AN2/P 6.2 AN1/P 6.1 AN0/P 6.0 Multiplexer Sample & Hold 7 6 5 4 3 2 1 0 A/D-Wandler V AREF Internal Reference Voltages V AGND DAPR (0DAH) 7 6 5 4 Programmierung V intAREF Prof. J. WALTER Kurstitel Stand: Oktober 2001 3 2 1 0 Programmierung V intAGND interner Bus Seite 10 mc Bild 5.12. Anschluß eines Potentiometers an EURO_535 Anschluß EURO_535 VCC 1 K +5V VAREF VGA Pin 26 AN0 VGA Pin 27 VAGND VGA Pin 31 VGA Pin 21 GND 0V Prof. J. WALTER Kurstitel Stand: Oktober 2001 VGA Pin 4 Seite 11 mc Prof. J. WALTER Tabelle 5.12. Wert - Spannung Kurstitel Stand: Oktober 2001 Zahl Spannung / V 0 0 1 0,01960784 ...... ...... 50 0,98039216 51 1 52 1,01960784 ...... ...... 101 1,98039216 102 2 103 2,01960784 ...... ...... ...... ...... 254 4,98039216 255 5 Seite 12 mc Bild 5.13. Schaltbild ADDA535-Karte VCC J3 P5.0 P5.1 P5.2 P5.3 P5.4 P5.5 P5.6 P5.7 1 2 3 4 5 6 7 8 IC1 DB0 V OUT DB1 V OUT SENSE DB2 V OUT SELECT DB3 GND DB4 GND DB5 +VCC DB6 CS DB7 CE AD558 R11 16 15 14 13 12 11 10 9 B1 1 1K R9 ANALOG OUT1 B13 VCC 1 1K lin JUMPER DA1 GND BNC1 R2 P4.1 AN0 P5.0 P5.1 P5.2 P5.3 P5.4 P5.5 P5.6 P5.7 1 2 3 4 5 6 7 8 IC2 DB0 V OUT DB1 V OUT SENSE DB2 V OUT SELECT DB3 GND DB4 GND DB5 +VCC DB6 CS DB7 CE AD558 R10 16 15 14 13 12 11 10 9 B2 1 1K BNC 2 ANALOG OUT2 VCC PIN1 DA0 B14 100 D2 ZD 5V6 1 GND 1 BNC2 R3 AN1 BNC 2 P4.0 100 D3 ZD 5V6 PIN3 1 +5V VCC VSS X4 VCC R1 AN2 PIN5 2 P4.0 P5.0 P5.2 P5.4 P5.6 VCC AN0 AN2 AN4 AN6 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 VG1 A1 C1 A2 C2 A3 C3 A4 C4 A5 C5 A6 C6 A7 C7 A8 C8 A9 C9 A10 C10 A11 C11 A12 C12 A13 C13 A14 C14 A15 C15 A16 C16 A17 C17 A18 C18 A19 C19 A20 C20 A21 C21 A22 C22 A23 C23 A24 C24 A25 C25 A26 C26 A27 C27 A28 C28 A29 C29 A30 C30 A31 C31 A32 C32 VG_535Z 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 100 D1 ZD 5V6 1 R4 AN3 VDD X3 PIN6 2 100 D4 ZD 5V6 P4.1 P5.1 P5.3 P5.5 P5.7 1 R5 AN4 PIN7 2 100 PIN3 D5 ZD 5V6 1 R6 AD/DA Zusatzkarte f uer 80535-Board AN5 PIN8 8 Analogeingaenge VCC 2 100 D6 ZD 5V6 2 Analogausgaenge PIN1 PIN5 PIN6 PIN7 PIN8 PIN9 PIN10 1 2 3 4 5 6 7 8 9 10 PL1 PIN1 PIN2 PIN3 PIN4 PIN5 PIN6 PIN7 PIN8 PIN9 PIN10 PINLEISTE_10 Joachim Juengst, Januar 1994 AN1 AN3 AN5 AN7 1 R7 Fachhochschule Karlsruhe, FB F AN6 PIN9 2 100 D7 ZD 5V6 1 R8 AN7 PIN10 2 100 D8 ZD 5V6 1 Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 13 mc Tabelle 5.13. ADCON REGISTER 0DFH 0D9H BD 0DEH CLK - 0DCH BSY 0DB ADM 0DAH MX2 Bit Funktion MX2 MX1 MX0 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 MYMOS ACMOS Anlog Eingang 0 AN0 P6.0 Anlog Eingang 1 AN1 P6.1 Anlog Eingang 2 AN2 P6.2 Anlog Eingang 3 AN3 P6.3 Anlog Eingang 4 AN4 P6.4 Anlog Eingang 5 AN5 P6.5 Anlog Eingang 6 AN6 P6.6 Anlog Eingang 7 AN7 P6.7 ADM "1" Kontinuierliche Wandlung. "0" Stop nach jeder Wandlung BSY "1" Busy Flag / Wandlung findet statt. "0" Wandlung beendet - Prof. J. WALTER 0DDH MX1 0D8H MX0 ADCON frei CLK CLK - Wird nicht für A/D-Wandler verwendet BD Baudrate - Wird nicht für A/D-Wandler verwendet Kurstitel Stand: Oktober 2001 0D9H Seite 14 mc Tabelle 5.14. Erhöhung der Auflösung durch Einschränkung des Meßbereiches DAPR .3 - .0 DAPR .4 - .7 VintAGND 0. - 3. Bit VintAREF 4. - 7. Bit 0000 0,0 5,0 0001 0,3125 - 0010 0,625 - 0011 0,9375 - 0100 1,25 1,25 0101 1,5625 1,5625 0110 1,875 1,875 0111 2,1875 2,1875 1000 2,5 2,5 1001 2,8125 2,8125 1010 3,125 3,125 1011 3,4375 3,4375 1100 3,75 3,75 1101 - 4,0625 1110 - 4,375 1111 - 4,68754 Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 15 mc Prof. J. WALTER Bild 5.14. Anzeige des ADDAT-Inhalts im Debug-Programm Kurstitel Stand: Oktober 2001 Seite 16 Bild 5.15. Umsetzung von parallel in seriell mc 0 1 1 1 0 1 0 0 0 0 Sender 0 1 0 0 0 1 0 0 0 1 1 1 zeitlich nacheinander 1 0 Stop Bit Kurstitel Stand: Oktober 2001 0 Empfänger 0 1 1 1 Prof. J. WALTER 0 0 0 0 1 1 1 0 1 0 0 1 1 1 0 0 Start Bit 0 1 0 0 Seite 17 mc Prof. J. WALTER Bild 5.16. Einstellungen der seriellen Schnittstelle Kurstitel Stand: Oktober 2001 Seite 18 mc Prof. J. WALTER Bild 5.17. Einstellungen im Terminalprogramm Windows 98 Kurstitel Stand: Oktober 2001 Seite 19 Bild 5.18. Wechselspiel zwischen PC und Controller mc PC t Controller Remote-Debug-Programm Hitop.exe lädt Seriel_1.HTX Seriel_1.HTX steht im Programmspeicher Start des Programmes Seriel_1.HTX Programm wartet auf Taster 1="0" Hitop.exe wird beendet Start von Terminalprogramm Einstellungen vornehmen Taster 1 betätigt, Programm wird fortgesetzt. Testzeichen "A" erscheint B wird gesendet b empfangen Prof. J. WALTER Kurstitel Stand: Oktober 2001 B+20H ergibt b - Rückgabe an Terminalprogramm Seite 20 mc Tabelle 5.15. SCON Bits 09FH 98H SM0 Bit SM1 09DH SM2 09CH REN 09B TB8 09AH RB8 099H TI 098H RI SCON Symbol SM0 SM1 0 0 1 1 0 1 0 1 Prof. J. WALTER 09EH Mode 0: Mode 1: Mode 2: Mode 3: Synchroner Modus, feste Baudrate fosc/12 8-Bit UART, variable Baudrate 9-Bit UART, feste Baudrate fosc/64 oder fosc/32 9-Bit UART, variable Baudrate SM2 Ermöglicht Multiprozessor-Kommunikation in Mode 2 und 3 Empfänger-Interrupt wird nicht ausgelöst, falls das neunte Datenbit "0" ist. In Mode 1 und SM2="1" wird der Interrupt ebenfalls nicht aktiviert falls kein gültiges Stopbit empfangen wird. In Mode 0 muß SM2="0" sein. REN Receiver enable. "1" Gibt den seriellen Empfang durch Software frei. "0" sperrt den Empfang. TB8 Übertragungsbit 8. Das neunte Bit für Mode 2 und 3. Wird durch Software gesetzt und rückgesetzt. RB8 Empfangsbit 8. Neunte Bit für Empfang in Mode 2 und 3 TI Übertragungsinterrupt. Wird durch die Hardware am Ende des achten Bits in Mode 0 gesetzt, oder am Beginn des Stop-Bits in den anderen Moden. Muß durch Software zurückgesezt werden. RI Empfängerinterrupt. Ist das empfangene Interrupt-Flag. Wird am Ende des achten Bits in Mode 0 gesetzt, oder am Beginn des Stop-Bits in den anderen Modi. Muß durch Software zurückgesetzt werden. Kurstitel Stand: Oktober 2001 Seite 21 mc Bild 5.19. Erzeugen der Baudrate Timer 1 fosc/2 Overflow ADCON.7 (BD) SM0 SM1 SMOD *1/39 *1/2 Baud Rate Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 22 mc Baudraten im ADCON REGISTER A/D-Wandler Steuerung Bitadressierbar 0DFH 0D9H Prof. J. WALTER BD 0DEH CLK 0DDH 0DCH 0DB 0DAH 0D9H - ADCON Bit Funktion BD Baudrate - Wird nicht für A/D-Wandler verwendet CLK "1" Der Takt wird nach P1.6/CLKOUT weitergeleitet Kurstitel Stand: Oktober 2001 0D8H außen an Pin Seite 23 mc Tabelle 5.17. Allgemein verwendete Baudraten Baud Rate Mode 1,3 fosc(MHz) SMOD C/(/T) TIMER 1 Reload Mode Value 62,5 Kbaud 12,0 1 0 2 0FFH 19,5 Kbaud 11,059 1 0 2 0FDH 9,6 Kbaud 11,059 0 0 2 0FDH 4,8 Kbaud 11,059 0 0 2 0FAH 2,4 Kbaud 11,059 0 0 2 0F4H 1,2 Kbaud 11,059 0 0 2 0E8H 110 Baud 6,0 0 0 2 72H 110 Baud 12,0 0 0 1 0FEEBH Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 24 mc Bild 5.20. Blockschaltbild für Effektivwertmesser µ-Controller Signalgenerator A/D-Wandler Uef f t Zeitgeber Serielle Schnittstelle Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 25 mc Bild 5.21. Abgetasteter Sinus Sinus mit 100 Hz; abgetastet mit 1000 Hz 3 2,5 Ue 2 1,5 1 0,5 0 0 5 10 15 20 25 30 35 40 45 t in ms Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 26 Bild 5.22. Blockschaltbild Zeitgeber 2 mc P1.5/T2EX Fosc/12(24) Gegattertes Fosc/12(24) Fallende Flanke an P1.7/T2 Timer 2 16 Bit Tim e r 2 Inte rrupt Inte rrupts 16 Bit 16 Bit Komparator Komparator 16 Bit Komparator 16 Bit Komparator P1.0/CC0 E/ASteuerung 8 CCH3 CCL3 CCH2 CCL2 CCH1 CCL1 CRCH CRCL P1.1/CC1 P1.2/CC2 P1.3/CC3 Inte rne r Bus 8 Bit Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 27 mc Tabelle 5.18. Verwendete Abkürzungen Abkürzung Bedeutung CRCH, CRCL Compare Reload Capture High/Low Register CCH1, CCL1 Compare Capture High / Low Register 1 CCH2, CCL2 Compare Capture High / Low Register 2 CCH3, CCL3 Compare Capture High / Low Register 3 Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 28