Der Transistor als Schalter

Werbung

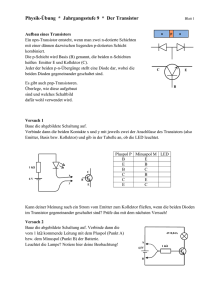

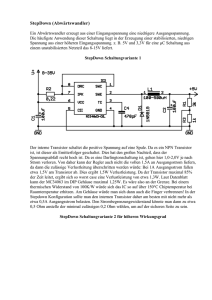

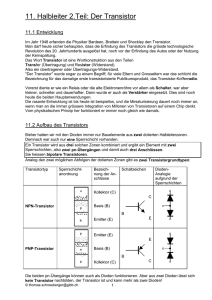

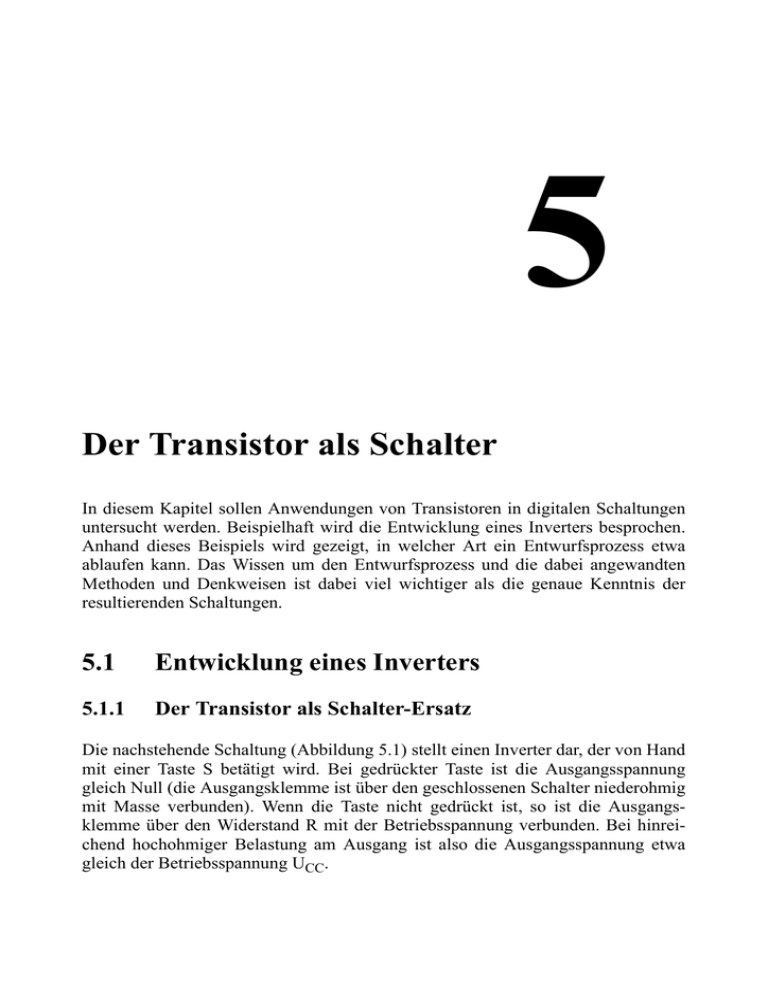

5 Der Transistor als Schalter In diesem Kapitel sollen Anwendungen von Transistoren in digitalen Schaltungen untersucht werden. Beispielhaft wird die Entwicklung eines Inverters besprochen. Anhand dieses Beispiels wird gezeigt, in welcher Art ein Entwurfsprozess etwa ablaufen kann. Das Wissen um den Entwurfsprozess und die dabei angewandten Methoden und Denkweisen ist dabei viel wichtiger als die genaue Kenntnis der resultierenden Schaltungen. 5.1 Entwicklung eines Inverters 5.1.1 Der Transistor als Schalter-Ersatz Die nachstehende Schaltung (Abbildung 5.1) stellt einen Inverter dar, der von Hand mit einer Taste S betätigt wird. Bei gedrückter Taste ist die Ausgangsspannung gleich Null (die Ausgangsklemme ist über den geschlossenen Schalter niederohmig mit Masse verbunden). Wenn die Taste nicht gedrückt ist, so ist die Ausgangsklemme über den Widerstand R mit der Betriebsspannung verbunden. Bei hinreichend hochohmiger Belastung am Ausgang ist also die Ausgangsspannung etwa gleich der Betriebsspannung UCC. 2 Der Transistor als Schalter +UCC R S Ua Abb. 5.1: Mechanischer Schalter als Inverter Will man nun das mechanisch betätigte Bauelement, also den Schalter, durch ein elektronisches Bauelement ersetzen, so muss man sich zunächst darüber im Klaren sein, was das zu ersetzende Bauelement für Eigenschaften hat. Den Schalter können wir durch die in Abbildung 5.2 gezeigten Kennlinien beschreiben. I S geschlossen U S offen Abb. 5.2: Kennlinien eines Schalters Bei offenem Kontakt ist der Strom gleich Null, unabhängig von der Spannung. Bei einem realen Schalterkontakt darf aber sicher die Spannung nicht beliebig gross werden, da sonst ein Überschlag auftreten wird. In unserer Anwendung wird die Spannung über dem Kontakt sicher nie negativ. Die entsprechende Kennlinie für den offenen Schalterkontakt ist deshalb auch nur in dem Bereich ausgezogen gezeichnet, in dem der Schalter in unserer Schaltung betrieben wird. Der unbenutzte Kennlinienteil ist gestrichelt gezeichnet. Analog gelten die gleichen 5.1 Entwicklung eines Inverters 3 Bemerkungen für die Kennlinie des geschlossenen Schalterkontaktes; hier ist bei einem realen Schalter der maximal zulässige Strom ebenfalls begrenzt. IC IB = 100µA 15mA IB = 80µA IB = 60µA 10 IB = 40µA 5 IB = 20µA IB = 0 UCE 5 10 15 20V Abb. 5.3: Transistor- und Schalter-Kennlinien Bei der Betrachtung des Ausgangskennlinienfeldes eines Transistors stellt man sofort fest, dass die Kennlinie mit IB = 0 genau der Kennlinie des offenen Schalterkontaktes entspricht, wenn man die Kollektor-Emitter-Strecke als Schalteräquivalent betrachtet. Die Ausgangskennlinie mit IB = 100 µA entspricht dann etwa der Kennlinie des geschlossenen Schalters. Man kann also einen mechanischen Schalterkontakt ohne weiteres durch einen Transistor ersetzen, wenn sichergestellt wird, dass gewisse physikalische Grenzen (Durchbruchspannung bzw. maximaler Strom) nicht überschritten werden. Vergleichbare Grenzen hat man aber auch beim mechanischen Kontakt, so dass diese Forderung keine große Einschränkung bedeutet. +UCC RC RB Ua Ue Abb. 5.4: Grundschaltung eines Inverters Die Schaltung von Abbildung 5.4 bildet also einen Inverter. Bei einer hinreichend grossen Eingangsspannung Ue fliesst Basisstrom und der Transistor leitet. Damit wird die Ausgangsspannung sehr klein. Umgekehrt wird bei hinreichend kleiner 4 Der Transistor als Schalter Eingangsspannung der Transistor sperren und der Ausgang ist über den Widerstand RC mit der Betriebsspannung verbunden. Die etwas schwammigen Begriffe “hinreichend gross” bzw. “hinreichend klein” müssen noch präzisiert werden. Dazu betrachten wir einen abstrakten Inverter, wie er in Abbildung 5.5 gezeigt wird. INVERTER Ue Ua Abb. 5.5: Abstrakter Inverter Das Verhalten eines Inverters lässt sich durch folgende Beziehungen formal beschreiben: ! ! ! Für eine Eingangsspannung Ue kleiner oder gleich einer vorgegebenen Schranke UL gilt der Eingang als im Zustand Low (L) befindlich. Die Ausgangsspannung Ua muss dann entsprechend grösser oder gleich einer ebenfalls vorgegebenen Schranke UH sein; der Ausgang des Inverters befindet sich dann im Zustand High (H). Für eine Eingangsspannung Ue grösser oder gleich der Schranke UH gilt der Eingang als im Zustand High (H) befindlich. Die Ausgangsspannung Ua muss dann entsprechend kleiner oder gleich der Schranke UL sein; der Ausgang befindet sich dann im Zustand Low (L). Die Schranke UH muss grösser sein als die Schranke UL. Nun geht es noch darum, sinnvolle Werte für die Schranken UL und UH festzusetzen. Wenn bei einem Silizium-Transistor bei Raumtemperatur die Basis-Emitter-Spannung UBE kleiner als etwa 0.4 V wird, so nimmt der Kollektorstrom IC nahezu unmessbare kleine Werte an: der Transistor ist gesperrt. Die Schwelle UL kann also auf 0.4 V festlegt werden. Bei der Festsetzung von UH muss noch berücksichtigt werden, dass der Ausgang eines Inverters im allgemeinen wieder Eingänge von anderen Invertern bzw. ähnlichen Schaltungen treibt. Wenn bei gesperrtem Transistor am Ausgang Strom fliesst, so sinkt die Ausgangsspannung natürlich unter die Betriebsspannung ab. Daher darf die Schwelle UH nicht zu hoch angesetzt werden; ein Wert von 2 V scheint angemessen. 5.1.2 Elementare Inverterstufe Für die Dimensionierung der Inverter-Schaltung von Abbildung 5.6 kann man davon ausgehen, dass der Kollektorstrom IC beim leitenden Transistor durch die Betriebsspannung und den Kollektorwiderstand gegeben ist. 5.1 Entwicklung eines Inverters 5 +UCC RC IC RB IB Ue Ua UBE Abb. 5.6: Invertergrundschaltung Damit dieser Kollektorstrom auch wirklich fliessen kann, muss der Transistor einen notwendigen Basisstrom IB0 bekommen U CC IC I B0 = ----- = --------------β β ⋅ RC U CC I C = ----------RC In einem Experiment wollen wir ermitteln, wie sich die Ausgangsspannung des Inverters verhält, wenn am Eingang ein Basisstrom fliesst, der grösser ist als der eben definierte notwendige Basisstrom. In der folgenden Abbildung 5.7 findet man das Resultat dieser an einem Transistor des Typs 2N2219A durchgeführten Messungen für einen Bereich des Basisstroms, der sich bis zum sechsfachen des notwendigen Basisstromes erstreckt. Ua = UCE 1.0V 0.5V 1 2 3 4 5 6 m = IB/IB0 Abb. 5.7: Einfluss des Sättigungsfaktors m 6 Der Transistor als Schalter Man erkennt, dass in der Umgebung von m=1, wenn also nur gerade der notwendige Basisstrom fliesst, die Spannung sehr stark ansteigt, wenn der Basisstrom auch nur um sehr wenig sinkt. Bei einem grösseren überschüssigen Basisstrom nimmt die Ausgangsspannung noch etwas ab; es ist damit auch sichergestellt, dass die Ausgangsspannung nie über den Wert von UL ansteigt. Wenn die Situation eintritt, dass der Basisstrom grösser ist als für den fliessenden Kollektorstrom notwendig, spricht man von Sättigung (engl. saturation). Das Verhältnis von tatsächlichem Basisstrom zu notwendigem Basisstrom wird dann auch Sättigungsfaktor m genannt. Die in dieser Betriebsart auftretende Kollektor-Emitter-Spannung heisst Sättigungsspannung UCEsat. Die Sättigung eines Transistors ist aufgrund einiger Symptome erkennbar: ! Der Kollektorstrom ist nicht mehr vom Basisstrom abhängig, sondern wird nur noch durch die äussere Beschaltung festgelegt. ! Die Kollektor-Emitter-Spannung ist sehr klein. Massgebend für den Eintritt der Sättigung ist aber eine Erscheinung, die nur indirekt beobachtet werden kann: Beim gesättigten Transistor leitet die Kollektor-Basis-Diode in Flussrichtung. Wir werden diese Behauptung später noch an einigen Beispielen verifizieren. Man wird also die Inverterschaltung so dimensionieren, dass auch unter unglücklichsten Umständen (kleinste zulässige Eingangspannung und kleinste mögliche Stromverstärkung $) noch ein Sättigungsfaktor m von mindestens 5 eingehalten wird. Die kleinste Eingangsspannung, die den Transistor noch zum Leiten bringen muss, ist die Schwellenspannung UH. Wir erhalten damit für den Basisstrom folgende Beziehungen: U H – U BE m ⋅ U CC I B = ------------------------- ≥ ----------------------RB β min ⋅ R C Diese Beziehung kann nun noch nach dem Basisvorwiderstand RB aufgelöst werden: β min ⋅ R C ⋅ ( U H – U BE ) R B ≤ ---------------------------------------------------------m ⋅ U CC 5.1 Entwicklung eines Inverters 7 Zahlenbeispiel Man dimensioniere einen Inverter mit 5 V Betriebsspannung, Transistor BD237 ($ $ 25, UBEsat = 0.7 V), Kollektorstrom . 5 mA, Sättigungsfaktor m $ 5. Die vereinbarten Schwellspannungen seien UH = 2 V und UL = 0.4 V. Für den Kollektorwiderstand RC folgt sofort ein Wert von 1 kS. Für den Basisvorwiderstand RB erhält man als obere Grenze 1300 S. Wir wählen den nächsttieferen Normwert aus der Reihe E12, nämlich 1.2 kS. Damit erhalten wir die folgende Schaltung: 5V 1k Ua Ue 1k2 BD237 Abb. 5.8: Dimensionierte Inverterstufe Experiment Aufbau der Schaltung (Abbildung 5.8) und Messung von Ein- und Ausgangsspannung mit dem Oszilloskop. Als Eingangsspannung diene die Trigger-Ausgangsspannung eines Funktionsgenerators (TTL-kompatibler Ausgang). Die gemessenen Spannungsformen sind auf dem KO-Bild Abbildung 5.9 dargestellt. Ue(t) Ua(t) 6V 14V 4V 12V 2V 10V 0V 8V -2V 6V -4V 4V -6V 2V -8V 0V -10V 5µs/DIV Abb. 5.9: Spannungsverläufe beim Inverter mit BD237 -2V 8 Der Transistor als Schalter Wir erkennen, dass man diesen Transistor zwar relativ rasch vom sperrenden in den leitenden Zustand bringen kann, dass es aber ziemlich lange dauert, bis der Transistor vom leitenden in den sperrenden Zustand gebracht werden kann. In der folgenden - etwas übertrieben gezeichneten - Abbildung 5.10 sind die bei einem Inverter auftretenden Schaltzeiten definiert. U Ue(t) Ua(t) 90% 10% t ts tr td tf Abb. 5.10: Definition der Schaltzeiten ts = Speicherzeit (storage time) tr = Anstiegszeit (rise time) td = Verzögerungszeit (delay time) tf = Abfallzeit (fall time) In unserer Darstellung sind die Bezeichnungen für die verschiedenen Zeiten auf die Ausgangsspannung bezogen; in der Literatur werden dieselben Bezeichnungen auch auf den Kollektorstrom IC angewandt, dabei tauschen aber Anstiegs- und Abfallzeit ihre Bedeutung. Auffällig bei den gemessenen Spannungsverläufen (Abbildung 5.9) ist die sehr große Speicherzeit ts, die mehr als 10 µs beträgt. Sie ist eine Folge der Sättigung, weil dabei die Kollektor-Basis-Diode leitend wird. Bevor der Transistor sperren kann, müssen die Ladungsträger aus diesem leitenden pn-Übergang entfernt werden, was einige Zeit dauert, wie wir bereits bei der Untersuchung des dynamischen Verhaltens der Dioden gesehen haben. Es handelt sich beim hier im Versuch verwendeten Transistor nicht um einen schnellen Schalttransistor, sondern um einen Leistungstransistor, also etwa das Äquivalent zur Gleichrichterdiode. 5.1 Entwicklung eines Inverters 9 Wenn man davon ausgeht, dass die geschilderten Effekte die Schuld an der Speicherzeit tragen, muss man sich überlegen, durch welche schaltungstechnischen Massnahmen diese Speicherzeit verkürzt werden könnte. Es sollen hier nur zwei mögliche Ideen angedeutet werden: Beschleunigungs-Kondensator Falls ein grosser negativer Basisstrom fliessen könnte, würde die Kollektor-BasisDiode schneller ausgeräumt und der Transistor würde wesentlich schneller sperren. Dieses Konzept wird durch einen Kondensator parallel zum Basisvorwiderstand realisiert. Man überlege sich selbst die genaue Funktionsweise und führe entsprechende Experimente durch. Schottky-Diode Man kann das Problem auch so anpacken, dass man verhindert, dass die KollektorBasis-Diode jemals leitet, dass man also den Eintritt der Sättigung verhindert. Die Schottky-Diode unterscheidet sich von gewöhnlichen Dioden einerseits durch das völlige Fehlen einer Speicherladung und anderseits durch eine wesentlich tiefere Flussspannung, die nur etwa 0.3 ... 0.4 V beträgt. Wenn nun eine solche SchottkyDiode parallel zur Kollektor-Basis-Diode des Schalttransistors geschaltet wird (Abbildung 5.11), so kann die CB-Diode gar nicht mehr ins Leiten kommen, da die Schottky-Diode dank ihrer wesentlich tieferen Flussspannung zuerst leitet. Der Transistor nimmt sich genau den Basisstrom, den er benötigt, um voll zu leiten; der restliche hineingepumpte Basisstrom fliesst durch die Schottky-Diode. +5V 1k BAT81 Ue Ua 1k2 BD237 Abb. 5.11: Inverter mit Schottky-Diode Die Ausgangsspannung des Inverters im Zustand Low (Transistor leitend) wird etwas höher, da die Ausgangsspannung etwa gleich der Differenz der Flussspannungen der Basis-Emitterdiode und der Schottky-Diode ist. Beim Betrachten der gemessenen Spannungsverläufe (Abbildung 5.12) fällt sofort auf, dass die Speicherzeit nun praktisch verschwunden ist: 10 Der Transistor als Schalter Ue(t) Ua(t) 6V 14V 4V 12V 2V 10V 0V 8V -2V 6V -4V 4V -6V 2V -8V 0V -10V 5µs/DIV -2V Abb. 5.12: Spannungsverläufe beim Inverter mit Schottky-Diode Das Messresultat zeigt, dass die Hypothese für die Speicherzeit richtig war. Auch die Vermutung betreffend die leicht erhöhte Ausgangsspannung im Low-Zustand wird durch die Messung bestätigt. Anregung: Aufbau und Test der Schaltung mit der Schottky-Diode 1N5819. Man beachte vor allem die Anstiegszeit und suche eine Erklärung dafür. Dazu noch ein Hinweis: Die 1N5819 ist eine Gleichrichterdiode mit einer Sperrschichtkapazität von ca. 150 pF. Das Verfahren mit der Schottky-Diode hat in der Elektronik eine große Bedeutung erlangt. Die schnellsten Logik-Familien, die mit bipolaren Transistoren aufgebaut sind, beruhen auf dieser Technik (Schottky-TTL-Technik mit den Reihen 74Sxx, 74LSxx, 74ASxx, 74ALSxx etc.). Die Schottky-Diode kann leicht zusammen mit dem Transistor in integrierter Technik hergestellt werden und benötigt sehr wenig Chip-Fläche. Man spricht dann auch kurz von Schottky-Transistoren und zeichnet auch nur ein Symbol dafür, obwohl man streng genommen immer die Kombination Transistor und Schottky-Diode meint (Abbildung 5.13). Abb. 5.13: Schottky-Transistor 5.1 Entwicklung eines Inverters 11 Für die folgenden Schaltungen wollen wir wieder auf die Schottky-Technik verzichten, dafür aber einen Transistor einsetzen, der für diese Aufgabe besser geeignet ist, nämlich den npn-Universal-Transistor 2N2219A. Die bei diesem Transistor auftretenden Speicherzeiten sind für uns hinreichend klein und sollen nicht weiter beachtet werden. +5V 1k Ua Ue 3k3 2N2219A CL=1nF Abb. 5.14: Inverter mit kapazitiver Last In der Schaltung von Abbildung 5.14 wurde noch ein Last-Kondensator eingefügt. Dieser Kondensator soll die am Ausgang eines Inverters unvermeidlich auftretende Lastkapazität simulieren. Eine kapazitive Belastung kommt vor allem bei angeschlossenen Leitungen vor (z.B. Koaxialkabel mit ca. 100 pF/m), aber auch lange, parallel geführte Leiterbahnen auf einem Print (z.B. Bus-Leitungen) führen zu relativ grossen kapazitiven Belastungen. Der Lastkondensator ist mit 1 nF sicher übertrieben gross gewählt, dafür sind aber die auftretenden Effekte auch deutlicher sichtbar. Entsprechend der grösseren Stromverstärkung des 2N2219A ($ > 75) wurde der Basiswiderstand auf 3.3 kS vergrössert; im übrigen blieb die Schaltung unverändert. Die Messresultate (Abbildung 5.15) zeigen, dass vor allem die ansteigende Flanke einen exponentiellen Verlauf hat. Dieses Verhalten ist leicht verständlich, wenn man bedenkt, dass der Transistor sperrt und damit der Lastkondensator nur über den Kollektorwiderstand auf die Betriebsspannung aufgeladen wird. Entsprechend erhält man auch für die Zeitkonstante J = RC · CL = 1 kS · 1 nF = 1 µs, was man in der Abbildung leicht verifizieren kann. Die Steilheit der fallenden Flanke der Ausgangsspannung kann durch folgende Überlegung ermittelt werden: Die auf die Betriebsspannung aufgeladene Lastkapazität muss über den Transistor entladen werden. Da der Transistor erst sättigt, wenn seine Kollektor-Emitterspannung praktisch Null geworden ist, wird der Kollektorstrom durch $ · IB definiert. Da dieser Wert mindestens m-mal (m = Sättigungsfaktor) grösser ist als der Strom durch RC (und dieser also vernachlässigt 12 Der Transistor als Schalter werden kann), kann der ganze Strom zur Entladung des Kondensators verwendet werden. Ue(t) Ua(t) 6V 14V 4V 12V 2V 10V 0V 8V -2V 6V -4V 4V -6V 2V -8V 0V -10V -2V 5µs/DIV Abb. 5.15: Spannungsverlauf mit kapazitiver Last Wir erhalten also eine linear fallende Flanke, deren Steilheit durch die folgende Beziehung gegeben ist: dU C ⋅ ------- ≈ β ⋅ I B dt → dU β ⋅ I B ------- ≈ ------------dt C Die Flankensteilheit ist offensichtlich proportional zur Stromverstärkung der verwendeten Transistoren und umgekehrt proportional zur Lastkapazität. Ein weiterer Nachteil dieser Schaltung ist die starke Abhängigkeit der Ausgangsspannung von einem angeschlossenen Lastwiderstand (z.B. Eingangswiderstand einer nachfolgenden Stufe) im Zustand High. Diesen Nachteil kann man durch eine Ergänzung der Inverterstufe durch einen zusätzlichen Transistor beheben. Gleichzeitig wird dabei auch das Problem mit der exponentiell ansteigenden Flanke gelöst. 5.1 Entwicklung eines Inverters 5.1.3 13 Inverter mit Emitterfolger Betrachten wir die folgende, durch einen sogenannten Emitterfolger ergänzte Inverterschaltung: UCC IC2 RC IB2 T2 RB T1 Ue RE Ua RL CL Abb. 5.16: Inverter mit Emitterfolger Falls der Transistor T1 leitet (Eingang ist im Zustand High), liegt die Basis von T2 praktisch an Masse, d.h. der Transistor T2 sperrt und damit ist die Ausgangsspannung Ua = 0, also sicher im Zustand Low. Etwas komplizierter liegen die Verhältnisse bei sperrendem Transistor T1. In diesem Fall können wir bei vernachlässigtem Lastwiderstand RL mit Hilfe des Maschensatzes ansetzen: U a ≈ U CC – U BE2 – I B2 ⋅ R C Mit den Beziehungen IC2 = $ · IB2 und IC2 . IE2 = Ia erhalten wir für die Ausgangsspannung in Abhängigkeit vom Ausgangsstrom: RC U a ≈ ( U CC – U BE2 ) – I a ⋅ ------β Das ist die Gleichung eines linearen aktiven Zweipols mit der eingeprägten Spannung UCC - UBE2 und dem Innenwiderstand Ri = RC / $. Die gewöhnliche Inverterschaltung bildet bei gesperrtem Transistor einen aktiven Zweipol mit der Leerlaufspannung UCC und dem Innenwiderstand RC. 14 Der Transistor als Schalter Im Zustand High am Ausgang können die beiden Inverterstufen durch die folgenden Ersatzschaltungen beschrieben werden (Abbildung 5.17): RC RC/β UCC UCC - UBE a) b) Abb. 5.17: Ersatzschaltung ohne (a) und mit (b) Emitterfolger am Ausgang Richtig deutlich wird der Unterschied, wenn man die Ausgangskennlinien für beide Fälle aufzeichnet, wie das in Abbildung 5.18 gemacht wurde. Dabei wurden die folgenden Annahmen getroffen: UCC = 5 V, RC = 1 kS, $ = 100. U mit Emitterfolger ohne Emitterfolger 5V 4 3 2 1 I 1 2 3 4 5mA Abb. 5.18: Ausgangskennlinien Man erkennt sehr klar, dass durch den Einsatz des Emitterfolgers die Ausgangsspannung praktisch unabhängig von der Belastung wird; der Innenwiderstand ist um die Stromverstärkung kleiner geworden. Nun muss noch der Einfluss des Emitterfolgers auf die Steilheit der steigenden Flanke des Inverters bei kapazitiver Belastung untersucht werden, die schlechte Anstiegszeit (Exponentialfunktion) war ja eigentlich der Hauptgrund für den Versuch einer Schaltungsverbesserung. Da bei der ansteigenden Flanke der eigentliche Inverter-Transistor gesperrt ist, ist die massgebende Zeitkonstante das Produkt aus Lastkapazität und Ausgangswiderstand. Da wir durch Einführung des Emitterfolgers den Ausgangswiderstand massiv verkleinert haben, dürfte also die Anstiegzeit gegenüber dem einfachen Inverter ebenfalls um die Stromverstärkung $ kleiner 5.1 Entwicklung eines Inverters 15 werden; mit den damals getroffenen Annahmen (CL = 1 nF, RC = 1 kS, $ = 100) resultiert eine Zeitkonstante von J = RC · CL / $ = 10 ns, d.h. diese Zeitkonstante verschwindet gegenüber den anderen Schaltzeiten. Insofern hat also die Inverterschaltung mit nachgeschaltetem Emitterfolger alle unsere Erwartungen erfüllt: Die ansteigende Flanke sollte sehr steil sein und die Ausgangsspannung im Zustand High sollte praktisch lastunabhängig sein. Ein Testlauf mit RL = 4, RC = 1 kS, RE = 10 kS und CL = 1 nF liefert die in Abbildung 5.19 gezeigten Spannungsverläufe. Der Widerstand RE ist ja nur dazu da, dass der Emitter nicht einfach in der Luft hängt; sein Wert ist an sich unkritisch. Ue(t) Ua(t) 6V 14V 4V 12V 2V 10V 0V 8V -2V 6V -4V 4V -6V 2V -8V 0V -10V 5µs/DIV -2V Abb. 5.19: Verbesserter Inverter bei kapazitiver Belastung Die ansteigende Flanke ist wie erwartet nun sehr steil, aber mit Schrecken stellen wir fest, dass jetzt die fallende Flanke, die früher beim einfachen Inverter sehr steil war, exponentiell und sehr gemütlich gegen Null läuft. Der Grund für dieses Verhalten liegt darin, dass bei leitendem Transistor T1 der Emitterfolger T2 sperrt; damit kann sich der Lastkondensator CL nur über den Emitterwiderstand RE entladen, was zu einer entsprechend grossen Zeitkonstanten führt. Jetzt drängt sich natürlich die Frage auf, ob es nicht möglich wäre, die Vorteile der beiden Schaltungen (niederohmiger Pfad vom Ausgang gegen Masse beim gewöhnlichen Inverter, niederohmiger Pfad von Ausgang zur Betriebsspannung beim Inverter mit Emitterfolger) zu kombinieren. 16 Der Transistor als Schalter UCC RC T2 RB T1 Abb. 5.20: Kombinierte Schaltung Durch den geschickten Einsatz einer Diode (Abbildung 5.20) erreicht man diese gewünschte Kombination. Im Zustand High sperrt T1 und der Transistor T2 stellt eine niederohmige Verbindung mit der Betriebsspannung sicher (Innenwiderstand etwa RC / $). Im Zustand Low leitet T1 und verbindet den Ausgang über die Diode niederohmig mit Masse; T2 sperrt. Diese Schaltung vereint offensichtlich alle Vorzüge und soll deshalb auch noch einem Test unterzogen werden. Die Resultate, wieder mit kapazitiver Belastung, sind in Abbildung 5.21 gezeigt. Ue(t) Ua(t) 6V 14V 4V 12V 2V 10V 0V 8V -2V 6V -4V 4V -6V 2V -8V 0V -10V 5µs/DIV Abb. 5.21: Spannungsverläufe beim kombinierten Inverter -2V 5.1 Entwicklung eines Inverters 17 Einen Nachteil weist diese Schaltung trotz ihrer Schnelligkeit noch auf: Die Ausgangsspannung im Zustand Low ist klar grösser als unsere früher definierte Schwelle UL = 0.4 V. Der Ausgang unseres Inverters wäre also nicht in der Lage, einer weiteren angeschlossenen Inverterstufe ein sauberes Low zu liefern. Wir müssen deshalb die Schwelle UL neu definieren. Dazu muss aber auch die Schaltung noch etwas geändert werden, damit der Transistor bei diesem höheren Low-Pegel noch sicher sperrt. Eine Möglichkeit besteht darin, am Eingang einfach einen Spannungsteiler vorzuschalten (Abbildung 5.22). UCC RC T2 R1 T1 R2 Abb. 5.22: Endgültige Schaltung Für die Dimensionierung geht man davon aus, dass über dem Widerstand R2 beim leitenden Transistor immer die Basis-Emitter-Spannung UBE . 0.7 V liegt. Die kleinste zulässige Eingangsspannung ist UH; also liegt mindestens die Spannungsdifferenz UH - UBE über dem Widerstand R1. Damit lässt sich der Basisstrom von T1 berechnen: U H – U BE U BE m ⋅ I C I B ≈ ------------------------- – ----------- ≥ -------------R2 R1 β min Für den gesperrten Transistor muss sichergestellt sein, dass die Spannung UBE auch bei der maximal zulässigen Eingangsspannung UL kleiner als 0.4 V ist, damit der Transistor sicher sperrt. Bei als gesperrt angenommenem Transistor liegt aber ein unbelasteter Spannungsteiler vor, für den wir die folgende Ungleichung ansetzen können: UL ⋅ R2 ------------------- ≤ 0.4V R1 + R2 18 Der Transistor als Schalter Diese beiden Ungleichungen können nun nach R1 und R2 aufgelöst werden. Bei der endgültigen Bemessung der Widerstände (Runden auf Normwerte) muss sichergestellt sein, dass die obigen Ungleichungen erfüllt sind. Anregung: Man dimensioniere eine Inverterschaltung wie in Abbildung 121 unter folgenden Annahmen: UCC = 12 V, IC . 5 mA (±10%), Transistor 2N2219A ($ > 75), UL = 3 V, UH = 8 V, Sättigungsfaktor m $ 5. Die dimensionierte (Widerstände Reihe E12) Schaltung soll aufgebaut und die Einhaltung der Schwellen-Spannungen UL und UH nachgeprüft werden. Eine zweite Möglichkeit, die Schwellspannung UL anzuheben, ist in Abbildung 5.23 gezeigt: UCC RC T2 RB T3 T1 RE Abb. 5.23: Alternative Schaltung Bei dieser Variante kann UL nicht beliebig angenommen werden; bei einer Eingangsspannung von ca. 1.2 V werden die Transistoren T3 und T1 leiten. Wenn man wieder für beide Transistoren, deren Basis-Emitter-Strecken in Serie liegen, eine zulässige Spannung von je 0.4 V ansetzt, so kann man davon ausgehen, dass bei einer Eingangsspannung von weniger als 0.8 V die beiden Transistoren T3 und T1 sicher sperren. Für UL ergibt sich daraus eben dieser Wert von UL = 0.8 V. Der Transistor T2 arbeitet in diesem Fall als Emitterfolger; die Ausgangsspannung ist wieder weitgehend lastunabhängig und beträgt etwa Ua = UCC - UBE2 - UF. Die Ausgangsspannung im Zustand High ist also etwa um die Flussspannung der Diode kleiner als bei der Schaltung von Abbildung 5.22. Die Schwelle UH kann wieder weitgehend willkürlich festgelegt werden; wir wählen z.B. 2.4 V. Wenn wir für voll leitende bzw. gesättigte Transistoren für UBE einen Wert von maximal 0.7 V ansetzen, kann bei einer Eingangsspannung UH das Potential an der Basis von T3 (UB3) höchstens einen Wert von 1.4 V haben; das Emitterpotential des selben Transistors (UE3 = UB1) kann höchstens 0.7 V betragen. Der Basisstrom von T3 (IB3) beträgt demnach IB3 = (UH - 1.4 V)/RB. Der Transistor 5.2 NAND-Glieder 19 T3 sollte gesättigt sein; seine Kollektor-Emitterspannung beträgt dann etwa UCEsat = 0.2 V. Das Basispotential von T2 liegt dann auf 0.9 V; damit T2 leiten könnte, müsste es aber mindestens 1.5 V betragen (UCEsat + UF + UBE2 = 0.2 V + 0.7 V + 0.6 V). Der Transistor T2 sperrt also mit Sicherheit. Damit erhält man für den Kollektorstrom von T3: IC3 = (UCC - UB2)/RC. Damit die Sättigungsbedingung eingehalten werden kann, muss für den Basisstrom IB3 gelten: IB3 $ m·IC3/$min. Der Widerstand RE muss gemäss folgender Vorschrift gewählt werden: 0.7 V/RE + IB1 # IC3. Der Strom IB1 muss dabei so gross gewählt werden, dass T1 bei einem spezifizierten Laststrom sicher gesättigt ist. Aus den bisher aufgeführten Gleichungen können die Widerstände bestimmt werden, nachdem z.B. der Strom IC3 gewählt wurde. Gegenüber der Schaltung von Abbildung 5.22 hat die hier besprochene Schaltung wie bereits erwähnt eine etwas tiefere Ausgangsspannung im Zustand High, dafür aber auch eine um denselben Wert kleinere Ausgangsspannung im Zustand Low. Diese ausgereifte Schaltungsvariante hat sich in der Praxis durchgesetzt; die Endstufe mit den Transistoren T1 und T2 und der Diode wird auch als Totem-Pole-Stufe bezeichnet. 5.2 NAND-Glieder 5.2.1 NAND-Glied mit Dioden und Inverter Aus dem eben behandelten Inverter soll nun als logische Verknüpfung ein NANDGlied abgeleitet werden. Aus der Digitaltechnik ist ja bekannt, dass sich jede beliebige kombinatorische logische Funktion durch ausschliessliche Verwendung von NAND-Gliedern realisieren lässt; sogar Flip-Flops können durch NAND-Glieder erzeugt werden. Wenn man also ein NAND-Glied realisiert, so hat man alle denkbaren Logikschaltungen realisiert. In der Schaltung in Abbildung 5.24 wurde der Inverter durch ein vorgeschaltetes Dioden-Netzwerk ergänzt, das die NAND-Funktion erzeugt. Falls der Eingang A oder der Eingang B auf einem Potential < UL = 0.8 V liegt, fliesst der Strom durch RB aus dem entsprechenden Eingang heraus; die Diode D3 und damit T3 und in der Folge auch T1 sperren. Der Ausgang der Schaltung ist somit im Zustand High. Sind hingegen beide Eingänge (A und B) im Zustand High, so sperren die Dioden D1 und D2 und der Strom durch RB fliesst über D3 in die Basis von T3. Damit werden die Transistoren T3 und T1 gesättigt (T2 sperrt) und der Ausgang ist im Zustand Low. Aus diesen Zusammenhängen ergibt sich, dass der 20 Der Transistor als Schalter Ausgang C unter der Annahme einer positiven Logik (Low 6 0, High 6 1) die NAND-Verknüpfung der Eingänge A und B darstellt: C = !(A & B). UCC RB RC T2 A D1 D3 T3 B D4 C T1 D2 RE Abb. 5.24: NAND-Glied mit Dioden als Inverter Mitte der 60-er-Jahre gelang es, diese Schaltung zu integrieren, womit eigentlich der Siegeszug der Digitaltechnik begann. Bei der Integration wurde ein neues Bauelement - der Multi-Emitter-Transistor - eingeführt; die entstandene Technologie wurde TTL1-Technik genannt. 5.2.1 NAND-Glied in TTL-Technik UCC RB RC RH T2 A T4 T3 D C T1 B RE Abb. 5.25: NAND-Glied in TTL-Technik Man erkennt, dass an die Stelle der Dioden in der Schaltung Abbildung 5.24 nun ein Multi-Emitter-Transistor getreten ist. Eine kurze Analyse zeigt, dass dieser Transistor eigentlich gar nie als Transistor arbeiten kann; der Kollektorstrom ist ja gleich dem negativen Basisstrom von T3, es kann also eigentlich gar nie Strom in der 1. TTL, auch T2L genannt, bedeutet Transistor-Transistor-Logik 5.2 NAND-Glieder 21 “richtigen” Richtung fliessen. Man kann aber den Multi-Emitter-Transistor auch als Kombination von pn-Übergängen bzw. Dioden betrachten. Dabei stellt man fest, dass die Schaltungen Abbildung 5.24 und Abbildung 5.25 eigentlich identisch sind. Der geheimnisumwitterte Multi-Emitter-Transistor entpuppt sich bei näherem Hinsehen als einfache Dioden-Kombination. Die Bezeichnung als Transistor hat trotzdem ihre Berechtigung, da der Herstellungsprozess derselbe ist wie bei einem Transistor und man gegenüber einer klassischen Integration von Dioden sehr viel Chip-Fläche und damit Kosten einsparen kann. C E1 E2 B Abb. 5.26: Schnitt durch einen Multi-Emitter-Transistor Man sieht hier deutlich, dass die ganze “Dioden-Kombination” in Form des MultiEmitter-Transistors in einer einzigen Insel (siehe Abschnitt 4.4) realisiert werden kann. Das funktioniert bis zu Transistoren mit acht Emittern. TTL-Familien Die bekannteste Reihe von in TTL-Technik gefertigten Logikbausteinen ist die Reihe 74xx (Standard-TTL). Später gesellten sich die auch heute noch weitverbreitete Familien 74Sxx bzw. 74LSxx dazu. Der Buchstabe “S” steht dabei für Schottky-Technik, d.h. die Sättigung der Transistoren wird durch Schottky-Dioden verhindert und damit die Arbeitsgeschwindigkeit der Schaltungen bei gleichem Stromverbrauch massiv erhöht. Die Buchstaben “LS” bedeuten Low-PowerSchottky-Technik, also ein Kompromiss zwischen Stromverbrauch und Geschwindigkeit. Eine Weiterentwicklung der TTL-Technik ist die Advanced-Schottky-Technology (74ASxx bzw. 74ALSxx), die nochmals eine massive Steigerung der Geschwindigkeit brachte. Die in den Bezeichnungen verwendete Kombination “xx” steht für eine Zahl, die dann den Typ des IC’s spezifiziert; als Beispiele seien erwähnt: 7400, 74LS00, ... = 4 NAND-Glieder mit je zwei Eingängen, 7474, 74LS74, ... = 2 D-Flip-Flops mit Reset und Clear etc. 22 Der Transistor als Schalter Technische Daten Alle hier angegebenen Werte beziehen sich auf Standard-TTL bei 5 V Betriebsspannung. Die Bezugsrichtung für die Ströme ist so gewählt, dass in das Bauteil hineinfliessende Ströme positiv gezählt werden. Für die TTL-Reihe sind für die Schwellspannungen folgende Werte spezifiziert: UL = 0.8 V, UH = 2 V. Weitere wichtige Daten sind: Eingangsstrom im Zustand High (Ue > 2 V) < 40 µA Eingangsstrom im Zustand Low (Ue < 0.8 V) < -1.6 mA Ausgangsspannung im Zustand Low (Ia = 16 mA) < 0.4 V Ausgangsspannung im Zustand High (Ia = -400 µA) > 2.4 V Aus diesen Daten ist ersichtlich, dass ein Standard-TTL-Ausgang mindestens 10 Standard-TTL-Eingänge zu treiben vermag. Man spricht dann von einem fan out (oder kurz Ausgangs-Verzweigungs-Faktor) von 10. Weitere Informationen sind der Spezial-Literatur1 oder den Datenbüchern zu entnehmen. In Abbildung 5.27 ist ein Ausschnitt aus einem Datenblatt für Standard-TTL2 gegeben. In den Kurven sind die verschiedenen Kennlinien mit der Temperatur als Parameter aufgetragen. Die Reihe 74xx ist nur für einen Temperaturbereich von 0°C bis 70°C zugelassen, die ausserhalb dieses Bereiches liegenden Temperaturangaben beziehen sich auf die im übrigen identische Familie 54xx, die für Temperaturen zwischen -55°C und 125°C zugelassen ist. Die propagation delay time tpd ist der Mittelwert der Schaltverzögerungszeiten beider Flanken; gemessen wird jeweils bei den 50%-Punkten. 1. E. Kühn: Handbuch TTL- und CMOS-Schaltkreise. Hüthig, Heidelberg 1985 A. Shah, M. Saglini, Ch. Weber: Integrierte Schaltungen in digitalen Systemen (Band 1). Birkhäuser, Basel 1977 W. Jutzi: Digitalschaltungen. Springer, Berlin 1995. Das TTL-Kochbuch. Texas Instruments Deutschland, Freising 1980. 2. Quelle: TTL Pocket Guide von Texas Instruments 5.2 NAND-Glieder 23 Abb. 5.27: Ausschnitt aus dem Datenbuch 5.2.3 TTL-Inverter mit Tristate-Ausgang In der Digitaltechnik werden in gewissen Fällen (Bus-Systeme, bidirektionale Datenübertragungen etc.) Bausteine mit Tristate-Ausgängen verwendet. Diese Ausgänge können neben High und Low noch einen dritten Zustand annehmen, der “Z” genannt wird und in dem der Ausgang sehr hochohmig ist. Um einen Ausgang in diesen Zustand zu bringen, ist natürlich noch ein Steuersignal, das sog. Enable-Signal notwendig. In TTL-Technik ist die Realisierung von Tristate-Ausgängen sehr einfach. Man muss dazu nur eine einzige - in Abbildung 5.28 fett eingezeichnete Diode einzufügen, um ein TTL-NAND-Glied in einen Tristate-Inverter umzubauen. 24 Der Transistor als Schalter UCC RB D2 RC RH T2 EN T3 T4 D1 B T1 A RE Abb. 5.28: TTL-Inverter mit Tristate-Ausgang Falls der Eingang EN (der Enable-Eingang) auf High liegt, sperrt die Diode D2 und der Baustein funktioniert als gewöhnlicher TTL-Inverter mit B = !A. Falls EN auf Low liegt, so werden dadurch die Transistoren T2 und T3 gesperrt; damit sperrt auch T1 und der Ausgang wird sehr hochohmig. Das Verhalten dieses Bausteins kann durch die folgende Wahrheitstabelle beschrieben werden: EN A B L L Z L H Z H L H H H L Für weitere Einzelheiten bezüglich Eigenschaften und Anwendungen von TristateAusgängen sei auch wieder auf die reichhaltige Spezial-Literatur verwiesen. Wenn auch die meisten Bereiche der Digitaltechnik mit Bausteinen der diversen TTL-Reihen oder mit CMOS-Bausteinen abgedeckt werden, so gibt es auch hier noch einige Anwendungen für aus diskreten Bauteilen aufgebaute Schaltungen. Dazu gehören vor allem Leistungsstufen und Pegelwandler. Solche Stufen sollen im letzten Abschnitt dieses Kapitels noch vorgestellt und besprochen werden. 5.3 Leistungsstufen 5.3 25 Leistungsstufen TTL-Bausteine werden nicht nur verwendet, um logische Verknüpfungen zu realisieren; am Ausgang jeder Schaltung soll das Signal etwas bewirken, zum Beispiel sollte eine Anzeigelampe oder LED leuchten oder es soll ein Relais anziehen etc. Der Ausgang einer Standard-TTL-Stufe1 ist so beschaffen, dass im Low-Zustand ein Strom von höchstens 16 mA in den Ausgang hineinfliessen kann (Senke), im Zustand High sollte ein Ausgangsstrom von 400 µA (Quelle) nicht überschritten werden. Kleine Lasten (Betriebsspannung # 5 V, Laststrom # 16 mA) können also direkt von einem TTL-Ausgang getrieben werden; die Last muss dabei zwischen dem Ausgang und der positiven Betriebsspannung liegen (siehe Abbildung 5.29): +5V RL & & RL a) b) Abb. 5.29: a) richtige und b) falsche Anordnung einer Last Beispiele für derartige Lasten sind einerseits Leuchtdioden (mit einem der Flussspannung und dem Strom angepassten Vorwiderstand) und anderseits kleine Relais, wie beispielsweise Reed-Relais2 (Abbildung 5.30). Da es sich bei einer RelaisSpule ungeachtet des relativ hohen ohmschen Widerstandes um eine Induktivität handelt, darf die Freilaufdiode nicht vergessen werden, die die TTL-Ausgangsstufe vor den im Ausschaltmoment auftretenden Spannungsspitzen schützt. Manche dieser kleinen Relais sind mit eingebauter Freilaufdiode lieferbar (auf richtige Polung achten!). 1. Für die anderen TTL-Familien (LS, AS, ALS etc.) gelten andere Maximalwerte für die Ausgangsströme; man vergleiche dazu die Datenbücher. 2. Reed-Relais sind Relais, bei denen die Kontakte in einem gasgefüllten Glasröhrchen eingeschmolzen sind, das seinerseits den “Kern” einer Zylinderspule bildet. 26 Der Transistor als Schalter +5V & Relais: 5V, 500Ω Abb. 5.30: Relais an TTL - Ausgang 5.3.1 TTL-Leistungsstufen mit Open Collector Ausgang Innerhalb der TTL-Reihen sind Gatter mit speziellen Ausgangsstufen erhältlich, nämlich mit den sogenannten Ausgängen mit offenem Kollektor (open collector output), abgekürzt OC-Ausgang. Der Name wird sofort klar, wenn man die Innenschaltung sieht: UCC T1 T2 T4 T3 Abb. 5.31: Schema des Bausteins 7407 (open collector buffer) Der Kollektor des Ausgangstransistors T4 bildet den Ausgang der Schaltung. Man kann diesen Ausgang nicht ohne weiteres mit dem Eingang einer weiteren TTLStufe verbinden, denn die Ausgangssignale sind hier nicht mehr definierte Spannungspegel, sondern der Ausgangstransistor leitet oder er sperrt. Damit ein OCAusgang wieder ein verarbeitbares Signal liefert, muss er über einen sogenannten pull up Widerstand mit der Betriebsspannung verbunden werden, der den Ausgang bei gesperrtem Transistor zur Betriebsspannung “hochzieht”. Üblicherweise werden aber solche OC-Ausgänge als Leistungsstufen verwendet. Die zulässige Kollektorspannung beim als Beispiel verwendeten 74071 beträgt immerhin 30 V, der maximale Strom im Zustand Low etwa 40 mA. Mit einer solchen OC-Stufe können also schon viele (auch grössere) Relais geschaltet werden. Falls noch grössere 5.3 Leistungsstufen 27 Spannungen und/oder Ströme gefordert sind, muss man auf externe Schaltungen ausweichen. 5.3.2 Darlington-Treiber Abb. 5.32: Darlington-Treiber Eine solche externe Treiberstufe gibt es als Multipack (7 Treiber in einem IC) zu kaufen: die Reihe ULN200x. Es handelt sich um Darlington-Treiber, so genannt nach der Transistor-Kombination, bei der der Emitterstrom des einen Transistors den Basisstrom des anderen bildet und so die resultierende Stromverstärkung auf Werte von über 1000 ansteigt. Der Typ ULN2003A hat Eingänge, die an TTLSchaltungen angepasst sind; der Ausgangstransistor sperrt bis maximal 50 V und der Ausgangsstrom kann maximal 500 mA betragen. Interessant sind die mitintegrierten Freilaufdioden, die darauf hindeuten, dass der Hersteller das Hauptanwendungsgebiet bei Relaistreibern sieht. Von dieser Reihe gibt es auch Typen, die an andere Eingangsspannungsbereiche angepasst sind oder solche, die auch höhere Spannungen (bis 90 V) aushalten. Für noch grössere Ströme müssen diskrete Schaltungen entwickelt werden, die vom Aufbau her unseren bisherigen Inverterschaltungen entsprechen. Für bestimmte Zwecke, wie z.B. für die Ansteuerung von Schrittmotoren, sind auch hier integrierte Leistungstreiber verfügbar. 1. Vorsicht! Nicht alle OC-Ausgänge der TTL-Reihe sind mit 30 V und 40 mA belastbar. In jedem Fall ist das detaillierte Datenblatt zu konsultieren. 28 Der Transistor als Schalter 5.4 Übungsaufgaben und Kontrollfragen 5.4.1 Übungsaufgaben 12. Dimensioniere die nachstehende Schaltung (Abbildung 5.33) unter den folgenden Annahmen: Transistoren 2N2219A, UCC = 24 V, IC = 2 mA (±10%), Schwellspannungen UL = 2 V, UH = 10 V, Sättigungsfaktor m $ 5. Es dürfen nur Widerstände der Reihe E12 verwendet werden. UCC RC T2 R1 T1 R2 Abb. 5.33: Schaltung zu Aufgabe 12 13. Wie gross ist der fan out der Schaltung von Abbildung 5.8 (UL = 0.4 V, UH = 2 V)? Anders gefragt, wie viele gleichartige Eingänge wie sie in Abbildung 5.8 dargestellt sind, kann die Ausgangsstufe maximal treiben? 14. Gegeben: Schaltung UCC RC T2 RB T3 T1 RE Abb. 5.34: Schaltung zu Aufgabe 14 5.4 Übungsaufgaben und Kontrollfragen 29 Dimensioniere die Schaltung von Abbildung 5.34 für eine Betriebsspannung von 5 V unter der Annahme, dass der Ausgangstransistor T1 maximal einen Strom von 20 mA schlucken muss. Als Transistoren werden Schalttransistoren des Typs BSX20 eingesetzt, deren Daten hier gegeben sind: ICmax = 500 mA, 40 # $ # 120. Für die Rechnung gehe man von folgenden Werten aus: UCEsat # 0.2 V, UBEakt = 0.6 V, UBEsat = 0.7 V, UH = 2.4 V, UL = 0.8 V. Bei gesättigten Transistoren sei der Sättigungsfaktor m $ 5. 15. Bei der Schaltung von Abbildung 5.35 wurde die Reaktion der Schaltung auf einen Spannungssprung am Eingang von 5 V (steigende Flanke) gemessen. +5V 1k2 Ua Ue 3k9 2N2219A CL=10nF Abb. 5.35: Schaltung zu Aufgabe 15 Die Messung ergab den in Abbildung 5.36 gezeigten Verlauf der Ausgangsspannung. Man berechne die Stromverstärkung $ des Transistors aus diesen Angaben. Abb. 5.36: Verlauf der Ausgangsspannung (Aufgabe 15) 30 Der Transistor als Schalter 16. Man entwerfe einen Pegelwandler, der TTL-Signale (UL = 0.8 V, UH = 2 V) auf den Bereich 0 .. -12 V umsetzt. Ein High am Eingang soll dabei eine Ausgangsspannung von # -8 V bewirken; bei einem Low am Eingang soll die Ausgangsspannung sicher $ -1 V sein. Gesucht ist eine fertig dimensionierte Schaltung, die mit gesättigten Transistoren arbeitet (m $ 5). Es gibt übrigens ausser den npn-Transistoren auch noch pnp-Typen. 17. an analysiere die Wirkungsweise des nachstehend gezeichneten astabilen Multivibrators: 5V RC T1 RB RB C C RC T2 Ua Abb. 5.37: Astabiler Multivibrator Gesucht ist der Verlauf der Ausgangsspannung, der beiden Basisspannungen sowie die Periodendauer des Signals. Zum Knacken dieser Nuss empfiehlt es sich, einerseits etwas in der Literatur zu stöbern, anderseits kann auch eine Simulation der Schaltung etwas Licht ins Dunkel bringen. Man kann dann versuchen, die simulierten Spannungsverläufe zu erklären und so zu allgemeinen Ausdrücken z.B. für die Frequenz zu kommen. 5.4.2 Fragen zur Lernkontrolle Es wird erwartet, dass die folgenden Fragen ohne im Buch nachzuschlagen beantwortet werden können. 1. Wozu dient die Festlegung der Spannungen UH und UL? 2. Weshalb muss ein Transistor im Schalterbetrieb mehr Basisstrom bekommen als für den tatsächlich fliessenden Kollektorstrom notwendig wäre? 3. Welches sind die Kennzeichen der Sättigung? 5.4 Übungsaufgaben und Kontrollfragen 31 4. Weshalb kann man durch eine Schottky-Diode die Speicherzeit einer Inverterschaltung massiv verkleinern? 5. Was ist der Vorteil des Multiemitter-Transistors? 6. Wie gross ist der fan out bei Standard-TTL? 7. Weshalb sollten Lasten am Ausgang von logischen Schaltungen an der Betriebsspannung und nicht an Masse liegen?