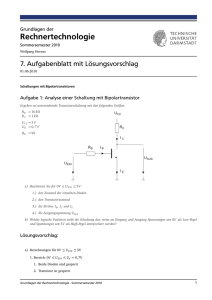

Aufgaben und Lösungen

Werbung

Aufgaben und Lösungen Kapitel 1 – 10 7. Juni 2005 Kapitel 1 Aufgabe 1.1 Bei einer Ge-Probe liegt das Ferminiveau 0,15eV unter der Leitungsbandkante. a) Berechnen Sie die Wahrscheinlichkeit, mit welcher die Valenzbandkante und die Leitungsbandkante von Elektronen besetzt sind und vergleichen Sie die Werte mit den Wahrscheinlichkeiten für einen Intrinsic-Halbleiter. (kT = 26meV =∃ Zimmertemperatur) b) Berechnen Sie die Elektronendichte im Leitungsband und die Löcherdichte im Valenzband für den obigen Halbleiter. Über welche Beziehung sind die aus b) erhaltenen Ergebnisse direkt miteinander verknüpft? Aufgaben und Lösungen 2 Lösung zur Aufgabe 1.1: W W 0,15 eV WC WF F(WC ) Wg =0,66 eV F(WV ) WV 0 0,5 1 F(W) Bild L: 1.1 a) Besetzungswahrscheinlichkeit für Elektronen F (WC ) = 1 1+ e WC − W F kT 1 F (WV ) = 1+ WV −W F e kT F (WV ) ≈ 1 − e − 0 , 51eV 0 , 026 eV 1 = 1+ e ≈1− e 0 ,15 eV 0 , 026 eV − = 3,11 ⋅ 10 −3 (W F −WV ) kT = 1 − 3, 03 ⋅ 10 − 9 Besetzungswahrscheinlichkeit durch Löcher F (WV ) ≈ 1 − F (WV , Elektr.) = 3, 03 ⋅ 10 b) −9 Elektronen- und Löcherdichte n o = N C F (WC , Elektr.) = 1, 04 ⋅ 1019 cm −3 ⋅ 3,11 ⋅ 10 −3 = 3, 23 ⋅ 1016 Elektr. / cm 3 18 po = NV F (WV , Löcher ) = 6, 0 ⋅ 10 cm n o p o = ni2 ni = −3 ⋅ 3, 03 ⋅ 10 n o p o = 2, 4 ⋅ 1013 cm −3 −9 9 = 18,18 ⋅ 10 Löcher / cm 3 Aufgaben und Lösungen 3 Aufgabe 1.2 Gegeben ist ein n-Typ Si-Halbleiter, dessen Donatorniveau 0,05eV unter der Leitungsbandkante liegt. Die Dichte der ionisierten Donatoratome ND+ (Bild 1.11) beträgt + N D = N D [1 − F(W D )] ⎡ ⎢ 1 = N D ⎢1 − WD − WF 1 ⎢ 1 + exp ⎣⎢ 2 kT ⎤ ⎥ ⎥ ⎥ ⎦⎥ wobei [1 - F(WD)] die Wahrscheinlichkeit für das Fehlen eines Elektrons ist und der Faktor 1/2 den einfach ionisierten Donator berücksichtigt ⏐MÜLL⏐. a) Berechnen Sie bei Raumtemperatur die Ferminiveaus bei folgenden Dotierungen: ND = 1016cm-3, 1018cm-3 und 1019cm-3. Dabei wird vorausgesetzt, dass 100%ige Ionisation der Donatoren vorliegt. b) Verwenden Sie dann die berechneten Ferminiveaus, um die Voraussetzung der 100%igen Ionisation zu überprüfen. Lösung zur Aufgabe 1.2: Vorgehensweise: a) Bestimmung von WC - WF bei Annahme 100%ige Ionisation b) Überprüfung der Annahme W WC WD WF 0,05 eV WC - WF WV Bild L: 1.2 no = N C e − (WC −W F ) kT Annahme: 100%ige Ionisation ⇒ WC − W F = kT ln NC no Aufgaben und Lösungen 4 N D =ˆ n o WC − W F WD − WF = WC − W F − 0, 05eV 100%ige Ionisation 1016 cm-3 0,206 eV 0,156 eV 1018 cm-3 0,0866 eV 0,0366 eV 1019 cm-3 0,0268 eV -0,0232 eV Dichte der ionisierten Donatoratome N D = N D [1 − F (W D ) ] + hierbei beschreibt [1-F(WD] die Wahrscheinlichkeit für das Fehlen eines Elektrons ⎡ ⎢ 1 + N D = N D ⎢1 − W ⎢ D −W F ⎢ 1 + 1 e kT ⎢⎣ 2 ⎤ ⎥ ⎥ ⎥ ⎥ ⎥⎦ ND WD - WF ND+ [cm-3] [eV] [cm-3] 1016 0,156 1016[1 - 0,049] = 1016 1018 0,0366 1018 [1 - 0,328] = 0,63⋅1018 1019 -0,0232 1019 [1 - 0,83] = 0,17⋅1019 D.h. ab ND = 1018cm-3 keine 100%ige Ionisation mehr Exakter Lösungsansatz: + + po no = N D elk. Neutralität (WC −W F ) kT = ND NC e − ⎡ ⎢1 − 1 W −W F ⎢ 1+ 1 e D ⎢⎣ kT 2 (W F −WV ) ⎤ ⎥ + N e− kT V ⎥ ⎥⎦ Numerische Lösung: 1. Lage des Ferminiveaus 2. aus Dichtebeziehung Ladungsträgerkonzentration Aufgaben und Lösungen 5 Aufgabe 1.3 Gegeben ist ein Si-Halbleiter mit 5⋅1016 Boratome/cm3 und 1015 Phosphoratome/cm3. Berechnen Sie bei Raumtemperatur: a) die Elektronen- und Löcherkonzentration; b) die Leitfähigkeit und c) den Abstand des Fermi- zum Intrinsic-Niveau. Die Beweglichkeiten sind dem Bild 1.17b zu entnehmen. Lösung zur Aufgabe 1.3 a) Elektronen- und Löcherkonzentration Bor; NA = 5⋅1016cm-3 Phosp.; ND = 1015cm-3 NA - ND = 4,9⋅1016cm-3 » ni = 1,45⋅1010cm-3 p-Typ-Halbleiter 100%ige Ionisation ppo = NA - ND = 4,9⋅1016cm-3 npo = ni2/(NA-ND) = 4,29⋅103cm-3 b) Leitfähigkeit σ = q( µ p p + µ n n) σ = 1, 6 ⋅ 10 −19 As ( 400 cm 2 V ⋅s 4,9 ⋅ 10 16 cm −3 2 3 −3 + 1000 cm 4, 29 ⋅ 10 cm ) V ⋅s σ = 3,13( Ωcm ) −1 c) Abstand Fermi- zu Intrinsicniveau p po = n i e (Wi −W F ) / kT Wi − W F = kT ln p po ni Wi − W F = 390 meV = 26 meV ln 4,9 ⋅ 1016 cm − 3 1, 45 ⋅ 1010 cm − 3 Aufgaben und Lösungen 6 Aufgabe 1.4 In einem sehr langen homogen dotierten p-Typ Silizium Halbleiter werden an der Stelle x = 0 bei Raumtemperatur (300K) kontinuierlich Elektronen injiziert. (Entspricht einem pn-Übergang, bei dem der n-Bereich nicht gezeigt und sehr hoch dotiert ist). p - Typ x 0 An der Stelle x = 0 ist die Elektronendichte n(0) = 1010cm-3. Die Elektronen- und Löcherbeweglichkeiten betragen µn = 1200cm2/Vs und µp = 400cm2/Vs. Der Halbleiter hat eine Dotierung von NA = 1015cm-3. Die Diffusionslänge der Elektronen beträgt 22µm. a) Zeichnen Sie den Verlauf von Elektronenstromdichte Jn und Löcherstromdichte Jp als Funktion des Ortes. b) Wie groß ist die Gesamtstromdichte? c) Welchen Wert hat die elektrische Feldstärke für x → ∞ ? Hinweis: Zur Lösung der Aufgabe ist das Studium "Vertiefende Betrachtung zum Experiment" (Kap.1.5) erforderlich. Lösung zur Aufgabe 1.4: I - E+ In (0) In (x) Ip (x) νp νn Drift 0 p - Typ - H. L. x Bild L: 1.4 J n = qµ n nE + qD n ∂n ∂x Drift vernachlässigbar bei ∂p Minoritätsträger J p = qµ p pE − qD p ∂x J = Jn + J p an der Stelle x = 0: J = J n ( 0 ) + J p ( 0 ) = qD n ∂n ∂x x = 0 123 0 Aufgaben und Lösungen 7 Aus "Vertiefende Betrachtung zum Experiment" (Kap.1.5) und in Analogie zu Beziehung (1.70): −x / L n n ′p ( x ) = n ′p ( 0 ) e ∂n ′p − x / Ln 1 =− n ′p ( 0 ) e ∂x Ln ∂n ′p ∂x 1 n ′ (0) Ln p =− x =0 J = − qDn 1 n ′p ( 0 ) = − q kT µ n 1 ( n p ( 0 ) − n po ) q Ln Ln 2 5 n po = ni / N A = 2,1 ⋅ 10 cm −3 2 J = −1, 6 ⋅ 10 −19 As ⋅ 26 ⋅ 10 − 3 V ⋅ 1200 cm V ⋅s J = −22, 7 1 22 ⋅ 10 −4 cm (1010 − 2,1 ⋅ 10 5 ) cm − 3 µA cm 2 Feldstärke bei x → ∞ ? J n = qµ n nE + qDn ∂n ∂x ( Diff. − Term vernachlässigbar) ∂p J p = qµ p pE − qD p ∂x pp » np mit (Diff. − Term vernachlässigbar) ist Jp » Jn J x → ∞ = J p = qµ p pE E = J qµ p p = − 22, 7 ⋅ 10 −6 A / cm 2 1, 6 ⋅ 10 −19 A ⋅ 400 cm 2 / V ⋅ s ⋅ 1015 cm − 3 E = −3,54 ⋅ 10 − 4 V / cm Aufgaben und Lösungen 8 Aufgabe 1.5 Mit dieser Aufgabe soll der Begriff Lebensdauer vertiefend betrachtet werden. Dazu wird das folgende Experiment analysiert. In der gezeigten n-Typ Siliziumprobe werden Majoritäts- und Minoritätsträgerdichten gegenüber denjenigen im thermodynamischen Gleichgewicht zu gleichen Teilen erhöht bzw. erniedrigt. n - Typ x 0 pn p pn L p p L p no 0 no x p L 0 p L x Bild A: 1.5 Die Erhöhung kann z.B. durch Lichtbestrahlung erfolgen, wodurch ElektronenLochpaare durch das Aufbrechen kovalenter Verbindungen entstehen. Die Ursache zur Erniedrigung der Ladungsträgerdichten ist dagegen nicht so einfach zu beschreiben, was jedoch für das Experiment von untergeordneter Bedeutung sein soll. Wird nun die Ursache, die die Ladungsträgerdichten verändert, beseitigt, so stellt sich die Frage, wodurch und wie der Ausgleichsvorgang zum thermodynamischen Gleichgewicht erfolgt. Aufgaben und Lösungen 9 Lösung zur Aufgabe 1.5 Ausgangspunkt ist die Kontinuitätsgleichung ∂p n = G − R. ∂t Hierbei wurde angenommen, dass keine örtliche Stromänderung in der als homogen angenommenen Probe auftritt. Die Nettorekombinationsrate bei schwacher Injektion beträgt (Gl. 1.65) p′ U = R − G = 1 ( p n − p no ) = n . τp τp Damit ergibt sich aus der Kontinuitätsgleichung der Zusammenhang ∂p n′ ∂t = p n′ τp . Mit den Randbedingungen p'n(t=0) = p'L liefert die Lösung der Differentialgleichung p n′ ( t ) = p ′L e −t / τ p die Beschreibung des Ausgleichvorgangs zum thermodynamischen Gleichgewicht, wobei τp eine Zeitkonstante ist, die die Minoritätsträger-Lebensdauer beschreibt. Abhängig vom Experiment kann p'L größer oder kleiner 0 sein. Ist p'L > 0 und damit U > 0, so geschieht der Ausgleichsvorgang pn pn 0 pL R>G 0 τp t p τp t R<G L Bild L: 1.5 durch überwiegende Rekombination. Ist dagegen p'L < 0 und U < 0, so findet der Ausgleichsvorgang durch überwiegende Generation statt. Aufgaben und Lösungen 10 Kapitel 2 Aufgabe 2.1 Ein abrupter pn-Si-Übergang hat die Dotierungen NA = 1015cm-3 und ND = 2⋅1017cm-3. a) Berechnen Sie die Diffusionsspannung bei Raumtemperatur. b) Bestimmen Sie die Weite der Raumladungszone und c) die entsprechende maximale Feldstärke für UPN = 0V und - 10V. Lösung zur Aufgabe 2.1 a) Diffusionsspannung (built-in voltage) bei RT φ i = φ t ln N AND 2 ni = 26 mV ln 10 15 cm −3 ⋅ 2 ⋅ 10 (1, 45 ⋅ 10 10 cm 17 cm −3 −3 2 ) φ i = 0, 717V b) Weite der Raumladungszone bei UPN = 0V und UPN = -10V w= w= 2ε o ε Si 1 (φ − U PN ) q NA i 2 ⋅ 8,854 ⋅ 10 −14 1, 6 ⋅ 10 As / V ⋅ cm ⋅ 12 −19 ND » NA da As 1 10 15 cm −3 ist ( 0 , 717V − U PN ) w(U PN = 0V ) = 0,97 µm w(U PN = −10V ) = 3, 77 µm c) Maximale Feldstärke bei UPN = 0V und UPN = -10V φ i − U PN = − EM = − E M (U PN = 0V ) = − 1 E ⋅w 2 M 2 (φ i − U PN w 2 ( 0, 717V ) 97 ⋅ 10 −6 cm ) E M (U PN = −10V ) = −56,8 ⋅ 10 V / cm 3 3 = −14, 78 ⋅ 10 V / cm Aufgaben und Lösungen 11 Aufgabe 2.2 Im thermodynamischen Gleichgewicht kompensieren sich die Drift- und Diffusionsströme beim pn-Übergang. Bestimmen Sie ungefähr eine dieser Stromdichtekomponenten, wenn NA = 1018cm-3, ND = 5⋅1015cm-3 und die Weite der Raumladungszone 46⋅106 cm beträgt. Die Beweglichkeit der Löcher soll 500 cm2/Vs betragen. Lösung zur Aufgabe 2.2: I Diff = − qD p I Diff ≈ − qD p dp ∆p ≈ − qD p ∆x dx p po − p no w mit: D p = φ t µ p = 26 mV ⋅ 500 cm 2 / V ⋅ s = 13cm 2 / s mit ppo » pno I Diff ≈ − qD p p po w = 1, 6 ⋅ 10 I Diff ≈ −45217 A / cm −19 As ⋅ 13 cm s 2 10 18 cm −3 46 ⋅ 10 − 6 cm 2 Diese enorm große Diffusionsstromdichte wird kompensiert durch eine gleich große Driftstromdichte. Aufgaben und Lösungen 12 Aufgabe 2.3 In Kapitel 2.1 ist ein inhomogener n-Typ-Halbleiter beschrieben. Geben Sie qualitativ das Strom-Spannungsverhalten wieder. Kommt es zu einer Gleichrichterwirkung? Lösung zur Aufgabe 2.3 Zum Vergleich: a) pn-Übergang I I n p xp xn i n νn np pn xp xn Injektion nn pp νp n po x νn n p νp nn pp xn + UPN <0V UPN >0V νp xp i x + n p n p pno x νn npo νp pno np xp xn Extraktion pn x Bild L: 2.3.1 Strom der jeweiligen Majoritätsträger ist gleich dem der entsprechenden Minoritätsträger. D.h. In im n-Typ ist gleich In im p-Typ und Ip im p-Typ ist gleich Ip im n-Typ. In Durchlassrichtung können die Minoritätsträgergradienten d.h. Minoritätsträgerströme bis zum thermischen Durchbruch erhöht werden. Aufgaben und Lösungen 13 In Sperrrichtung kann der Minoritätsträgergradient an den Rändern der Raumladungszone bis auf Null absinken. Weitere Veränderung der Gradienten und damit Minoritätsträgerströme ist nicht möglich. Der Strom sättigt bei sehr kleinen Werten. b) n+n-Übergang n+ n + RLZ n p νp nn νp xi + RLZ n p νn νn n+ n νn νn νp pn x νp xi nn pn x Bild L: 2.3.2 Grundsätzlich: Majoritätsträgerbauelement, bei dem die Majoritätsträger in beiden Richtungen wandern können. Die Ladungsträgeränderungen an den Grenzen der Raumladungszone sind vernachlässigbar. Somit resultiert ein Verhalten wie ein Widerstand. Aufgaben und Lösungen 14 Aufgabe 2.4 Bestimmen Sie für den n+p-Übergang die Sperrschichtkapazitäten pro Fläche und Raumtemperatur am Rand und am Boden bei UPN = 0V. Nehmen Sie dabei als Näherung das gezeigte Stufenprofil an. 0,2um A ND ~ ~ Bild A: 2.4 A NA ~ ~ 20 -3 17 ND =10 cm-3 ND =10 cm ND Stufenprofil 17 NA=10 cm-3 Aufgaben und Lösungen 15 Lösung zur Aufgabe 2.4 φ i = φ t ln N AND w= ; 2 ni 2ε o ε Si ⎛ 1 1 ⎜⎜ + q ND ⎝ NA ⎞ ⎟⎟φ i ⎠ Rand: φ i = 26 mV ln w= 10 20 ⋅ 10 17 (1, 45 ⋅ 10 ( cm 10 −3 2 ) −3 2 cm = 0,998V ) As Vcm ⎛⎜ 1 + 1 ⎜ 20 −19 17 ⎝ 10 1, 6 ⋅ 10 As 10 −14 2 ⋅ 11,9 ⋅ 8,85 ⋅ 10 ⎞ 1 ⎟⎟ 0, 998V ⎠ cm − 3 w = 0 ,114 µm As Vcm = 92, 4 nF C ′j = = w cm 2 1,14 ⋅ 10 − 5 cm pF nF C *j = C ′j ⋅ x j = 92, 4 ⋅ 0, 2 ⋅ 10 − 4 cm = 1,85 2 cm cm ε o ε Si 11,9 ⋅ 8,85 ⋅ 10 −14 Boden: φ i = 26 mV ln w= 10 17 ⋅ 10 17 (1, 45 ⋅ 10 2 ⋅ 11,9 ⋅ 8,85 ⋅ 10 1, 6 ⋅ 10 ( cm 10 cm −3 2 ) −3 2 = 0 ,819V ) −14 −19 As / Vcm ⎛ 1 1 + ⎜⎜ 17 ⎝ 10 As 1017 w = 0 ,147 µm C ′j = As Vcm = 71, 7 nF 1, 47 ⋅ 10 − 5 cm cm 2 11,9 ⋅ 8,85 ⋅ 10 −14 ⎞ 1 0,819V ⎟⎟ ⎠ cm − 3 Aufgaben und Lösungen 16 Aufgabe 2.5 Am pn-Übergang der Diode ist eine Diffusionsspannung wirksam. Entsteht ein Stromfluss, wenn die Diode von außen kurzgeschlossen wird? Begründen Sie die Aussage. Lösung zur Aufgabe 2.5 Es kommt zu keinem Gleichstromfluss. Nach einigen ps stellt sich thermodynamisches Gleichgewicht ein. Siehe hierzu Kapitel 2.3.4 Aufgaben und Lösungen 17 Aufgabe 2.6 Im Folgenden soll ein Basis-Emitterübergang bei Raumtemperatur analysiert werden. Die Daten sind: ND (Emitter) = 5⋅1019 cm-3 ; w'n = 0,2 µm NA (Basis) = 5⋅1017 cm-3 ; w'p = 0,2 µm Dp = 12 cm2/s ; Dn = 21 cm2/s Emitterfläche A = 1 µm2 UPN = 0,80 V Bestimmen Sie: Die Weite der Raumladungszone, den Sperrstrom IS; Durchlassstrom I sowie die Sperrschicht- und Diffusions-Kapazität bei UPN = 0,80 V und UPN = 0V Lösung zur Aufgabe 2.6: a) mit ND > NA Weite der Raumladungszone: w= 2ε o ε Si 1 (φ − U PN NA i q φ i = φ t ln N AND ); = 26 mV ln 2 ni 5 ⋅ 10 19 cm −3 (1, 45 ⋅ 10 ⋅ 5 ⋅ 10 10 cm 17 cm −3 −3 2 ) φ i = 1, 02V w= 2 ⋅ 8,854 ⋅ 10 1, 6 ⋅ 10 −19 −14 As / Vcm ⋅ 11,9 As ⋅ 5 ⋅ 10 17 cm −3 0 , 2V w = 2 , 29 ⋅ 10 − 6 cm = 22, 9 ⋅ 10 − 6 mm = 22,9 nm b) Sperrstrom: mit ND > NA ⎛ Dp 1 ⎛ Dp ⎞ D D 1 ⎞⎟ 2 I S = qA⎜ + n p no + n n po ⎟ = qA⎜ n ⎜ w′ N ⎜ w′ ⎟ w ′p w ′p N A ⎟ i n n D ⎝ ⎠ ⎝ ⎠ D 1 2 I S ≈ qA n n w ′p N A i Aufgaben und Lösungen I S ≈ 1, 6 ⋅ 10 18 −19 As ⋅ 10 −8 cm 2 2 21cm / s 1 0, 2 ⋅ 10 − 4 cm 5 ⋅ 1017 cm − 3 I S ≈ 7 , 0 ⋅ 10 −19 A c) Durchlassstrom I 800 mV U PN / φ t −19 I = I S (e − 1) = 7 , 0 ⋅ 10 A( e 26 mV − 1) I = 0,16 µA d) Sperrschicht- und Diffusionskapazität bei UPN = 0,8V ε ε 8,854 ⋅ 10 −14 As / Vcm ⋅ 11,9 C j = A o Si = 10 −8 cm 2 w 2, 29 ⋅ 10 − 6 cm C j = 4, 6 ⋅ 10 −15 F = 4, 6 fF τ /φ U C d = T I S e PN t φ t τT = τ n mit In I I D p n2 i I p = qA ′ wn N D τT ≈ τ n Cd = D n ni2 I n = qA w ′p N A ND > NA und e) Ip +τ p ( w ′p ) 2 τn = 9 , 5 ⋅ 10 −12 26 ⋅ 10 −3 2 Dn s V 7 ⋅ 10 = −19 ( 0, 2 ⋅ 10 −4 cm ) 2 ⋅ 21cm 2 / s 2 = 9,5 ps 800 mV A e 26 mV = 5,9 fF Sperrschicht- und Diffusionskapazität bei UPN = 0V C j = 2 fF C d = 2,5 ⋅ 10 −28 fF ≈ 0 (1, 45 ⋅ 10 10 cm −3 ) 2 Aufgaben und Lösungen 19 Aufgabe 2.7 In einer integrierten Schaltung soll eine Versorgungsleitung durch einen möglichst großen Kondensator gegen Kopplungen unempfindlich gemacht werden. Hierzu wird ein nWannen/p-Substrat Übergang (Bild A: 2.7) verwendet. 2 um UPN n - Wanne 300 um p - Substrat Bild A: 2.7 Daten: ND = 5⋅1018 cm-3 ; UPN = 0,8 V ; NA = 1017 cm-3 ; Dp = 12 cm2/s ; Dn = 21 cm2/s A = 0,1 mm2 . Bestimmen Sie bei Raumtemperatur: Den fließenden Gleichstrom I, sowie die Diffusions- und Sperrschichtkapazität bei UPN = 0,8 V Lösung zur Aufgabe 2.7: a) Gleichstrom I = Ip + In ⎞ U ⎛ Dp D /φ I = qA⎜ p no + n n po ⎟ ⎛⎜ e PN t − 1 ⎞⎟ ⎟⎝ ⎜ w′ w ′p ⎠ ⎠ ⎝ n D n ni2 ⎛ U /φ I p = qA ⎜ e PN t − 1 ⎞⎟ ′ wp N A ⎝ ⎠ I p = 1, 6 ⋅ 10 −19 I p = 5, 43mA As 0,1 ⋅ 10 −2 cm 2 w ′p ≈ w p = 298 µm ≈ 0, 03cm 10 −3 21cm 2 / s (1, 45 ⋅ 10 cm ) 0, 03cm 1017 cm − 3 2 ⎛ 800 ⎞ ⎜ e 26 − 1 ⎟ ⎜⎜ ⎟⎟ ⎝ ⎠ Aufgaben und Lösungen 20 Dp n2 i ⎛ U PN / φt − 1 ⎞⎟ I n = qA ⎜e wn′ N D ⎝ ⎠ −19 I n = 1, 6 ⋅ 10 As 0,1 ⋅ 10 −2 cm wn′ ≈ wn = 2 µm −3 10 2 12 cm / s (1, 45 ⋅ 10 cm ) 2 2 ⋅ 10 −4 cm 5 ⋅ 10 18 cm −3 2 ⎛ 800 ⎞ ⎜ e 26 − 1 ⎟ ⎜⎜ ⎟⎟ ⎝ ⎠ I n = 9 ,3mA I = I p + I n = 14 , 7 mA b) Sperrschichtkapazität N AND φ i = φ t ln n i2 = 26 mV ln 1017 cm −3 5 ⋅ 1018 cm −3 (1, 45 ⋅ 1010 cm − 3 ) 2 φ i = 0,92V mit ND > NA w≈ 2ε o ε Si ≈ q 1 (φ − U PN ) NA i 2 ⋅ 8,854 ⋅ 10 −14 As / cm ⋅ 11,9 1, 6 ⋅ 10 −19 As ⋅ 10 17 cm −3 0,12V = 3,9 ⋅ 10 − 6 cm = 39 nm −14 ε ε 8,854 ⋅ 10 As / Vcm ⋅ 11,9 C j = A o Si = 0,1 ⋅ 10 − 2 cm 2 −6 w 3, 9 ⋅ 10 cm C j = 2, 7 ⋅ 10 −10 F = 0, 27 nf c) Diffusionskapazität Cd = τT τ /φ U I S e PN t ≈ T I φt φt τT = τ n In I +τ p Ip I Aufgaben und Lösungen τn = τp = ( w ′p ) 2 2 Dn ( wn′ ) 2 2D p 21 ( 0, 03cm ) = = 2 = 21, 43 µs 2 ⋅ 21cm 2 / s ( 2 ⋅ 10 − 4 cm ) 2 = 1, 66 ns 2 2 ⋅ 12 cm / s τ T = 21, 43 ⋅ 10 − 6 s 9,3 ⋅ 10 −3 A + 1, 66 ⋅ 10 − 9 s 14, 7 ⋅ 10 − 3 A τ T = 13,5 µs + 0, 61ns (vernachlässigbar) τ T = 13,5 µs Cd = 13,5 ⋅ 10 26 ⋅ 10 −6 −3 s A 14, 7 ⋅ 10 −3 A = 7 , 63 µF 5, 43 ⋅ 10 −3 A 14, 7 ⋅ 10 − 3 A Aufgaben und Lösungen 22 Aufgabe 2.8 Leiten Sie die Beziehung für die Diffusionskapazität bei langen Geometriemaßen, d.h. w'n » Lp und w'p » Ln her. Gehen Sie bei der Herleitung davon aus, dass die Generation und Rekombination in der Raumladungszone vernachlässigbar ist. Hinweis: Zur Lösung der Aufgabe ist das Studium "Vertiefende Betrachtung zum Experiment" (Kap.1.5) erforderlich. Lösung zur Aufgabe 2.8: n p n p n n (x) p p (x) pL n p (x) n n (x) p p (x) n p (x) p n (x) a) x p x n Qp ∆ UPN >0 p n (x) x b) x xn ∆ UPN <0 x Bild L: 2.8 Um die Diffusionskapazität zu berechnen, muss zuerst die gesamte positive Ladung in dem pn-Übergang bestimmt werden. Diese besteht im n-Gebiet aus injizierten Löchern, deren Verteilung durch Beziehung (1.70) − p n′ ( x ) = p ′L e ( x − xn ) Lp U /φ = p no ( e PN t − 1) e − ( x − xn ) Lp beschrieben ist. Durch Integration und Multiplikation mit der Fläche A erhält man die injizierte positive Ladung ∞ Q p = qA ∫ p n′ ( x ) dx = qAL p p no ⎛⎜⎝ e xn U PN / φ t − 1 ⎞⎟ ⎠ im n-Gebiet. Der Löcherstrom Ip(xn) beträgt aus vorhergehender Ladungsbeziehung Aufgaben und Lösungen 23 I p ( x n ) = − qAD p dp n′ ( x n ) = qA dx Dp U /φ ( e PN t − 1) . Lp Durch Einsetzen dieses Löcherstromes, der eine Folge der Ladung ist, resultiert die einfache Form Qp = Lp2 Dp I p ( xn ) = τ p I p ( xn ) , wobei Gleichung (1.69) Lp = D pτ p mit verwendet wurde. Diese Beziehung besagt, dass die injizierte Ladung um so größer ist je größer die Lebensdauer und der Strom sind. Die positive Ladung im p-Gebiet wird durch die Majoritätsträger erzeugt, die aus Neutralitätsgründen innerhalb der dielektrischen Relaxationszeit den Minoritätsträgern in diesem Gebiet folgen. Da die Verteilung der Minoritätsträger bekannt ist und n'p(x) = p'p(x) ist, ergibt sich nach einer ähnlichen Herleitung eine Majoritätsträgerladung von Q p = −Qn = τ n I n ( x p ) im p-Gebiet. Die gesamte positive Ladung im pn-Übergang beträgt damit Q = τ n I n ( x p ) + τ p I p ( xn ) . Diese kann als Funktion des Gesamtstroms I = I n ( x p ) + I p ( xn ) in der Form Q = τT I ausgedrückt werden. τT wird Transitzeit genannt. Sie bestimmt, wie in Abschnitt 2.4.2 gezeigt wurde, maßgeblich das Schaltverhalten des pn-Übergangs. Ihre Abhängigkeit von Strömen und Lebensdauern ergibt sich direkt aus den obigen Beziehungen zu τT = τ n In (x p ) I +τ p I p ( xn ) I Mit Q = τT I U /φ = τ T I S ⎛⎜ e PN t − 1 ⎞⎟ ⎠ ⎝ resultiert eine Diffusionskapazität von . Aufgaben und Lösungen 24 Cd = dQ dU PN τ /φ U = T I S e PN t φ t die mit derjenigen für die kurzen Abmessungen Gl.(2.63) identisch ist. Der physikalische Hintergrund ist jedoch verschieden. Die Transitzeit hängt vielmehr bei langen Abmessungen von den Lebensdauern und somit von den Generations- und Rekombinationsraten der Ladungsträger im Silizium ab. Aufgaben und Lösungen 25 Kapitel 3 Aufgabe 3.1 In Bild 3.4 ist das Dotierungsprofil eines npn-Transistors dargestellt. Bestimmen Sie daraus in etwa den Transportstrom ISS, den Kollektorstrom IC bei UBE = 750mV sowie die Stromverstärkungen im normalen und inversen Betrieb. Daten des Transistors: A = 4µm2; DPE ≈ 12cm2/s; DnB ≈ 25cm2/s; DpC ≈ 14cm2/s. Hinweis: Der vergrabene Kollektoranschluss kann als sehr niederohmig betrachtet werden. Lösung zur Aufgabe 3.1: I SS = AqDnB ni2 N AB x B ≈ 4 ⋅ 10 −8 cm 2 1, 6 ⋅ 10 −19 As 25cm 2 / s (1, 45 ⋅ 1010 cm − 3 ) 2 1017 cm − 3 ⋅ 0, 2 ⋅ 10 − 4 cm I SS = 1, 7 ⋅ 10 −17 A I C = I SS BN = BI = U /φ ( e BE t D nE N DE w E D pE N AB x B D nB N DC w EPI D pC N AB x B − 1) = 1, 7 ⋅ 10 ≈ −17 ⎛ 750 mV ⎞ A⎜⎜ e 26 mV − 1 ⎟⎟ = 57 ,3 µA ⎜ ⎟ ⎝ ⎠ 25cm / s ⋅ 10 2 19 2 17 12 cm / s ⋅ 10 ≈ cm −3 cm 0, 25 µm −3 0, 2 µm = 260 25cm 2 / s ⋅ 1016 cm − 3 0,55 µm 2 14 cm / s ⋅ 10 17 cm −3 0, 2 µm = 0,5 Vergrabener Kollektor wird in erster Näherung als sehr niederohmiger Kontakt betrachtet. Aufgaben und Lösungen 26 Aufgabe 3.2 In einem p-Wannen CMOS-Prozess wird, wie im Bild gezeigt, ein npn-Transistor realisiert. ND B 3,4um E 0,2um NA C ND +5V Bild A: 3.2 Die Daten betragen: ND-Sourcedotierung 5⋅1019 cm-3, NA-Wannendotierung 1017 cm-3, Emitterfläche AE = 10⋅10µm2, DnB = 25 cm2/s; DpE = 8 cm2/s. Gesucht werden bei Raumtemperatur: Der Transportstrom ISS, der Kollektorstrom IC bei UBE = 700 mV und die Stromverstärkung B. Zur Vereinfachung kann angenommen werden, dass die Basisweite der metallurgischen Weite von 3,2 µm entspricht. Lösung zur Aufgabe 3.2: I SS = AqD nB n i2 N AB x B 2 ≈ (10 ⋅ 10 − 4 cm ) 1, 6 ⋅ 10 −19 As ⋅ 25cm 2 / s (1, 45 ⋅ 1010 cm − 3 ) 1017 cm − 3 ⋅ 3, 2 ⋅ 10 − 4 cm I SS = 2, 63 ⋅ 10 −17 A ⎞ ⎛ 700 mV U BE / φ t −17 ⎜ 26 mV I C = I SS ( e A⎜ e − 1) = 2, 63 ⋅ 10 − 1 ⎟⎟ ⎟ ⎜ ⎠ ⎝ I C = 12,95 µA B = D nE N DE w E D pE N AB x B B = 97 ,5 = 2 25cm / s ⋅ 5 ⋅ 10 2 8 cm / s ⋅ 10 17 19 cm cm −3 −3 0, 2 ⋅ 10 3, 2 ⋅ 10 −4 −4 cm cm 2 Aufgaben und Lösungen 27 Aufgabe 3.3 Gegeben ist die gezeigte Schaltung, wobei der Transistor die Daten BN = 200, BI = 2 und ISS = 10-15A besitzt. 5V R=1k Ω C B E Bild A 3.3: a) Bei UBE = 0,7V befindet sich der Transistor in Stromsättigung. Berechnen Sie hierfür IC, IB und UCE. b) Der Transistor soll in Spannungssättigung geschaltet werden, wobei UCE auf 100mV sinken soll. Welcher Basisstrom IB muss dazu eingeprägt werden? Lösung zur Aufgabe 3.3: a) Gesucht IC, IB und UCE ⎛ 700 ⎞ U BE / φ t −15 ⎜ 26 ⎛ ⎞ I C = I SS ⎜ e − 1 ⎟ = 10 A⎜ e − 1 ⎟⎟ = 0,5 mA ⎝ ⎠ ⎜ ⎟ ⎝ ⎠ I B = I C / B N = 0,5 mA / 200 = 2,5 µA U CE = 5V − R ⋅ I C = 5V − 1kΩ ⋅ 0,5 mA = 4,5V b) Gesucht IB wenn UCE = 100mV betragen soll U CEsat = φ t ln B N [ I C + I B (1 + B I )] BI [BN I B − I C ] Aufgaben und Lösungen 28 aufgelöst nach IB IB = IC = IB = IC IB /φ U I C ⎛⎜ B N + e CEsat t ⎞⎟ ⎝ ⎠ U /φ e CEsat t B I B N − B N (1 + B I ) 5V − 0,1V = 4,9 mA 1kΩ ( 4,9 ⋅ 10 − 3 A 200 + e100 / 26 e100 / 26 ⋅ 200 ⋅ 2 − 200 ⋅ 3 = 73, 4 < B N ) = 66.7 µA Aufgaben und Lösungen 29 Aufgabe 3.4 Der Transistor in der gezeigten Schaltung hat eine Stromverstärkung von BN = 100. Wie groß sind die Ströme IB, IC, IE und die Ausgangsspannung Uo? IB 5V IC 3V IE R=1k Ω U0 Bild A: 3.4 Lösung zur Aufgabe 3.4 Überschlägig: UBE ≈ 0,7V (Schleusenspannung) U0 = 3V - 0,7V = 2,3V Emitterstrom: 2,3V = 2,3 mA 1kΩ I E = I B + I C = I B + I B BN IE ≈ Basisstrom: I B = I E / (1 + B N ) I B = 2,3mA / 101 = 22,8 µA Kollektorstrom: I C = B N I B = 22 ,8 µA ⋅ 100 = 2 , 28 mA Aufgaben und Lösungen 30 Genauere Herleitung: U 0 = 3V − U BE U U /φ /φ I C = I SS ⎛⎜ e BE t − 1 ⎞⎟ ≈ I SS e BE t ⎝ ⎠ I U BE = φ t ln C I SS damit ergibt sich eine Ausgangsspannung von I U 0 = 3V − φ t ln C I SS da aber auch U 0 = ( I C + I B ) R = ( I C + I C / B N )R fließt ein Kollektorstrom von IC = U0 (1 + 1 / B N ) R . Die resultierende Ausgangsspannung beträgt damit U0 U 0 = 3V − φ t ln (1 + 1 / B N ) R I SS Diese Gleichung ist nur iterativ lösbar. . Aufgaben und Lösungen 31 Aufgabe 3.5 Gegeben ist ein Transistor mit den zur Vereinfachung als homogen angenommenen 17 −3 ′ = 1016 cm −3 ; xB (bei UBC = 0V) = 1µm; Dotierungen: N ′AB = 10 cm ; N DC DnB = 18 cm2/s; A = 10µm2 Gesucht wird: Die Early-Spannung UAN und die Steigung dI C / dU BC des Kollektorstroms bei UBC = 0V und UBE = 0,7V Aufgaben und Lösungen 32 Lösung zur Aufgabe 3.5 a) Early-Spannung C jco = A qε o ε si ⎛ 1 1 + 2⎜ ⎜ N′ ′ N DC ⎝ AB φ ic = φ t ln ′ N ′AB N DC ≈ A ⎞ ⎟φ ⎟ ic ⎠ = 26 mV ln ni2 φ ic = 0, 76V C jco ≈ 10 ⋅ 10 −8 cm 2 1, 6 ⋅ 10 −19 10 16 qε o ε si ′ 2φ ic / N DC cm −3 (1,45 ⋅ 10 10 10 17 cm cm − 3 As ⋅ 11,9 ⋅ 8,854 ⋅ 10 −3 ) 2 −14 As / cm 2 ⋅ 0, 76V / 1016 cm − 3 C jco ≈ 3,3 fF 2 17 −19 −8 −3 −4 Q Bo = qAN ′AB x Bo = 1, 6 ⋅ 10 As ⋅ 10 ⋅ 10 cm ⋅ 10 cm 10 cm Q Bo = 1, 6 ⋅ 10 −13 As U AN = Q Bo / C jco = 1, 6 ⋅ 10 U AN = 48,5V −13 As / 3,3 ⋅ 10 −15 As / V b) Steigung dIC/dUBC IC = qAD nB n Bo ⎛ U BE / φ t − 1 ⎞⎟ ⎜⎜ e ⎟ xB ⎝ ⎠ ni2 (1, 45 ⋅ 1010 ) 2 cm − 6 n Bo = = = 2,1 ⋅ 10 3 cm − 3 17 −3 N ′AB 10 cm IC = 1, 6 ⋅ 10 −19 As 10 ⋅ 10 −8 cm 2 ⋅ 18cm 2 / s ⋅ 2,1 ⋅ 10 3 cm − 3 I C = 2,98 µA 1 ⋅ 10 −4 cm (e 700 / 26 − 1) dI C / dU BC = − I Co / U AN = −2,98 µA / 48,5V = −6,1 ⋅ 10 −8 A / V entspricht einem Kleinsignal-Ausgangswiderstand von ro = 16 , 2 MΩ Aufgaben und Lösungen 33 Aufgabe 3.6 Das Kriterium für den Beginn der Emitterrandverdrängung ist gegeben, wenn der Spannungsabfall in der Basis größer als φt ist. Bestimmen Sie den Kollektorstrom, bei Raumtemperatur, bei dem die Emitterrandverdrängung bei einem npn-Transistor einsetzt. Die Daten des Transistors sind: N ′AB = 10 17 −3 2 ; µ p = 400 cm / Vs ; x B = 1µm; B N = 50 ; einseitiger Basiskontakt, wie in (Bild 3.2) gezeigt, mit l E = 30 µm und b E = 20 µm . cm Zur Vereinfachung wurden homogene Dotierungen angegeben. Lösung zur Aufgabe 3.6 Kriterium für den Beginn der Emitterrandverdrängung: I B ⋅ RB ≈ φt RB ≈ ρ B bE ; 3x B LE 1 1 1 ρB = ≈ = q( µ p p + µ n n) qµ p p qµ p N ′AB bE 1 RB ≈ qµ p N ′AB ⋅ 3 ⋅ x B L E 1 ≈ 20 ⋅ 10 − 4 cm 30 ⋅ 10 − 4 cm cm 2 ⋅ 1017 cm − 3 ⋅ 3 ⋅ 10 − 4 cm V ⋅s (relativ groß; L E vergrößern ) 1, 6 ⋅ 10 −19 As ⋅ 0, 4 ⋅ 10 3 ≈ 347 Ω 26 mV I B ⋅ R B ≈ φ t = 26 mV ; I B = = 75 µA 347 Ω somit Beginn der Emitterrandverdrängung bei einem Kollektorstrom von I C = B N ⋅ I B = 50 ⋅ 75 µA = 3, 75 mA Aufgaben und Lösungen 34 Aufgabe 3.7 Bei dem als Diode verknüpften Transistor wird bei einem Strom von I = 80mA eine Spannung von UPN = 0,975 V gemessen. Wie groß sind die Widerstände RS (Gl.3.88) und RB? Daten des Transistors: BN = 150; ISS = 10-16A¸ RE ≈ 0Ω IC RB UPN I UBE Bild A: 3.7 Lösung zur Aufgabe 3.7 I ≈ I C ≈ I SS e ′ /φ U BE t 80 ⋅ 10 I −3 A ′ = φ t ln U BE = 26 mV ln = 0,892V − 16 I SS A 10 ′ +I U PN = U BE RB 1 + BN ′ + IR S = U BE ′ = 0 ,975V − 0 ,892V = 0 , 083V IR S = U PN − U BE RS = RS = 0, 083V 80 ⋅ 10 − 3 A RB 1 + BN = 1, 04 Ω d.h . R B = R S (1 + B N ) = 157 Ω Aufgaben und Lösungen 35 Aufgabe 3.8 Bei einem npn-Transistor in Emitterschaltung und wechselspannungsmäßig kurzgeschlossenem Ausgang (Bild 3.42) wurden bei 1GHz die folgenden KleinsignalStromverstärkungen gemessen: ⏐β(jω)⏐ = 40 bei IC = 1mA und ⏐β(jω)⏐ = 48 bei IC = 3mA. Die gemessene Kleinsignal-Kapazität Cjc beträgt 35 fF. Bestimmen Sie aus den Angaben die Sperrschichtkapazität Cje und die Transitzeit τN. Dabei wird vorausgesetzt, dass starke Injektion noch nicht auftritt und Cje und τN konstant bleiben. Bei der Lösung der Aufgabe ist Folgendes zu beachten: Im Frequenzbereich f ω » 1 ergibt sich eine Verstärkung bei der Frequenz fm = ωβ fβ Gl.(3.115) von β ( jf m ) = β N fβ fm . Bei der Transitfrequenz resultiert hieraus β ( jf T ) = 1 = β N fβ . fT Damit ergibt sich aus dem Verhältnis der Verstärkungen bei verschiedenen Frequenzen β ( jf m ) β ( jf T ) = β ( jf m ) = fT fm der Zusammenhang f T = β ( jf m ) ⋅ f m . , Aufgaben und Lösungen 36 Lösung zur Aufgabe 3.8 Gesucht Transitfrequenz fT aus den indirekten Messungen f T = β ( jf m ) f m f T 1 = 10 91 / s ⋅ 40 = 40 ⋅ 10 91 / s bei I C = 1mA f T 2 = 10 91 / s ⋅ 48 = 48 ⋅ 10 91 / s bei I C = 3mA Aus Beziehung (3.118) τ N = 1 / ωT − τN = I.) II.) τN = τN = φt IC (C je + C jc ) φ 1 − t C je + C jc 2πf T IC ( 1 9 2π ⋅ 40 ⋅ 10 1 / s 1 9 2π ⋅ 48 ⋅ 10 1 / s − 26 ⋅ 10 10 − −3 −3 26 ⋅ 10 3 ⋅ 10 ) V [C je + 35 ⋅ 10 −15 As / V ] V [C je + 35 ⋅ 10 −15 As / V ] A −3 −3 A Annahme: Bei Stromänderung von 1mA auf 3mA sollen Cje, Cjc und τN unverändert bleiben. damit gilt: I.-II.) 0 = 3,98 ⋅ 10 −12 s − 26V / A ( C je + 35 ⋅ 10 −15 As / V ) − 3, 32 ⋅ 10 −12 s + 8, 66V / A ( C je + 35 ⋅ 10 −15 As / V ) nach Cje aufgelöst ergibt: C je = 2 ,88 fF Überprüfung der Annahme Cje = konst. U /φ I C ≈ I SS e BE t IC2 I C1 ≈ U /φ e BE , 2 t U /φ e BE ,1 t I ∆U BE 1 U BE , 2 − U BE ,1 = ln C 2 = I C1 φt φt ( ) Aufgaben und Lösungen 37 Änderung der Basisspannung die auftritt: ∆U BE = 26 mV ln 3mA = 28, 6 mV 1mA Diese Spannungsänderung kann als geringer Einfluss auf die Sperrschichtkapazität Cje betrachtet werden. Aufgaben und Lösungen 38 Aufgabe 3.9 Bestimmen Sie die Ausgangsspannung uo des gezeigten Verstärkers bei niedrigen Frequenzen, wenn die Eingangsspannung ui = 50µV beträgt. Daten des Transistors: RB ~ 0Ω; UAN = 25V. Wovon würde die Verstärkung abhängen, wenn R einen Wert von unendlich hätte? UDD IC=20uA RL =10 6 Ω uo = ? ui ~ ri = 0 Ω Bild A: 3.9 Lösung zur Aufgabe 3.9: Bei niedrigen Frequenzen können Kapazitäten vernachlässigt werden. C B ui ~ ~ gπ gm ui go gL uo E Bild L 3.9: 1 uo = − g m ui go + g L I 20 ⋅ 10 − 6 A = 0,8 ⋅ 10 − 61 / Ω go = C = U AN 25V g L = 1 / R L = 10 − 61 / Ω Aufgaben und Lösungen uo ui =− 39 gm go + g L = I C / φt go + g L 20 ⋅ 10 − 6 A = −3 −6 26 ⋅ 10 V ( 0,8 + 1, 0 ) 10 A / V u o = u i ⋅ 427 = 50 µV ⋅ 427 = 21,3mV mit: = 427 u R L = ∞ d.h . g L = 0 ist o unabhängig von I C ui uo ui uo ui = = gm go = I C / φt U = AN I C / U AN φt ! 25V = 961 26 mV Diese Verstärkung wird intrinsische Transistorverstärkung genannt. Aufgaben und Lösungen 40 Aufgabe 3.10 Leiten Sie aus dem Kleinsignal-Ersatzschaltbild (Bild 3.42b) das Verhältnis der Kleinsignalströme io / ib, wie es durch Beziehung (3.110) beschrieben ist, ab. Lösung zur Aufgabe 3.10: io C jc rb UCE + ube ib ib a) i1 i2 gπ Cbe Bild L 3.10: am Knoten a) ib = i1 + i2 + i3 I) ′ ( g π + jωC be + jωC je ) i b = u be am Knoten b) i3 + io - i C = 0 II) ′ jωC jC + i o − u be ′ gm = 0 u be hieraus: ′ =− u be io jω C jC − g m dies in I) eingesetzt ergibt: gm io ib = gπ 1+ (1 − jωC jc gm ) jω ( C be + C je ) gπ i3 b) io ic = gmube Aufgaben und Lösungen mit gπ = io ib io ib 41 gm βN β N (1 − = 1+ jωC jc gm ) jω β ( C + C jc ) g m N be ω ) ωz ω (1 + j ) ωβ (1 − j = βN mit Nullstellenkreisfrequenz ωz = gm C jc und Polstellenkreisfrequenz ωβ = gm β N ( C be + C jc ) . Aufgaben und Lösungen 42 Kapitel 4 Aufgabe 4.1 Bei der MOS-Struktur setzt starke Inversion ein, wenn die Elektronenkonzentration an der Halbleiteroberfläche ns gleich der der Substratdotierung NA ist. Die Oberflächenspannung φS hat dabei den Wert φS (SI) und bleibt auch bei größerer Gatespannung und Inversionsschichtladung näherungsweise konstant. Skizzieren Sie für diesen Fall das Bänderdiagramm und weisen Sie nach, dass sich der Wert der Oberflächenspannung nur noch um ca. 60mV ändert, wenn ns um den Faktor 10 zunimmt. Lösung zur Aufgabe 4.1 W WC Wi WF WV ∆φS Wi1 Wi2 φS Bild L 4.1: W F −Wi1 n S ,1 =ˆ N A = ni e kT W F −Wi 2 n S , 2 =ˆ 10 N A = n i e kT W F −Wi 2 nS ,2 n S ,1 = 10 = ln 10 = ∆φ S = ni e kT W F −Wi1 kT ni e − W i 2 + W i1 kT W i 2 − W i1 −q = kT ln 10 = 26 mV ⋅ ln 10 = 59,8 mV q Aufgaben und Lösungen 43 Aufgabe 4.2 Nachfolgend ist die Kleinsignalkapazität einer n-Kanal MOS-Struktur in Abhängigkeit von der Gatespannung für mittlere Frequenzen dargestellt. Das Si-Substrat sei mit NA = 1016 cm-3 dotiert. C 80 nF cm 2 24,3 UFB [V] UGB Bild A: 4.2 a) Wie groß ist die Weite der Verarmungszone bei Inversion? b) Berechnen Sie die Oberflächenspannung bei Beginn von starker Inversion. c) Wie groß ist die Einsatzspannung des Transistors, wenn die Flachbandspannung UFB = - 0,1 V beträgt und USB = 0 V ist? d) Wie groß ist die Einsatzspannung bei USB = 5 V? Lösung zur Aufgabe 4.2: a) Weite der Raumladungszone bei Inversion ⎛ 1 1 C 'i = ⎜ + ⎜ C' C ' ox j ⎝ Cj = xd = ⎞ ⎟ ⎟ ⎠ −1 = 24 , 3nf / cm 2 1 1 2 = = 34 , 9 nf / cm 1 / C ' i −1 / C ' ox 1 / 24 ,3 − 1 / 80 ε o ε Si C' j = As ⋅ 11,9 V ⋅ cm = 0,3 µm As −9 34 ⋅ 10 V ⋅ cm 2 8,86 ⋅ 10 −14 Aufgaben und Lösungen b) 44 Oberflächenspannung bei starker Inversion Ladung in der Raumladungszone σ d = − qN A x d = − qN A 2ε o ε Si φ S ( SI ) φ S ( SI ) = φ S ( SI ) = qN A x d2 2ε o ε Si 1, 6 ⋅ 10 −19 As ⋅ 10 16 −3 −4 ( 0,3 ⋅ 10 cm ) As −14 2 ⋅ 11,9 ⋅ 8,86 ⋅ 10 V ⋅ cm cm φ S ( SI ) = 0, 7V alternativer Rechengang φ F = φ t ln NA ni = 26 mV ln 1016 cm −3 1, 45 ⋅ 1010 = 0,35V φ S ( SI ) = 2φ F = 0, 7V c) Einsatzspannung des Transistors 1 U Ton = U FB + 2φ F + C ' ox qN A 2ε Si ε o 2φ F U Ton = 1, 21V U Tn = U Ton + γ ( 2φ F + U SB − γ = 1 C ' ox 2φ F ) qN A 2ε o ε Si = 0, 73 V U Tn = 1, 21V + 0 , 73 V U Tn = 2,34V [ 0 , 7V + 5V − 0 , 7V ] 2 Aufgaben und Lösungen 45 Aufgabe 4.3 Dargestellt ist eine Ein-Transistor Zelle. Die n+-Polyseite der Kapazität kann auf 1,8 V bzw. 0 V aufgeladen werden. Dadurch ist es möglich, dass ein unerlaubt großer Leckstrom durch den gezeigten parasitären n-Kanal Transistor fließt. Bestimmen Sie: a) Die "worst case" Spannungskonstellation, b) die Einsatzspannung des parasitären Transistors bei dox = 7 nm (oxid collar) sowie wenn c) dox auf 30 nm vergrößert wird und d) eine Spannung von – 1 V an die p-Wanne (p-Well) gelegt wird. Al-1 Bit Line (W) Bit Line Contact STI n+ P-Well 0V / -1V Word Line (WSI / n+ poly) Oxide Collar WL Capacitor Insulator n 17 -3 NA =2x10 cm p-Well n+ poly Buried N-Well n +0.9V 1.8V/0V BL CS UFB= 0.8V +0.9V Buried Plate p-Si Bild A: 4.3 Lösung zur Aufgabe 4.3 a) dox = 7nm; 0V am p-well N 2 ⋅ 1017 cm −3 2φ F = 2φ t ln A = 2 ⋅ 26 mV ln = 885 mV ni 1, 45 ⋅ 10 −10 cm − 3 C 'ox = ε oε ox d ox = As ⋅ 3,9 F V ⋅ cm = 493 ⋅ 10 − 9 2 −7 7 ⋅ 10 cm cm 8,85 ⋅ 10 −14 Aufgaben und Lösungen γ = = 1 C ' ox 46 qN A 2ε o ε Si 1 493 ⋅ 10 −9 F / cm 2 1, 6 ⋅ 10 −19 As ⋅ 2 ⋅ 10 17 cm −3 ⋅ 2 ⋅ 11,9 ⋅ 8,85 ⋅ 10 γ = 0,526 V worst case: 1,8V 0V USB D S UGS CS +0,9V Bild L 4.3 U Tn = U FB + 2φ F + γ 2φ F + U SB = −0,8V + 0,855V + 0,526 V 0,885V + 0,9V = U Tn = 0, 758V b) d ox = 30 nm U Tn = −0,8V + 0,855V + U Tn = 3, 07V c) zusätzlich USB = 1,9V U Tn = 3,82V 30 0,526 V 7 0,885V + 0, 9V = −14 As cm Aufgaben und Lösungen 47 Aufgabe 4.4 Gesucht wird die Einsatzspannung des gezeigten Feldoxidtransistors, der in Kapitel 4.3.3 näher beschrieben wurde. Bestimmen Sie die Einsatzspannung UFT des Transistors wenn die BPSG-Schicht und das Feldoxid (FOX) zusammen 100 nm bzw. 200 nm betragen. Welchen Wert nimmt die Einsatzspannung für die genannten beiden Fälle an, wenn eine Source-Bulkspannung von USB = 1,0 V verwendet wird? Metallbahn BPSG FOX n+ FOX n+ Diffusionsbahn p Bild A: 4.4 Die wirksame Dielektrizitätskonstante der Doppelschicht beträgt ε r ≈ 4,1 . Die Substratdotierung hat einen Wert von N A = 10 U FB = −0, 4V . 17 cm −3 . Die Flachbandspannung liegt bei Aufgaben und Lösungen 48 Lösung zur Aufgabe 4.4 1 U FT = U FB + 2φ F + γ 2φ F ; γ = C ' ox C ' ox = ε o ε ox d ox = As ⋅ 4,1 nF V ⋅ cm = 36 ,3 −7 2 cm 100 ⋅ 10 cm 8,85 ⋅ 10 NA 2φ F = 2φ t ln ni 36,3 ⋅ 10 −9 −14 = 2 ⋅ 26 mV ln 1 γ = qN A 2ε o ε Si As 1, 6 ⋅ 10 −19 1017 cm −3 1, 45 ⋅ 1010 cm − 3 As ⋅ 10 17 cm −3 = 0,88V ⋅ 2 ⋅ 11,9 ⋅ 8,85 ⋅ 10 V ⋅ cm 2 γ = 5, 05 V Fall 1) U FT (U SB = 0V ) = −0, 4V + 0,88V + 5, 05 V 0 ,88V U FT (U SB = 0V ) = 5, 22V Fall 2) d ox = 200 nm γ = 5, 05 V 200 nm = 10,1 V 100 nm U FT (U SB = 0V ) = −0 , 4V + 0 ,88V + 10 ,1 V 0 ,88V 1 U FT (U SB = 0V ) = 9 ,95V mit Fall 1) U SB = 1V U FT = U FTo + γ 2φ F + U SB − = 5, 22V + 5, 05 V U FT = 7 , 41V Fall 2) [ U FT = 14,32V [ 2φ F ] 0,88V + 1, 0V − 0,88V ] −14 As V ⋅ cm Aufgaben und Lösungen 49 Aufgabe 4.5 a) Bestimmen Sie bei Raumtemperatur die Einsatzspannung des dargestellten MOSTransistors mit dox = 9,5 nm. b) b) Bestimmen Sie die Einsatzspannungsschwankung ebenfalls bei Raumtemperatur, wenn die Oxiddicke in der Fertigung zwischen 9,5 nm und 10,5 nm schwankt. c) c) Erwarten Sie eine Einsatzspannungsreduzierung infolge der kurzen Kanallänge (Bestimmen Sie die Weite der Raumladungszone)? G d ox SiO2 n+ n+ 0,35um UFB = 0,8V NA = 2 10 17cm-3 10 20 cm -3 Bild A: 4.5 Lösung zur Aufgabe 4.5 U Ton = U FB + 2φ F + γ 2φ F ; C ' ox = ε o ε ox = d ox 363 ⋅ 10 −9 1 C ' ox qN A 2ε o ε Si As ⋅ 3,9 −9 F V ⋅ cm = 363 ⋅ 10 3 −7 cm 9,5 ⋅ 10 cm 8,85 ⋅ 10 1 γ = γ = As −14 1, 6 ⋅ 10 −19 As ⋅ 2 ⋅ 10 17 cm −3 ⋅ 2 ⋅ 11,9 ⋅ 8,85 ⋅ 10 V ⋅ cm 2 γ = 0 , 715V N 2 ⋅ 1017 cm −3 2φ F = 2φ t ln A = 2 ⋅ 26 mV ln = 0,854V 10 −3 ni 1, 45 ⋅ 10 cm a) U Ton = −0 ,8V + 0 ,854V + 0 , 715 V 0 ,854V −14 As V ⋅ cm Aufgaben und Lösungen 50 U Ton = 0, 714V b) ∆U Ton = 2φ F (γ 1 − γ 2 ) = = 2φ F = 0,854V qN A 2ε Si 2 ε o ε ox 2φ F qN A 2ε o ε Si 1 ε o ε ox (d ox1 − d ox 2 ) (d ox1 − d ox 2 ) 1, 6 ⋅ 10 −19 As ⋅ 2 ⋅ 1017 cm − 3 ⋅ 2 ⋅ 11,9 (10,5 − 9,5 ) ⋅ 10 − 7 cm As ( 3,9 ) 2 ⋅ 8,85 ⋅ 10 −14 V ⋅ cm ∆U Ton = 69 ,5 mV c) Roll-down? w= w= 2ε o ε Si q N N 1 φ i ; φ i = φ t ln A D = 1, 08V 2 NA ni As ⋅ 11,9 V ⋅ cm ⋅ 1, 03V ≈ 0,1µm 1, 6 ⋅ 10 −19 As ⋅ 2 ⋅ 1017 cm − 3 2 ⋅ 8,85 ⋅ 10 −14 Die metallurgische Kanallänge hat einen Wert von 0,35µm, wodurch die effektive Kanallänge nur noch 0,15µm beträgt. D.h. roll-down ist gerade noch vernachlässigbar. Aufgaben und Lösungen 51 Aufgabe 4.6 Ein n-Kanal-Transistor mit w/l = 1,5; dox = 5 nm; εox = 3,9; µn = 600 cm2/Vs und USB = 0 V wird als steuerbarer Widerstand eingesetzt. a) Um wieviel muss die Gatespannung größer als die Einsatzspannung sein, damit für sehr kleine Drain-Sourcespannungen (UDS → 0) ein Widerstand von 2,5 kΩ zwischen den Drain-Sourceklemmen des Transistors messbar wird? b) Wie groß ist für diesen Widerstand die Elektronendichte σn der Inversionsschicht? Aufgaben und Lösungen 52 Lösung zur Aufgabe 4.6: 2 ⎤ ⎡ U DS w ⎥; β = µ C ′ I DS = β n ⎢ (U GS − U Tn )U DS − n n ox 2 ⎥ l ⎢ ⎦ ⎣ R = R U DS I DS U DS → 0V 1 = β n (U GS − U Tn − = U DS 2 ) 1 β n (U GS − U Tn ) overdrive U GS − U Tn = 1 βnR 1 = µn ε o ε ox w d ox l R 1 = 2 600 −14 cm 3,9 ⋅ 8,854 ⋅ 10 V ⋅s 5 ⋅ 10 − 7 cm As V ⋅cm 1,5 ⋅ 2,5 ⋅ 10 3 V / A U GS − U Tn = 0 , 64V σ n = − C ' ox (U GS − U Tn − φ K ( x ) ) bei UDS ~ 0 ist auch φK ~ 0 ′ (U GS − U Tn ) = − σ n = − C ox σ n = 4, 42 ⋅ 10 − 7 3,9 ⋅ 8,854 ⋅ 10 −14 5 ⋅ 10 −7 cm As V ⋅ cm = 0, 64V As cm 2 zum Vergleich Grenzflächenzustände: σ SS = 10 −10 As cm 2 Aufgaben und Lösungen 53 Aufgabe 4.7 Durch einen n-Kanal-Transistor mit kn = 120 µA/V2, w/l = 5 und UTon = 0,5 V fließt ein Strom von 300 µA. Die Gate-Sourcespannung beträgt 3 V. Wie groß ist die DrainSourcespannung? Lösung zur Aufgabe 4.7: Annahme: I DS = Sättigung I DS = 120 ⋅ 10 A −6 V 2 βn 2 (U GS ⋅ 5 ⋅ ( 2 ,5V ) 2 − U Tn ) 2 = 3, 75 mA d.h. Transistor muss im Widerstandsbereich sein. Dies muß so sein, denn in Sättigung ist der Strom unabhängig von der UDS-Spannung (Effekte zweiter Ordnung vernachlässigt) 2 ⎡ U DS ⎤ ⎥ I DS = β n ⎢ (U GS − U Tn )U DS − 2 ⎥ ⎢ ⎦ ⎣ U DS = 2 2 (U GS − U Tn ) ± 4 (U GS − U Tn ) − 8 I DS βn 2 2 ⋅ 2,5V ± 4 ⋅ 6 , 25V U DS = U DS = 4 , 79V 2 − 8 ⋅ 300 µA µA 120 ⋅5 2 V 2 bzw. 0, 21V Mit U DS > U GS − U Tn würde 4,79V Sättigung bedeuten. Somit beträgt U DS = 0, 21V . Aufgaben und Lösungen 54 Aufgabe 4.8 In dem gezeigten Bild ist ein MOS-Transistor als sog. MOS-Diode verschaltet. Wie groß ist die Spannung zwischen Drain und Source bei Raumtemperatur (300 K), wenn a) w/l = 5; b) w/l = 500 und c) w/l » 500 ist? Transistordaten: kn = 120 µA/V2; UTon = 0,8 V; n = 2 Bild A: 4.8 Lösung zur Aufgabe 4.8: −U ) / nφ t w 2 (U I DS = k n ( n − 1)(φ t ) e GS Tn l für U GS ≤ U Tn d.h. Übergang von Sättigung in den Unterschwellstrom-Bereich ist gegeben, wenn U GS = U Tn ist. w ( n − 1)(φ t ) 2 I DS = k n l Dies gilt somit ab einer Geometrie von: (w / l) ≥ ≥ 246 ,5 I DS k n ( n − 1)(φ t ) 2 20 ⋅ 10 = 120 ⋅ 10 −6 A V 2 −6 A ⋅ 1 ⋅ ( 26 ⋅ 10 −3 V) 2 Aufgaben und Lösungen a) 55 2 k w Transistor in Sättigung I DS = n (U DS − U Tn ) 2 l w =5 l U DS = 2 I DS w kn l + U Ton = 2 ⋅ 20 ⋅ 10 120 ⋅ 10 −6 A −6 V2 A + 0,8V ⋅5 U DS = 1, 06V b) w = 500 l U DS = U GS = nφ t ln Transistor im Unterschwellstrombereich I DS w kn ( n − 1)φ t2 l = 2 ⋅ 26 ⋅ 10 − 3 V ln + U Tn 20 ⋅ 10 − 6 A + 0,8V 2 −6 A −3 120 ⋅ 10 ⋅ 500 ( 26 ⋅ 10 V ) V2 U DS = 0, 763V c) w >> 500 l U DS = φ t ln d.h. I DS w k n ( ) → ∞ ( n − 1)φ t2 l U DS = 0V nach Theorie 1. Ordnung: + U Tn UTn hat Schaltfunktion U DS = 2 I DS w kn ( ) l + U Ton mit w/l >> 500 U DS = U Ton falsch Nur gut für Betrachtung kurzer Auf- bzw. Entladevorgänge Aufgaben und Lösungen 56 Aufgabe 4.9 Bestimmen Sie den IDS-Strom bei Raumtemperatur (300 K) ab dem der gezeigte Transistor in den Unterschwellstrombereich gelangt. kn = 120 µA/V2; w/l = 15; n = 2; UTon = 0,6 V Bild A: 4.9 Lösung zur Aufgabe 4.9: (U −U ) / φ t n w I DS = k n ( n − 1)φ t2 e GS Tn l mit U GS = U Tn Beginn Übergang zum Unterschwellstrombereich. Damit ergibt sich: w 2 I DS = k n ( n − 1)φ t l I DS = 120 ⋅ 10 I DS = 1, 22 µA −6 A/V 2 ⋅ 15( 2 − 1)( 26 ⋅ 10 −3 V) 2 Aufgaben und Lösungen 57 Aufgabe 4.10 Die Ein-Transistor-Zelle eines DRAMs kann durch folgendes vereinfachtes Ersatzschaltbild dargestellt werden Al-1 BL Bit Line (W) Bit Line Contact n+ P-Well 0V STI WL Word Line (WSI / n+ poly) Oxide Collar n Tr. 0V/1,8V n+ poly Buried N-Well n +0,9V p-Well 0V CS = 45fF +0,9V Capacitor Insulator n 1,8V " H" 0V " L" Buried Plate p-Si Bild A: 4.10 a) Bestimmen Sie den Unterschwellstrom des mit 0 V am Gate abgeschalteten nTransistors unter "worst case" Bedingungen. b) Verwenden Sie den "worst case" Fall, um die Refreshzeit zu bestimmen. Hierbei ist davon auszugehen, dass ein reduzierter HPegel von 1,5 V und ein erhöhter L-Pegel von 0,3 V noch akzeptabel ist. c) Wie verbessern sich die Werte, wenn eine Source-Bulkspannung, d.h. zusätzlich eine Spannung an "p-Well" von – 1 V verwendet wird? Daten des n-Transistors 27o C 90o C IDS (gemessen bei UGS = 0,6 V) 250 pA 4,8 nA UTon (p-Well an 0 V) 1,0 V 0,87 V γ 0,3 V 0,3 V S 120 mV/Dek 145 mV/Dek 2 φF 0,82 V 0,76 V 2 2 n = 1+ C ′j ′ C ox Aufgaben und Lösungen 58 Lösung zur Aufgabe 4.10: a) worst case Unterschwellstrom? BL WL = 0V D I S BL WL = 0V I UGS =-0,3V 0,3V S 0V 0V +0,9V selbstbegrenzend +0,9V worst case UGS = 0V Bild L: 4.10.1 U GS = 0V ; Refresh worst case: T = 90°C 600 mV ( Meßwert ) ≈ 4 Dekaden Stromreduzierung 145 mV / Dekade I DS = 4 ,8 nA/ 10 4 = 480 ⋅ 10 −15 A; ∆t ≈ 45 ⋅ 10 −15 As / V ∆t ≈ C ∆U I DS 0, 3V 480 ⋅ 10 −15 A ∆t = 28,1ms Genauere Betrachtung I DS = β n ( n − 1)φ t2 e (U GS −U Tn ) / φ t n I DS (U GS = 0, 6V ) I DS (U GS = 0V ) =e ; UDS >100 mV 600 mV 31, 4 mV ⋅ 2 = 14,1 ⋅ 10 3 U SB = 0V o 3 I DS ( 90 , U GS = 0V ) = 4,8 nA / 14,1 ⋅ 10 = 340 ⋅ 10 ∆t = 45 ⋅ 10 −15 As V c) D 1,5V 1,8V b) 1,8V 0 , 3V −15 340⋅10 A mit -1V an p-Well d.h. USB = 1V = 39, 7 ms −15 A Aufgaben und Lösungen 59 U Tn = U Ton + γ ( 2φ F + U SB − 2φ F ) = 0,874V + 0,3 V ( 0 , 76V + 1V − 0, 76V ) = 0,874V + 0,136V Verbesserung ca. 1 Dekade d.h. ∆t ≈ 300 ms genauere Betrachtung: log USB =0V IDS [A] USB =+1V 340 10 90°C -15 136mV -15 39 10 145mV/Dek 0V UGS UTn =0,87V Bild L: 4.10.2 I DS (U SB = 0 ) I DS (U SB = 1V ) =e 136 mV 31, 4 mV ⋅ 2 = 8, 72 U GS = 0V −15 A = 39 , 0 ⋅ 10 −15 A I DS (U SB = +1V ) = 340⋅10 8 , 72 ∆t = 45 ⋅ 10 −15 As V 0 , 3V = 346 ms −15 A 39 , 0⋅10 Aufgabe 4.11 Überprüfen Sie Beziehung 4.5 bei der die Diffusionsspannung φi entweder über die verschiedenen Austrittsarbeiten oder Dotierungen bestimmt werden kann. Aufgaben und Lösungen 60 Lösung zur Aufgabe 4.11: Mit W HA 2 > W HA1 wandern mehr Elektronen von NA1 nach NA2 als umgekehrt; demnach wird A1 positiv gegenüber A2 φi = W HA 2 − W HA1 q W − W FA 2 = FA1 q = W0 − W FA 2 − (W0 − W FA1 ) q Wi −W FA1 kT Mit N A1 = p = n i e Wi − W FA1 = kT ln φi = W FA1 − W FA 2 φ i = φ t ln q N A1 ni Wi − W FA 2 = kT ln (Wi − kT ln = N A1 ni N A2 ni ) − (Wi − kT ln N A2 ni ) q N A2 N A1 Aufgabe 4.12 Bestimmen Sie in etwa die Refresh-Zeit der dargestellten Ein-Transistor-Zelle. U(WL)= -0,5V 1,8V -150mV U(BL)= 0V IDS CS =30fF Aufgaben und Lösungen 61 Der zulässige Spannungsabfall an der Kapazität darf nicht mehr als 0,3V innerhalb der Refresh-Zeit betragen, wobei der Unterschwellstrom als dominierende Stromkomponente betrachtet werden kann. Die Daten bei 900C sind: UTon=0,1V, S =105 mV/Dekade; γ = 0,44V1/2; 2φF = 0,85V; IDS(UGS=UTn) = 25nA. Lösung zur Aufgabe 4.12 U Tn = U Ton + γ ( 2φ F + U SB − 2φ F ) = 0,134V d.h. mit einer Wortleitungsspannung von U(WL) = -0,5V wird eine Stromreduzierung 0, 634V von ≈ 6 Dekaden, und zwar von 25nA auf 25 10-15A erreicht. 0 ,105V / Dekade Daraus ergibt sich eine Refreh-Zeit von ∆t = C∆U/IDS = 360ms. Kapitel 5 Aufgabe 5.1 Die mittlere Lebensdauer einer Metallbahn, die durch eine Stromdichte von 1mA/µm2 belastet wird, beträgt bei einer durchschnittlichen Chiptemperatur von 80°C 75 Jahre. Wie verkürzt sich die Lebensdauer, wenn die mittlere Chiptemperatur 160°C betragen würde? Die gemessene Aktivierungsenergie beträgt WA = 0,65eV. Lösung zur Aufgabe 5.1: MTBF (T1 ) MTBF (T2 ) = W / kT e A 1 W / kT e A 2 WA ⎛ 1 1 ⎞ ⎟ ⎜ − k ⎜⎝ T1 T2 ⎟⎠ =e k =1,38⋅10-23 WS/K WA = 0,65⋅1,6⋅10-19 AsV = 1,04⋅10-19AsV T1 = 353 K; T2 = 433 K Aufgaben und Lösungen 62 − MTBF (T2 ) = MTBF (T1 ) e −19 AsV ⎛ 1 1 ⎞ 1, 04⋅10 − ⎜ ⎟ − 23 353 K 433 K ⎠ ⎝ 1, 38⋅10 AsV / K MTBF (160°C ) = 75 Jahre ⋅ 0, 0193 = Hinweis: FIT ~ 1 MTBF 1,45 Jahre Aufgaben und Lösungen 63 Aufgabe 5.2 Ein IC wird im Automobilbau eingesetzt. Im Betrieb beträgt die Stromdichte in der Versorgungsleitung I = 2,0mA/µm2. Die Lebensdauer (MTBF) der Leiterbahn wurde bei 70°C auf 60 Jahre ermittelt. Überprüfen Sie, ob die Lebensdauer ausreicht einen sicheren Betrieb des ICs für 10.000 Autostunden bei einer IC-Temperatur (Selbsterwärmung + erhöhte Außentemperatur) von 150°C zu garantieren. Die Aktivierungsenergie beträgt WA = 0,65 eV. Lösung zur Aufgabe 5.2: MTBF (T2 ) MTBF (T1 ) = e W A / kT2 W / kT e A 1 WA ⎛ 1 1 ⎞ ⎜⎜ − ⎟⎟ k ⎝ T2 T1 ⎠ =e MTBF (150°C ) = 60 Jahre e 1, 04⋅10 −19 AsV ⎛ 1 1 ⎞1 − ⎟ ⎜ 1, 38⋅10 − 23 Ws / K ⎝ 423 343 ⎠ K MTBF (150°C ) = 0,940 Jahre Im Vergleich 10000h = 1,15 Jahre D.h. Betrieb kann nicht für 10000h garantiert werden. Somit muss Stromdichte durch Vergrößerung der Leiterbahnweite reduziert werden. Hinweis: 10000h mit 50km/h entspricht einem Kilometerstand von 500000 km. Aufgaben und Lösungen 64 Aufgabe 5.3 Gegeben ist folgende Inverterschaltung 3V U Ton = 0, 6V RL k n = 120 µA / V 2 I CL UI C L = 0,1 pF UQ Bild A: 5.3 a) Wie groß muss der Lastwiderstand RL sein, damit die Lastkapazität CL bei gesperrtem Transistor in 3 ns auf ca. 86% (zwei Zeitkonstanten) aufgeladen wird? b) Wie groß muss das Geometrieverhältnis w/l des Schalttransistors gewählt werden, damit die Ausgangsspannung UQ auf 0,3 V absinkt, wenn man an den Eingang eine Spannung von UI = 3 V gibt? c) Wie muss die w/l-Dimensionierung geändert werden, wenn die Eingangspannung nur UI = 2 V beträgt? Lösung zur Aufgabe 5.3: 3 ⋅ 10 −9 s a) τ = 2 R ⋅ C ; R = τ / 2 C = b) I L = I DS ; I L = 2 ⋅ 0,1 ⋅ 10 −12 As / V = 15 kΩ 3V − 0 ,3V = 180 µA 15 kΩ mit UGS -UTn > UDS UGS = 3V; UDS = 0,3V [ w 2 ( I L = I DS = k n U GS − U Tn )U DS − U DS / 2 l IL w/l = 2 k n [(U GS − U Tn )U DS − U DS / 2 ] 180 ⋅ 10 w/l = 120 ⋅ 10 −6 −6 ] A 2 A / V [ 3V − 0, 6V ][ 0,3V − 2 ( 0,3V ) ] 2 w / l = 2, 2 c) mit UGS = 2V w/l = 4 Man sieht an diesem Fall, wie wichtig es ist den H-Pegel genau zu kennen. Aufgaben und Lösungen 65 Aufgabe 5.4 Gegeben ist ein Inverter aus der Leistungselektronik mit einem Verarmungstransistor als Lastelement. Die Eingangsspannung UI beträgt 0V. Wie groß ist die maximale Ausgangsspannung UQ, wenn UCC = 50 V ist? UCC U Ton , 2 = −3,5V T2 φ F = 0,3V Q I UI T1 γ = 0, 7 V UQ Bild A: 5.4 Lösung zur Aufgabe 5.4: 50V UTn,2 D S 32,7V 0 USB UQH -3,5V Bild L: 5.4 U Tn = U Ton + γ 2φ F + U SB − 2φ F 0 = −3,5V + 0, 7 V ( 0, 64V + U SB − ergibt U SB = U QH = 32 , 7V 0, 6V ) USB Aufgaben und Lösungen 66 Aufgaben und Lösungen 67 Aufgabe 5.5 Als Last wird bei einem Inverter ein Anreicherungstransistor verwendet. Die Eingangsspannung UI beträgt 0V. 3,3V +10% U Ton , 2 = 0, 6V T2 γ 2 = 0, 6 V Q I UI T1 φ F = 0,35V UQ Bild A: 5.5 a) Arbeitet der Lasttransistor T2 im linearen oder im Stromsättigungsbereich? b) Wie groß ist die im schlechtesten Fall erreichbare Ausgangsspannung? Lösung zur Aufgabe 5.5: ( ) T2 ist immer in Stromsättigung, da U GS , 2 − U Tn 2 < U DS , 2 ist. γ2 − γ U N + 2φ F + γ 2 U N = U CC − U Ton , 2 + γ 2φ F UQ = U N + = 3,3V ⋅ 0,9 − 0, 6V + 0 , 6 V 2 /4 0, 7V = 2,87V 2 U Q = 2,87V + ( 0, 6 V ) / 2 − 0, 6 V 2 2,87V + 0, 7V + ( 0, 6 V ) / 4 UQ (worst case) = 1,90 V Ohne Berücksichtigung des Substratsteuereffekts würde eine zu hohe Ausgangsspannung von U Q = 3,3V ⋅ 0 ,9 − 0 , 6V = 2 ,37V berechnet. Aufgaben und Lösungen 68 Aufgabe 5.6 Gegeben ist ein Komplementärinverter, der mit einem periodischen Signal getaktet wird. Das Signal ist spezifiziert mit : Tp = 10 ns und τ r = τ f = 1ns . 3V β n = β p = 120 µA / V 2 T2 I U Ton = −U Top = 0, 45V C L = 0,1 pF Q UI T1 CL UQ Bild A: 5.6 Berechnen Sie den transienten Leistungsverbrauch Ptr und vergleichen Sie diesen mit dem dynamischen Leistungsverbrauch Pdyn. Lösung zur Aufgabe 5.6: Ptr = β (U 12 CC − 2U Tn )3 Tp Ptr = 120 µA / V 12 2 τ ( 3V − 0,9V )3 1ns = 9, 26 µW 10 ns Dies ist das Resultat für den Fall, dass CL nicht vorhanden ist. 2 Pdyn = C L fU CC = 0,1 ⋅ 10 −12 As / V 1 10 ⋅ 10 −9 s ( 3V ) 2 Pdyn = 90 µW In den meisten praktischen Fällen ist Pdyn » Ptr , es sei denn, dass die Anstiegs- und Abfallflanken am Eingang und Ausgang eines Gatters sehr unterschiedlich sind. Aufgaben und Lösungen 69 Aufgabe 5.7 Gezeigt ist der Ausschnitt aus einer Schieberegisterschaltung. Hat der Takt φ den Wert von UCC UCC UCC φ D Q1 TT I CL Q0 UQ Bild A: 5.7 wird die parasitäre Kapazität CL auf den logischen Zustand des vorhergehenden Inverters gebracht. Mit φ = 0V ist Transistor TT ausgeschaltet, und die logische Funktion als unterschiedliche Ladung an CL gespeichert. Wie groß ist die Spannung im L- bzw. HZustand an CL? Kann ein Gleichstrom I entstehen und wenn wie groß ist dieser? Daten: UCC = 3V; alle n-Kanal-Transistoren haben die Werte 2 U Ton = 0,5V ; γ = 0, 4 V ; β n = 300 µA / V ; 2φ F = 0, 65V und alle p-Kanal-Transistoren die Werte 2 U Top = −0,5V ; γ = 0, 4 V ; β p = 300 µA / V ; und 2φ F = 0, 65V . Aufgaben und Lösungen 70 Lösung zur Aufgabe 5.7: Spannung an CL = ? UCC =3V UCC φ =UCC aus S D=H 0V ein UI =UCC CL U C a) UCC =3V ein S UCC aus UI =0V aus 2,15V I=? Q0 UQH =UCC UQL CL U C B b) ein I=0 UCC φ =UCC D D=L 0V D USB Bild L: 5.7.1 Situation in Bild b) ist vergleichbar mit dem UQH beim Anreicherungsinverter, wo UQH um den Wert der Einsatzspannung bei Berücksichtigung des Substratsteuerfaktors reduziert ist. γ2 − γ U N + 2φ F + γ 2 / 4 2 U N = U CC − U Ton + γ 2φ F UC = U N + U N = 3V − 0,5V + 0, 4 V U C = 2,82V + (0 , 4 V U C = 2,15V 0, 65V = 2,82V )2 / 2 − 0, 4 V 2 2,82V + 0, 65V + ( 0, 4 V ) / 4 Aufgaben und Lösungen 71 Mit diesem reduzierten H-Signal ergibt sich die folgende Situation beim Ausgangsinverter: UGS,p= 0,85V UCC =3V S D D UC =2,15V S Ip I I Q0 In UQL UQ UGS,n Bild L: 5.7.2 Mit UGS,n = 2,15V > UTn und UGS,p = ⏐-0,85 V⏐ > ⏐UTp⏐ sind beide Transistoren leitend und es fließt ein Strom I. Der vom Wert her kleinste Strom durch die Transistoren bestimmt dabei den Strom I durch den Inverter. Aus den obigen Werten geht hervor, dass dies IDS,p ist. Damit IDS,p = IDS,n wird, geht der n-Kanal Transistor in den Widerstandsbereich (Bild L 5.7.3) wodurch die Ausgangsspannung absinkt. Dabei wird ⏐UDS,p⏐ > ⏐UGS,p - UTp⏐, wodurch der p-Kanal Transistor in den Stromsättigungsbereich gelangt. Der Strom beträgt dabei βp I = I DS , p = (U GS − U Tp ) 2 I = I DS , p = 18,38 µA. 2 I DS,n UGS =2,15V 408 = 300 µA / V 2 2 ( −0,85V + 0,5V ) 2 I DS , n = I DS,n =IDS,p UQL Bild L: 5.7.3 2 (U GS ,n − U Tn ) 2 300 µA / V 2 ( 2,15V − 0,5V ) 2 = 2 = 408µA [uA] 18,38 βn UDS,n Aufgaben und Lösungen 72 Aufgabe 5.8 Dimensionieren Sie die gezeigte Gatter-Schaltung, d.h. bestimmen Sie die Weite der Transistoren, wenn die Lastkapazität CL = 0,1pF innerhalb von 1 ns aufgeladen werden soll. Die elektrischen Daten der Transistoren sind: 2 k n = 100 µA / V ; k p = 40 µA / V 2 ; l min = 0,3 µm . 3V T2 A T8 B T7 D G E C T5 T4 T3 F T1 CL T6 Bild A: 5.8 Lösung zur Aufgabe 5.8: Aus der Anforderung an die Anstiegszeit ergibt sich: tr = C 0,1 ⋅ 10 −12 As / V 1, 2 (1 / V ) ⇒ β p = L 1, 2 (1 / V ) = 1, 2 (1 / V ) −9 βp tr 1 ⋅ 10 s CL β p = 120 µA / V 2 für T2 Aus dem z-Verhältnis von 5,9 resultiert dann die Stromverstärkung für T1 von β n ,1 = z ⋅ β p = 5,9 ⋅ 120 µA / V 2 = 708 µA / V 2 Entsprechend der Serienschaltung von Transistoren ist T3, T4 und T5 2⋅βn,1 = 1416µA/V2 und T6, T7 und T8 3⋅βn,1 = 2124µA/V2 Mit β n = k n ⎛⎜ w⎞ 2⎛ w ⎞ ⎟ = 100 µA / V ⎜ ⎟ und ⎝ l ⎠n ⎝ l ⎠n w⎞ 2⎛ w ⎞ ⎟ = 40 µA / V ⎜ ⎟ resultiert : ⎝ l ⎠n ⎝ l ⎠ β p = k p ⎛⎜ Aufgaben und Lösungen 73 Transistor β (µA/V2) w/l w*(µm) T1 708 7 2,1 T2 120 3 0,9 T3, T4, T5 1416 14 4,2 T6, T7, T8, T9 2124 21 6,3 *lmin beträgt 0,3µm Aufgaben und Lösungen 74 Aufgabe 5.9 Ein IC hat vier Datenausgänge, wodurch beim gleichzeitigen Schalten der Ausgangstreiber große Störspannungen an den Zuleitungswiderständen und -induktivitäten erzeugt werden. Würden Sie als Lösung die Schaltzeiten verlängern oder die Ausgänge gestaffelt schalten? Lösung zur Aufgabe 5.9: Fall 1: Ausgänge mit gestaffelten Verzögerungszeiten I QL1 =IMAX1 ts 2 Hüllkurve I MAX1 0 ts t t m=2,5 t s Bild L: 5.9.1 Fall 2: Alle Ausgänge mit verlängerter Schaltzeit I 4IMAX2 QL2 =IMAX2 t m 2 I MAX2 0 tm t Bild L: 5.9.2 Da zum Umladen an jedem Ausgang die gleiche Ladung benötigt wird gilt: Q L1 = Q L 2 I MAX 1 ⋅ t s / 2 = I MAX 2 ⋅ 2,5t s / 2 bei 4 Ausgängen 4 I MAX 2 = 4 ⋅ I MAX 1 / 2 ,5 = 1, 6 I MAX 1 Fazit: Fall 1 günstiger bei großen Zuleitungswiderständen wegen U = R⋅I Fall 2 günstiger bei großen induktiven Zuleitungen wegen U = LdI/dt Aufgaben und Lösungen 75 Kapitel 6 Aufgabe 6.1 Realisieren Sie die logische Funktion Q = I 1 ⋅ I 2 + ( I 3 + I 4 ) ⋅ ( I 5 + I 6 ) in einer statischen Komplementärschaltung und erstellen Sie dazu das Layout. Verwenden Sie dabei den in Abschnitt 6.1.2 beschriebenen Layoutstil und bestimmen Sie nach Möglichkeit einen gemeinsamen Eulerpfad. Lösung zu Aufgabe 6.1: Q = I1 ⋅ I 2 + ( I 3 + I 4 ) ⋅ ( I 5 + I 6 ) Geg: Kompl. Q = I1 ⋅ I 2 + ( I 3 + I 4 ) ⋅ ( I 5 + I 6 ) break the line change the sign Q = [I 1 ⋅ I 2 ] ⋅ [( I 3 + I 4 ) + ( I 5 + I 6 ) ] Q = [I 1 + I 2 ] ⋅ [I 3 ⋅ I 4 + I 5 ⋅ I 6 ] UCC I2 Euler - Pfad [ I4 , I3 , I1 , I2 , I5 , I6 ] I1 Q I3 I5 I4 I6 Anfang * n-Tr. Q I4 I5 I6 I2 a) Bild L: 6.1.1 I3 I4 I2 I5 I6 UCC I1 I3 I1 b) Anfang p-Tr. * Q Aufgaben und Lösungen Layout-Skizze 76 I4 I3 I1 I2 I5 I6 UCC Metall p - Tr. Q Kontakt n - Tr. Polyzid Bild L: 6.1.3 Aufgaben und Lösungen 77 Aufgabe 6.2 Welche logischen Funktionen können mit der gezeigten Transfer-Gatterschaltung realisiert werden, wenn die Eingangsvariablen, wie gezeigt, verändert werden? A X A Y Q X Y L B H B B H B L B B Q Bild A: 6.2 Lösung zur Aufgabe 6.2: A X Y Bild L: 6.2 A Q X Y Q L B BA H B A + BA = A + B = A ⋅ B B H BA + A = B + A B L BA= A+B B B BA + B A = A ⊕ B Aufgaben und Lösungen 78 Aufgabe 6.3 Bei der in Bild 6.39 gezeigten Kaskadierung von Dekodern entsteht an den ZAusgängen ein verschlechterter Logikpegel. a) Tritt dieser beim L- oder H-Zustand auf? b) Welchen Wert hat dieser Pegel, wenn UTop = -0,45V; φ F = −0,3V ; γ = 0,3 V und UCC = 3V betragen? c) Wie kann Abhilfe geschaffen werden? Lösung zur Aufgabe 6.3 Ein verschlechterter Logikpegel tritt auf, wenn CL auf H d.h. 3V aufgeladen ist und über den p-Kanal-Transistor mit 0V an der Drain und dem Gate entladen werden soll. H (3V) I DS,p H (3V) L (0V) D L (?) S Z CL aus L (0V) Bild L: 6.3.1 Erste Schätzung: L-Pegel ≈ ⏐UTp⏐, denn dann sperrt der Transistor. Genauere Analyse beinhaltet die Wirkung des Substratsteuereffekts B +3V USB 0V D Z S UGB 0V UGS CL U =? QL Bild L: 6.3.2 U GB − U SB − U GS = 0 U SB = U GB − U Tp [ U SB = U GB − U Tpo − γ ( − 2φ F − U SB − mit: γ2 U SB = −U N − + γ U N − 2φ F − γ 2 / 4 2 U N = −U GB + U Tpo + γ − 2φ F − 2φ F ) ] Aufgaben und Lösungen 79 mit den Werten U GB = −3V ; φ F = −0,3V ; U N = 3V − 0, 45V + 0 ,3 V U SB = −2, 78V − U Top = − 0, 45V γ = 0,3 V 0, 6V = 2 , 78V 0, 09V + 0,3 V 2 2, 78V + 0, 6V − 0 , 09V 4 U SB = −2, 28V U SB − U GB − U QL = 0 U QL = U SB − U GB = −2 , 28V + 3V = 0, 72V U QL = 0 , 72V Mögliche Lösung: φ oder UCC D Z S Tr CL Bild L: 6.3.3 Jeder Ausgang wird mit einem n-Kanal-Transistor (Tr) versehen, der getaktet oder mit UCC am Gate für die restliche Entladung von CL sorgt. Aufgaben und Lösungen 80 Aufgabe 6.4 Zeichnen Sie die Schaltung einer programmierbaren Logikanordnung (PLA), die die folgende Wahrheitstabelle realisiert. Welche Funktion wird durch die angegebene Wahrheitstabelle beschrieben? A B C Q1 Q2 L H L H L H L H L L H H L L H H L L L L H H H H L H H L H L L H L L L H L H H H Lösung zur Aufgabe 6.4: UCC UCC A A B B XÜ UCC XÜ X Su A B Xü Xsn Xü L H L H L H L H L L H H L L H H L L L L H H H H L H H L H L L H L L L H L H H H XÜ Volladdierer Aufgaben und Lösungen 81 Aufgabe 6.5 In Bild A: 6.5 ist ein dynamisches Master-Slave-Flip-Flop dargestellt. UCC=3V UCC =3V φ1 φ1 D CA φ1 CL φ2 Q φ2 CA D φ1 M Q CL CA a) φ2 b) S CA φ2 M S Bild A: 6.5 Welche der im Bild gezeigten Realisierungen ist zu bevorzugen? Welche H- und LSpannungen können sich im schlechtesten Fall bei der nicht zu empfehlenden Anordnung an CL einstellen, wenn CL = 2CA ist? Lösung zur Aufgabe 6.5: UCC UCC φ1 φ1 D CA φ1 CA CL D φ1 CA a) CL CA b) Bild L: 6.5.1 Kriterium: Transfer-Elemente sind hochohmig geschaltet und D ändert den Zustand. Bleibt die Ladung an CL erhalten? im Fall a) ja; keine Änderungen im Fall b) kommt es zur Ladungsteilung, wodurch ein reduzierter H-Pegel und ein erhöhter L-Pegel entsteht. Aufgaben und Lösungen φ1 (0V) 3V D (0V) 3V φ1 (3V) 0V 82 UCC φ1 (0V) 3V (3V) CA (0V) CA (3V) CL D UQ UA a) (3V) 0V φ1 (3V) 0V UCC (3V) CA (0V) (0V) CL CA b) Bild L: 6.5.2 Zahlen in Klammern entsprechen der Ausgangssituation; dann ändert sich φ1 und φ1 , so dass die Transfer-Elemente hochohmig geschaltet werden. Ändert sich anschließend D kommt es in Bild a) zur Reduzierung des H-Pegels und in Bild b) zur Erhöhung des L-Pegels. Mit ′ = UQ QGes C Ges = C LU Q + C AU A C A + CL mit C L = 2C A 2U Q + U A ′ = UQ 3 im Fall a) ′ = UQ 2 ⋅ 3V + 0V = 2V 3 im Fall b) ′ = UQ 0V + 3V = 1V 3 Aufgaben und Lösungen 83 Aufgabe 6.6 Bei dem in Bild A: 6.6 gezeigten Stromschalter liegt an den Eingängen eine Spannung von UI = 1,3V und U I = 0,9 V an. Wie groß sind die Ströme I1 und I2 ? 1,3V URp URp I1 I2 1,3V T1 UTn = 0,4V (w/l)1 = (w/l)2 = 3 k n = 150 uA/V 2 0,9V T2 IK = 50 uA UEE < 0V Bild A: 6.6 Quadratische Gleichung: ax 2 + bx + c = 0 ; x= −b± 2 b − 4 ac 2a Lösung zur Aufgabe 6.6 I1 = βn 2 (U I 1 − U S β − U Tn )2 ; I 2 = n (U I 2 − U S − U Tn )2 2 I K = I1 + I 2 Mit U A = U I 1 − U Tn und U B = U I 2 − U Tn ergibt sich daraus: US = 1 (U A + U B ) ± 2 − I 1 1 2 2 (U A + U B ) + U AU B + K 4 2 βn US = 433mV bzw 966mV (966mV kann nicht sein da in diesem Fall US >UI2’ ist). Damit ist : I 1 = 1 2 150 µA / V 3(1,3V − 0, 433V − 0, 4V ) 2 = 49, 0 µA und 2 I2 = 1 2 150 µA / V 3( 0, 9V − 0, 433V − 0 , 4V ) 2 = 1, 0 µA 2 Aufgaben und Lösungen 84 Kapitel 7 Aufgabe 7.1 Die gezeigte FETMOS-Zelle soll zur Speicherung von 2 Bits verwendet werden. Die Einsatzspannungsänderung ∆UTn pro Zustand soll dabei 0,8V betragen. Wie viele Elektronen werden pro Zustand benötigt? Daten: l = 0,6µm; w = 1,0µm; ε (ONO) = 5,5 SG 10 nm n+ CS CB 0,1 um l CK CD ONO SiO2 7 nm n+ 0,1 um Bild A: 7.1 Lösung zur Aufgabe 7.1: Änderung der Einsatzspannung ∆UTn entspricht Änderung der Floating-Gatespannung ∆UFG. SG Q FG n+ Bild L: 7.1.1 Spiegelladungen n+ Aufgaben und Lösungen ∆U FG = ′ = CK 85 ∆Q FG = CK + CB + CS + CD ε ( ONO )ε 0 d ox C K = 4,87 fF µm 2 = fF µm 2 C K + CG 5,5 ⋅ 8,854 ⋅ 10 −14 F cm −1 10 ⋅ 10 − 7 cm = 4,87 ⋅ 10 − 7 F cm 2 × 0, 6 µm × 1, 0 µm = 2,92 fF ′ = C S′ + C D ′ + C B′ = CG C G = 4,93 ∆Q FG ε ox ε o d ox = 3,9 ⋅ 8,854 ⋅ 10 −14 F cm −1 7 ⋅ 10 −7 cm 0,8 µm × 1, 0 µm = 3,95 fF As ∆Q FG = ∆U FG ⋅ (C K + C G ) = 0,8V ⋅ 6,87 ⋅ 10 −15 V ∆Q FG = 5,50 ⋅ 10 −15 As Daraus ergibt sich die Zahl der Elektronen zu Z = 5, 50 ⋅ 10 −15 As 1, 6 ⋅ 10 −19 As = 34.375 = 4,93 ⋅ 10 − 7 F cm 2 Aufgaben und Lösungen 86 Aufgabe 7.2 Für die gezeigte statische Speicherzelle sollen die maximal zulässigen Widerstandswerte bestimmt werden. Der Spannungsabfall an R darf im gesamten Temperaturbereich (0oC bis 90oC) auf keinen Fall 1V überschreiten. Als dominierender Leckstrom ist bei den Transistoren nur der Unterschwellstrom zu berücksichtigen. Daten der Transistoren: UTon(0°C) = 0,6V; UTon(90°C) = 0,51V; βn(0°C) = 150µA/V2; βn(90°C) = 110µA/V2; n = 2 UCC =3V ∆ U=1V WL R WL R L H T1 T2 ~0V IDS,n BL BL Bild A: 7.2 Lösung zur Aufgabe 7.2: a) IDS worst case /φ −U 2 (U GS −U Tn ) / φt n (1 − e DS t ) I DS = β n ( n − 1)φ t e U GS = 0; φt = Ausdruck (1 − e −U DS / φt ) vernachlässigbar kT ( 90°C ) = 31,3 mV q I DS ( 0°C ) = 150 µA / V = 2,37 ⋅ 10 2 −13 I DS ( 90°C ) = 110 µA / V 2 ⋅ ( 23,5 ⋅ 10 φ t ( 0°C ) = 23,5 mV 600 mV 2 − 47 mV ) V e −3 2 A ⋅ ( 31,3 ⋅ 10 −3 2 2 ) V e − 510 mV 62 , 6 mV − = 3,12 ⋅ 10 11 A d.h. worst case - wie erwartet - bei 90°C (post.Temp.Koeff. im Unterschw.) b) R≤ 1V 3,12 ⋅ 10 −11 A = 32,0⋅109 Ω Bemerkung: Durch Erhöhung der Einsatzspannung von T1 und T2 können die Unterschwellströme weiter reduziert und damit die Widerstände R vergrößert werden. Aufgaben und Lösungen 87 Aufgabe 7.3 Die Ein-Transistor-Zelle eines DRAMs kann durch folgendes vereinfachtes Ersatzschaltbild dargestellt werden: Al-1 BL Bit Line (W) Bit Line Contact n+ P-Well 0V STI Word Line (WSI / n+ poly) Oxide Collar 1,8V " H" 0V " L" n Tr. 0V/1,8V n+ poly Buried N-Well n +0,9V WL p-Well 0V CS = 45fF +0,9V Capacitor Insulator n Buried Plate p-Si Bild A: 7.3 a) Bestimmen Sie den Unterschwellstrom des mit 0V am Gate abgeschalteten nTransistors unter "worst case" Bedingungen. b) Verwenden Sie den "worst case" Fall, um die Refreshzeit zu bestimmen. Hierbei ist davon auszugehen, dass ein reduzierter H-Pegel von 1,5 V und ein erhöhter LPegel von 0,3 V noch akzeptabel ist. c) Wie verbessern sich die Werte, wenn eine Source-Bulkspannung, d.h. zusätzlich eine Spannung an "p-Well" von – 1 V verwendet wird? Daten des n-Transistors 27o C 90o C IDS (gemessen bei UGS = 0,6 V) 250 pA 4,8 nA UTon (p-Well an 0 V) 1,0 V 0,87 V γ 0,3 V 0,3 V S 120 mV/Dek 145 mV/Dek 2 φF 0,82 V 0,76 V 2 2 n = 1+ C ′j ′ C ox Aufgaben und Lösungen 88 Lösung zur Aufgabe 7.3: a) worst case Unterschwellstrom? BL WL = 0V I D S BL WL = 0V I UGS =-0,3V 0,3V S 0V 0V +0,9V +0,9V selbstbegrenzend worst case UGS = 0V Bild L: 7.3.1 U GS = 0V ; Refresh worst case: T = 90°C 600 mV ( Meßwert ) ≈ 4 Dekaden Stromreduzierung 145 mV / Dekade I DS = 4 ,8 nA/ 10 4 = 480 ⋅ 10 −15 A; − ∆t ≈ 45 ⋅ 10 15 As / V ∆t ≈ C ∆U I DS 0, 3V − 480 ⋅ 10 15 A ∆t = 28,1ms Genauere Betrachtung I DS = β n ( n − 1)φ t2 e (U GS −U Tn ) / φ t n I DS (U GS = 0, 6V ) I DS (U GS = 0V ) =e ; UDS >100 mV 600 mV 31, 4 mV ⋅ 2 = 14,1 ⋅ 10 3 U SB = 0V o 3 I DS ( 90 , U GS = 0V ) = 4,8 nA / 14,1 ⋅ 10 = 340 ⋅ 10 ∆t = 45 ⋅ 10 −15 As V c) D 1,5V 1,8V b) 1,8V 0 , 3V −15 A 340⋅10 mit -1V an p-Well d.h. USB = 1V = 39, 7 ms −15 A Aufgaben und Lösungen 89 U Tn = U Ton + γ ( 2φ F + U SB − 2φ F ) = 0,874V + 0,3 V ( 0 , 76V + 1V − 0, 76V ) = 0,874V + 0,136V Verbesserung ca. 1 Dekade d.h. ∆t ≈ 300 ms genauere Betrachtung: log USB =0V IDS [A] USB =+1V 340 10 -15 39 10 136mV -15 145mV/Dek 0V UTn =0,87V Bild L: 7.3.2 I DS (U SB = 0 ) I DS (U SB = 1V ) =e 136 mV 31, 4 mV ⋅ 2 = 8, 72 U GS = 0V −15 A = 39 , 0 ⋅ 10 −15 A I DS (U SB = +1V ) = 340⋅10 8 , 72 ∆t = 45 ⋅ 10 −15 As V 90°C 0 , 3V −15 A 39 , 0⋅10 = 346 ms UGS Aufgaben und Lösungen 90 Aufgabe 7.4 Dargestellt ist eine Ein-Transistor-Zelle eines DRAMs. Die n+-Polyseite der Kapazität kann auf 1,8 V bzw. 0 V aufgeladen werden. Dadurch ist es möglich, dass ein unerlaubt großer Leckstrom durch den gezeigten parasitären n-Kanal Transistor fließt. Bestimmen Sie: a) Welches die "worst case" Spannungskonstellation, b) die Einsatzspannung des parasitären Transistors bei dox = 7nm (oxid collar) sowie wenn c) dox auf 30 nm vergrößert wird und d) eine Spannung von – 1 V an die p-Wanne (p-Well) gelegt wird. Al-1 Bit Line (W) Bit Line Contact n+ P-Well 0V / -1V STI Word Line (WSI / n+ poly) Oxide Collar WL p-Si Bild A: 7.4 Capacitor Insulator n Buried Plate 17 -3 NA=2x10 cm p-Well n+ poly Buried N-Well n +0,9V 1,8V/0V BL CS UFB= 0,8V +0,9V Aufgaben und Lösungen 91 Lösung zur Aufgabe 7.4: a) worst case: 1,8V D 0V USB S UGS CS +0,9V Bild L: 7.4.1 d ox = 7 nm; b) 0V am p − Well −3 17 N 2 ⋅ 10 cm = 885 mV 2φ F = 2φ t ln A = 2 ⋅ 26 mV ln −3 10 ni 1, 45 ⋅ 10 cm ε o ε ox ′ = C ox γ = = 1 ′ C ox = dox 8,85 ⋅ 10 −14 As / V ⋅ cm ⋅ 3,9 7 ⋅ 10 −7 cm = 493 ⋅ 10 −9 1, 6 ⋅ 10 −19 As ⋅ 2 ⋅ 1017 cm − 3 ⋅ 2 ⋅ 11,9 ⋅ 8,85 ⋅ 10 −14 As cm 1 493 ⋅ 10 − 9 F cm 2 U Tn = U FB + 2φ F + γ 2φ F + U SB = −0,8V + 0,855V + 0,526 V 0,885V + 0,9V = UTn = 0,758V dox = 30 nm U Tn = −0,8V + 0,855V + UTn = 3,07V d) cm 2 qN A 2ε o ε Si γ = 0,526 V c) F zusätzlich USB = 1,9V UTn = 3,82V 30 0,526 V 7 0,885V + 0,9V = Aufgaben und Lösungen 92 Aufgabe 7.5 Bestimmen Sie die Lesesignale ∆UL in dem dargestellten Open-Bit-Line Konzept, wenn in der Zelle Z WL1 WL256 BL ∆ UL WL256 WL1 RBL SA Z CS US CB CB Bild A: 7.5 ein H-Pegel von 1,8V bzw. ein L-Pegel von 0V gespeichert ist. Daten: CS = 35fF; CB = 200fF; Vorladen der Bit-Leitungen auf 1,8V/2 = 0,9V. Lösung zur Aufgabe 7.5: ∆U L = U L ( BL ) − U B ( RBL ) ∆U L = C S U S + C BU B − U B ( RBL ) CS + CB ∆U L = (C S + C B ) CS C S U S + C BU B (U S − U B ) UB = − CS + CB CS + CB CS + CB ∆U L = 35 ⋅ 10 −15 As V [1,8V ( bzw. 0V ) − 0,9V ] −15 As 235 ⋅ 10 V = ± 134mV. Das Lesesignal ist relativ groß, da nur 256 Zellen mit den Biltleitungen verbunden sind. Aufgaben und Lösungen 93 Aufgabe 7.6 Gezeigt ist von einem DRAM der Ausschnitt aus dem Zellenfeld. WL1 WL 256 BL -1V -1V CS CS Bild A: 7.6 Wie groß muss die Wortleitungsspannung UWL mindestens sein, damit in die Speicherzelle ein H-Pegel von 1,8V gelangen kann? Transistordaten: UTon = 1,1V; γ = 0,8 V ; 2φ F = 0 ,93V Lösung: UWL=? 1,8V -1V USB =2,8V US =1,8V Bild L: 7.6.1 U WL = U H + U Ton + γ ( 2φ F + U SB − 2φ F ) U WL = 1,8V + 1,1V + 0 ,8 V ( 0,93V + 2 ,8V − 0, 93V UWL = 3,67V ) Aufgaben und Lösungen 94 Aufgabe 7.7 Dargestellt sind typische Wortleitungs“Bootstrap“-Treiber eines DRAMs. Wie groß sind die Spannungen an den Gates von Tr0 und Tr1 sowie an den Wortleitungen WLO und WL1 vor und nach der Änderung von φWL von 0V auf 3,8V? Werte: CP = 9fF; CGS = CGD = 26fF; UTn = 0,6V Substratsteuerfaktor vernachlässigbar. φ WL 3,3V 0V CGD L Cp 1 Cp Bild A: 7.7 Tr0 WL 0 CGS CGD H 1 0V Bit-Leitung 3,3V 3,3V 3,8V Tr1 WL1 CGS CS 1-Tr. Zelle Aufgaben und Lösungen 95 Lösung zur Aufgabe 7.7: a) Spannung am Gate von Tr0 und WL0 beträgt jeweils 0V, unabhängig ob φWL = 0V oder 3,8V beträgt. b) Spannung am Gate von Tr1 undWL1 mit φWL = 0V φ WL =0V 3,3V 3,3V D UGS =UTn S 2,7V Tr1 0V WL1 Bild L: 7.7.1 Spannung am Gate von Tr1 und WL1 mit φWL = 3,8V φ WL 3,8V 3,3V 3,3V Cp 3,3V CGD WL CGS 3,3V S D Cp WL CGS +CGD Bild L: 7.7.2 C GS + C GD 52 fF U GS ,1 = φWL + 2, 7V = 3,8V + 2, 7V = C P + C GS + C GD 60 fF U GS ,1 = 5,99V und damit WL1 = 3,8V Aufgaben und Lösungen 96 Kapitel 8 Aufgabe 8.1 Gegeben ist der gezeigte einfache Verstärker mit folgenden Daten: IDS = 100 µA; βn = 1000 µA/V2; λn = 0,1 V-1; RL = 100kΩ; ui = 50 µV; (Transistor in Sättigung) Bild A: 8.1 Wie groß ist bei niedrigen Frequenzen die Ausgangswechselspannung und Verstärkung in dB? Lösung zur Aufgabe 8.1: Ω Bild L: 8.1 Aufgaben und Lösungen 97 U DS = 18V − R L I DS = 8V gm = 2 I DS β n (1 + λ nU DS ) = 2 ⋅ 10 − 4 A ⋅ 1000 ⋅ 10 − 6 A / V [1 + 0,1 ⋅ (1 / V )8V ] g m = 6 ⋅ 10 − 4 A / V λ n I DS 0,1V −1 ⋅ 100 ⋅ 10 − 6 A go = = = 5,56 ⋅ 10 − 6 A / V − 1 1 + λ nU DS 1 + 0,1V 8V d.h. ro = 1 / g o = 180 kΩ −6 −6 g = g o + g l = 5,56 ⋅ 10 A / V + 10 ⋅ 10 A / V = 15, 56 ⋅ 10 −4 gm 6 ⋅ 10 A / V uo = − u =− ⋅ 50 µV = −1,93mV −6 g i 15,56 ⋅ 10 A / V d.h. uo ui = −38, 6 −6 A/V 20 log 38, 6 = 31, 7 dB Um eine hohe Verstärkung zu erreichen benötigt man große Ausgangswiderstände; ro ist begrenzt durch die Kanallängenmodulation und RL durch die Größe der Versorgungsspannung. Lösung: Ersatz von RL durch eine Stromquelle. Aufgaben und Lösungen 98 Aufgabe 8.2 Bei welchem Strom I geht bei Raumtemperatur die Stromspiegelschaltung von Sättigung in den Unterschwellstrombereich? Bild A: 8.2 Daten der Transistoren bei R.T.: kn = 120 µA/V2; w/l = 10; n = 2; UDS > 1V Lösung zur Aufgabe 8.2: −U ) / φ n w 2 (U I DS = k n ( n − 1)φ t e GS Tn t l für U GS = U Tn Übergang in den Unterschwellstrombereich w I DS = k n ( n − 1)φ t2 l 2 ( I DS = 120 µA / V 10 ⋅ 26 ⋅ 10 −3 ) 2 V 2 = 0,81µA Aufgaben und Lösungen 99 Aufgabe 8.3 Gegeben ist der dargestellte CMOS-Verstärker. Der Arbeitspunkt wird durch eine Referenzstufe eingestellt, so dass sich Herstellungstoleranzen kompensieren. Bild A: 8.3 Die Daten der symmetrisch gestalteten Transistoren sind: N-Kanal: βn = 1000 µA/V2; UTn = 0,5 V; λn = 0,05 V-1; P-Kanal: Gesucht: βp = 1000 µA/V2; UTp = - 0,5 V: λp = 0,05 V-1; Die Verstärkung der Stufe bei niedrigen Frequenzen. Die Einflüsse von C und R sind vernachlässigbar. Lösung zur Aufgabe 8.3 Arbeitspunkt: Da In,r = -Ip,r ist beträgt UA ≈ UCC / 2 = 1,5V Es fließt ein Strom von In = -Ip durch den Verstärker. Dieser hat einen Wert von I DS , n = βn (U GS − U Tn ) 2 I DS , n = − I DS , p = 500 µA 2 1000 µA / V = 2 2 (1,5V − 0,5V ) 2 Die Übertragungs- und Ausgangsleitwerte betragen: g m,n = 2 I DS , n β n (1 + λ nU DS ) g m,n = 2 ⋅ 500 µA ⋅ 1000 µA / V 2 (1 + 0, 05V −1 ⋅ 1,5V ) g m , n = g m , p = 1, 04 ⋅ 10 g o,n = −3 A/V λ n I DS 0 , 05V −1 ⋅ 500 µA = −1 1 + λ nU DS 1 + 0, 05V 1,5V g o , n = g o , p = 2 ,33 ⋅ 10 −5 A/V Aufgaben und Lösungen 100 Hinweis zu Strom- und Spannungsrichtung beim Kleinsignal-Ersatzschaltbild von nund p-Kanal Transistor Bei den dargestellten einfachen Verstärkern sind die aktiven Elemente jeweils vertauscht. Der Einfachheit halber werden sehr hochohmige Lastwiderstände verwendet. Steigt die Eingangsspannung an, führt dies in beiden Fällen zu einer Reduzierung der Ausgangsspannung. Fällt dagegen die Spannung an den Eingängen, führt dies jeweils zu einer Erhöhung der Ausgangsspannung. Werden die aktiven Elemente, wie bei dem CMOS-Verstärker vorgesehen gleichzeitig angesteuert, verhalten sich diese damit so, als wären sie wechselspannungsmäßig parallel geschaltet. Demnach gilt für den Verstärker das folgende Ersatzschaltbild Bild L: 8.3.3 Aufgaben und Lösungen uo ui uo ui 101 =− −3 g m,n + g m, p g 1, 04 ⋅ 10 A / V =− m =− −5 g o , n + g op go 2, 33 ⋅ 10 A / V = −44 , 6 ( 32, 9 dB ) Aufgaben und Lösungen 102 Aufgabe 8.4 Bestimmen Sie die Weite des gezeigten Source-Folger-Transistors, wenn raus = 50Ω betragen soll. Um die Kanallängenmodulation zu reduzieren wird eine relativ große Gatelänge von 1,5µm verwendet. Es kann dadurch angeommen werden, dass λn⋅ UDS « 1 ist. Bild A: 8.4 Lösung zur Aufgabe 8.4: raus ≈ 1 g m ,1 = 1 2 I DS β n (1 + λ nU DS ) ≈ 1 2 I DS k n w / l w 1 1 = = 2 l 2 I DS k n raus 2 ⋅ 10 − 3 A ⋅ 100 ⋅ 10 − 6 A / V 2 ⋅ 50 2 (V / A) 2 w 3 = 2 ⋅ 10 l mit l = 1,5µm resultiert eine Weite von w = 3mm Durch Erhöhung von IDS kann zwar das w/l-Verhältnis reduziert werden jedoch steigt der Leistungsverbrauch an. Aufgaben und Lösungen 103 Kapitel 9 Aufgabe 9.1 Berechnen Sie den Kleinsignal-Ausgangswiderstand der dargestellten verbesserten Stromsenke bei niedrigen Frequenzen, wenn T3 und T2 identisch aufgebaut sind. Bild A: 9.1 Lösung zur Aufgabe 9.1: Kleinsignal-Ersatzschaltbild Bild L: 9.1 Aufgaben und Lösungen 104 Knotengleichung: für Pfad I − u T + u1 + u 2 = 0 I) 1 1 − u T + ( i o − g m ,1u gs ,1 ) + io =0 g o ,1 g m, 2 für Pfad II II) − u 2 − u gs ,1 − u 3 = 0 g m,3 i − o − u gs ,1 − u =0 g m,2 g o , 3 gs , 3 − io u gs , 3 = mit io g m, 2 − u gs ,1 − g m,2 g m,3 i =0 g m, 2 g o ,3 o u gs ,1 = − d.h. 1 io g m,2 − g m,3 1 i g m, 2 g o,3 o in I) eingesetzt und nach raus aufgelöst raus = = ui io 1 g o ,1 + g m ,1 ⎡ ⎢1 + g m , 2 ⎣⎢ g o ,1 1 g ⎛ ⎜1 + m, 2 ⎜ g o, 2 ⎝ ⎞⎤ ⎟⎥ ⎟⎥ ⎠⎦ wobei gm,3 = gm,2 und go,3 = go,2 gleiche Werte besitzen. D.h. die Transistoren T3 und T2 sind identisch mit g m, 2 g o,2 raus ≈ raus ≈ »1 1 g o ,1 und + g m ,1 g o ,1 g o , 2 g m ,1 g o ,1 g o , 2 = g m ,1 ro ,1 ro , 2 g m ,1 g o ,1 »1 Aufgaben und Lösungen 105 Aufgabe 9.2 Bestimmen Sie bei niedrigen Frequenzen die Verstärkung der dargestellten Verstärkerstufe (T5 befindet sich in Stromsättigung). Daten der Transistoren: β p (T1 bis T4 ) = 800 µA / V 2 ; λ (T1 bis T5 ) = 0, 01V −1 ; β 5 = 5000 µA / V 2 Es kann davon ausgegangen werden, dass bei allen Transistoren U DS λ « 1 ist. Bild A: 9.2 Lösung zur Aufgabe 9.2: In Analogie zu Beziehung (8.8) hat der Leitwert der verbesserten Stromquelle einen Wert von g o, p ≈ g o ,1 g o , 2 g m ,1 Bild L: 9.2 uo ui =− g m ,5 g o ,5 + g o , p Aufgaben und Lösungen 106 g m,5 = 2 I DS , 5 β 5 (1 + λ 5U DS ) ≈ 2 I DS , 5 β 5 g m,5 ≈ 2 ⋅ 100 ⋅ 10 − 6 A ⋅ 5000 ⋅ 10 − 6 A / V 2 g m , 5 ≈ 10 − 3 A / V 2 ⋅ 100 ⋅ 10 − 6 A ⋅ 800 ⋅ 10 − 6 A / V 2 2 I DS ,1 β 1 = g m ,1 ≈ g m ,1 ≈ 4 ⋅ 10 − 4 A / V go = I DS λ 1 + λU DS ≈ I DS λ = 100 ⋅ 10 g o , 5 = g o ,1 = g o , 2 = 10 d.h. g o, p = 10 −6 A / V ⋅ 10 4 ⋅ 10 −4 −6 −6 ui uo ui g m,5 g o ,5 = 60 dB =− 10 −6 A/V = 10 −6 A/V = 0, 25 ⋅ 10 −8 A / V vernachlässigbar = −10 3 A/V 10 −3 A / V −1 A/V somit ist: ≈− A ⋅ 0, 01V A/V gegenüber g o , n uo −6 Aufgaben und Lösungen 107 Aufgabe 9.3 In dem gefalteten Kaskode-Verstärker (Bild 9.14) wird eine sog. wrap-around Schaltung verwendet (Bild A.9.3). Bild A: 9.3 Bestimmen Sie den Spannungsbereich UB so, dass gewährleistet ist, dass sich beide Transistoren in Stromsättigung befinden. Lösung zur Aufgabe 9.3 δ δ δ δ δ Bild L: 9.3 Übergang Stromsättigung: (UGS - UTn) = UDS Mit UGS = UTn + δ hat UDS(MIN) einen Wert von δ Aus Bild L 9.3 resultiert eine Spannung von U B ( MIN ) = δ 1 + U Tn + δ 2 mit δ 2 = U DS , 2 = U Tn U B ( MAX ) = δ 1 + 2U Tn Aufgaben und Lösungen 108 Kapitel 10 Aufgabe 10.1 Bestimmen Sie die minimale mögliche Versorgungsspannung UCC der dargestellten BICMOS-Treiber UCC UI T2 UI UCC T2 UQ UQ T1 T1 a) b) Bild A: 10.1 Lösung zur Aufgabe 10.1: UCC UIH= UCC -UBE UCC UIH= UCC -UBE T2 T2 UTn UQ T1 UTn UQ T1 UBE a) b) Bild L: 10.1 UQ(MAX) ist in beiden Fällen ≈ UCC - UBE . Annahme: U IH ( MIN ) = U CC − U BE Mit UI = UQ(MAX) ergibt sich im Fall a) Fall b) UIH ≥ UTn + UBE UIH ≥ UTn UCC - UBE ≥ UTn + UBE UCC - UBE ≥ UTn UCC ≥ UTn + 2UBE UCC ≥ UTn + UBE Aufgaben und Lösungen 109 Aufgabe 10.2 Die im Bild dargestellte Stromquelle mit den Strömen IB1 und IB2 ist von der Versorgungsspannung UCC unabhängig, wenn die Kanallängenmodulation vernachlässigt wird. UCC start - up IB2 UCC I B1 UGS,2 UGS,1 I B1 Bild A: 10.2 Leiten Sie die Beziehung für den Strom IB1 als Funktion der Transistorgeometrien her, wenn (w/l)3 = (w/l)4 und (w/l)2 > (w/l)1 ist. Es ist davon auszugehen, dass alle Transistoren in Sättigung sind. In erster Näherung können der Substratsteuereffekt und die Kanallängenmodulation vernachlässigt werden. Lösung zur Aufgabe 10.2: [ ] [ ] I B1 = 2 1⎛w⎞ ⇒ U GS , 2 = ⎜ ⎟ k n U GS , 2 − U Tn 2 ⎝ l ⎠2 I B2 = 2 1⎛w⎞ ⇒ U GS ,1 = ⎜ ⎟ k n U GS ,1 − U Tn 2 ⎝ l ⎠1 I B1 = U GS ,1 − U GS , 2 R = ( w / l )1 k n − ⎡ 1 2 I B1 ⎢ − ⎣ ( w / l )1 k n R ⎤ 1 ( w / l ) 2 k n ⎥⎦ 2 ⎤2 ⎥ ⎦⎥ 2I B2 ( w / l )1 k n (w / l)2 kn R ⎡ ⎛ w ⎞ −1 2 ⎛ w ⎞ −1 I B1 = −⎜ ⎟ ⎟ 2 ⎢⎜ ⎝ l ⎠2 k n R ⎣⎢ ⎝ l ⎠1 2 (w / l) 2 kn 2 I B1 ⎛w⎞ =⎛w⎞ ⇒ I ⎜ ⎟ ⎜ ⎟ B1 = I B 2 ⎝ l ⎠3 ⎝ l ⎠ 4 mit: I B1 = 2I B2 2 I B1 + U Tn + U Tn Aufgaben und Lösungen 110 Aufgabe 10.3 Die dargestellte Schaltungsrealisierung stellt eine Variante der in Bild 10.24 vorgestellten Bandabstand-Spannungsquelle dar. UCC nT UBE,2 UBE,1 R1 Bild A: 10.3 Bestimmen Sie die Spannung URef unter der Voraussetzung eines idealen Verstärkers. Lösung zur Aufgabe 10.3: U Ref = U BE , 2 + I ( R3 + R 2 ) U BE ,1 − U BE , 2 I = da U a = U b ist R3 R ⎞ ⎛ U Ref = U BE , 2 + ⎜⎜ 1 + 2 ⎟⎟ ∆U BE R3 ⎠ ⎝ mit: ∆U BE = U BE ,1 − U BE , 2 = kT ln mn q und Verwendung von Beziehung (10.26) liefert die Schaltung eine Referenzspannung von R ⎞ kT ⎛ U Ref = U go − NT + ⎜⎜ 1 + 2 ⎟⎟ ln mn . R3 ⎠ q ⎝ R ⎞k ⎛ Wird ⎜⎜ 1 + 2 ⎟⎟ ln mn = N gewählt, resultiert eine von der Temperatur nahezu unR3 ⎠ q ⎝ abhängige Spannung. Aufgaben und Lösungen 111 Aufgabe 10.4 In Bild 10.39 ist eine einfache MOS-Stromverstärkerstufe mit Kleinsignal-Ersatzschaltbild dargestellt. Leiten Sie die Übertragungsfunktion io / ig her. (Stromrichtung io verändert gegenüber Buchausgabe 2003) Lösung zur Aufgabe 10.4: UCC io ig G ig i2 C ü a) Cgs ig i1 io b) ugs S Bild L:10.4 am Knoten a) i g − i1 − i 2 = 0 i g − jω C gs u gs − jω C ü u gs = 0 I) i g − jω ( C gs + C ü ) u gs = 0 am Knoten b) i 2 − g m u gs + i o = 0 jω C ü u gs − g m u gs + i o = 0 II) u gs ( jω C ü − g m ) = − i o ugs von II nach I liefert β ( jω ) = wobei io ig gm ugs S b) a) D g m (1 − j = ω ) ωz jω ( C gs + C ü ) Aufgaben und Lösungen 112 ωz = ist. Da im Allgemeinen gm Cü ω « 1 ist, resultiert ωz β ( jω ) = β ( jω ) = gm jω ( C gs + C ü ) 2 I DS β n (1 + λ nU DS ) ~ I DS 1 2 jω ( C gs + C ü ) Die Transitkreisfrequenz hat dabei einen Wert bei io = ig von ωT = ωT = gm C gs + C ü 2 I DS β n (1 + λU DS ) ~ I DS 1 2 C gs + C ü Aufgaben und Lösungen 113 Aufgabe 10.5 In Bild 10.35 ist eine einfache bipolare Verstärkerstufe mit Kleinsignal-Ersatzschaltbild dargestellt. Leiten Sie die Übertragungsfunktion uo/ui her, wenn parasitäre Widerstände vernachlässigbar sind. Lösung zur Aufgabe 10.5: UCC gol =0 B ui CL uo C i2 gm ui i1 ui i3 go i4 E Bild L: 10.5 i1 − i 2 − i3 − i 4 = 0 jω C jc ( u i − u o ) − g m u i − g o u o − jω C l u o = 0 ω u ( jω ) ωz = ao a( j ω ) = o ω u i ( jω ) 1+ j ωβ 1− j ao = − ωβ = g m,n go go Cl =− = I C / φt U = − AN ≠ I C I C / U AN φt IC U AN C l U uo Cl E b) a) Cjc ~ IC I I C ω T = a o ω β = AN = C ~ IC φ t U AN C l φ t Cl Aufgaben und Lösungen 114 Aufgabe 10.6 Vergleichen Sie die Eingangskapazitäten von einem bipolaren- und einem MOSTransistor bei einem Strom von jeweils 1mA. Daten: entspricht τN = 5,3ps Bipolarer Transistor: UBE = 0,85V; ft = 30GHz MOS-Transistor: ′ = 4 fF / µm 2 ; kn = 120µA/V2; UGS - UTn = 1,0V; C G l = 0,15µm Lösung zur Aufgabe 10.6: Kleinsignalkapazität: Basis-Emitter C be = τ N I C / φ t + C je ≈ τ N I C / φ t C be ≈ C be ≈ C be ≈ 1 U BE 1 U BE U BE ∫ o U BE ∫ o τN I dU φt C τN U / φt 1 τ I I SS e dU = φt U BE N C 1 ⋅ 5,3 ⋅ 10 −12 s ⋅ 10 − 3 A = 6, 24 fF 0,85V Kleinsignalkapazität: Gate - Source 2 C ′ ⋅ w ⋅ l; 3 ox w 2 2 ′ ⋅ C G = C ox ⋅l ; l 3 CG = CG = I DS = kn w (U GS − U Tn )2 2 l 2 I DS w = 2 l k n (U GS − U Tn ) I DS 4 ′ l2 C ox 3 k n (U GS − U Tn ) 2 10 3 µA 4 ⋅ 4 ( fF / µm 2 ) ⋅ ( 0,15 µm ) 2 3 120 µA / V 2 ⋅ 1V 2 C G = 1, 0 fF CG = d.h. für dieses Beispiel: C be ≈ 6 ⋅ C G Aufgaben und Lösungen 115 Aufgabe 10.7 Gesucht wird der Einfluß, den eine Offset-Spannung bei den Transistoren T1 und T2 auf die Referenzspannung URef (Bild 10.30) hat. Lösung: UGS,1 ist um den Wert der Offset-Spannung verändert. Demnach ist UEB,1+ UGS,1 ± Uoff = UGS,2+I1R1+UEB,2, wodurch ein Strom von I1 = U EB ,1−U EB , 2 R1 U ref = U EB , 3 + ± U off R1 = U off 1 kT und eine Referenzspannung von ln n ± R1 q R1 R 2 kT R ln n + 2 U off resultiert. R1 q R1