Alte integrierte Schaltkreise zu neuem Leben erwecken

Werbung

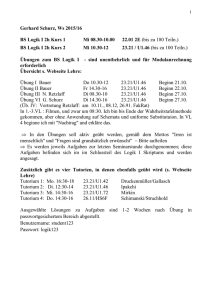

III1Technik III1Trends ASIC -Design: Alte integrierte Schaltkreise zu neuem Leben erwecken Applikationsspezifische Schaltungen, deren Fertigung der Halbleiterhersteller aufgekündigt hat, können mit Hilfe von spezialisierten Dienstleistungsunternehmen auf neue Halbleitertechnologien umgestellt und weiter gefertigt werden. Aufwendige Redesigns kompletter Platinen sind damit vermeidbar. Design-Ingenieure erarbeitet werden, um die hundertprozentig gleiche Funktionalität und das gleiche Timing zu gewährleisten. Das gilt ebenso für Busse. Es war vor einigen Jahren noch üblich, mit TristateBussen mehrere Teilnehmer an einem Datenbus kommunizieren zu lassen. Diese Technik wird in modernen ASICs Der IP·Core als Black-Box kaum oder gar nicht mehr verwendet, so dass auch die Zellen, die diese Es ist seit Jahren üblich, dass Intellec- Kommunikation unterstützten, heute nicht tual-Property-Anbieter genau einen mehr verfügbar sind. Diese Busse müssen ASIC-Entwurf anbieten und bezahlt dann häufig in ihrer Architektur geändert werden. Das führt zu Laufzeitbekommen. Bei einer TechnologieUmsetzung können diese IPs aber nicht Veränderungen. Außerdem müssen bei Hersteller elektronischer Geräte werden so betrachtet werden, wie das z.B. für den Simulationen Signale tief im Design mit der Tatsache konfrontiert, dass die einen selbst entworfenen digitalen beobachtet und deren Logik angepasst hierin verwendeten ASICs und werden. Selbst wenn man auf eine Schaltungsblock zutrifft. Eine DesignHalbleiterkomponenten mit der Zeit Technologie wechselt, die weiterhin Datenbasis kann z.B. einen 8-bit-Staneinfach vom Markt verschwinden. Die Tristate-Busse gestattet, ist deren für die Fertigung verwendeten zeitliches Verhalten anders, da die Halbleitertechnologien werden Tristate-Leitungen starke kapazitipermanent verbessert, und beve Lasten bilden. Diese umzulastehende Halbleitergenerationen den, stellt unterschiedliche Anauf neuen Fertigungsstraßen weiter forderungen an die treibende zu fertigen, ist zum Teil technisch Logik. Bei den Simulationen kann nicht möglich bzw. macht in es dadurch zu erheblichen Timingmanchen Fällen wirtschaftlich Verletzungen kommen. betrachtet keinen Sinn mehr. Idealerweise wird die TristateDamit verschwinden die ASICs in Struktur in eine Multiplexerder Regel mit einer Struktur umgewandelt. Hierfür Vorankündigungszeit von sechs sind allerdings Erfahrung und Monaten vom Markt. Fingerspitzengefühl nötig. MixedWer als Geräte-Entwickler seine Signal-ICs lassen sich prinzipiell Produkte weiter fertigen will, muss ebenso in neue Techreagieren. Prinzipiell stehen ihm nologien übertragen, der dabei zwei Möglichkeiten offen: Die Alle rot markierten ICs auf dieser Einschubplatine wurden neu Aufwand ist jedoch erheblich größer: entwickelt. erste besteht in Transistormodelle in bestehenden einem letzten Einkauf einer größeren analogen Schaltungsnetzlisten lassen sich Menge und deren Einlagerung. Das dardprozessor enthalten, wie er für nicht einfach beim Technologiewechsel bedeutet die Bindung von Kapital für die Millionen Stück verwendet wurde. austauschen. Beispielsweise wird die Lagerhaltung. Die Lagerung von Dieser wurde im ursprünglichen Design Simulation eines Operationsverstärkers, Schaltkreisen in Gehäusen muss unter nur als nicht synthesefähiges Verder in einer 2-llm- Technologie engen klimatischen Umgebungsbedinhaltensmodell eingebaut, in seiner entwickelt wurde, bei direkt skalierten gungen erfolgen. Gleichzeitig wirkt dem elektrischen Umgebung simuliert und Kanalweiten der Transistoren in einer Vorratskauf im großen Stil die beim Place&Route in die umgebende 0,6-µm- Technologie andere Ergebnisse Einführung der RoHS-konformen NorLogik als Hardmakro eingefügt. Eine liefern. Sensiblere Schaltungen wiederum men entgegen. Eingelagerte BaueleNetzliste hat es nie gegeben. funktionieren nach einer Technologiemente, die der neuen Norm nicht entIn digitalen ASICs finden sich regelSkalierung gar nicht mehr. Grundsätzlich sprechen, müssen vor dem Sommer 2006 mäßig Embedded-RAM-Speicher. Diese aber ist das Vorhandensein der Netzlisten verbaut worden sein. werden durch RAM-Generatoren erzeugt, und der Systemarchitektur des originalen Die zweite Möglichkeit besteht darin, den die die Halbleiterhersteller als ServiceICs von großem Vorteil, denn die Schaltkreis auf eine modernere Leistung mit anbieten. Dabei haben sich gesamte Systementwicklungszeit wird Technologie umzusetzen. Grundvodie Techniken sowohl bei der Erstellung eingespart. raussetzung dafür ist das Vorhandensein dieser RAMs als auch deren Ansteuerung der Design-Datenbasis. die vor vielen über die Jahre etwas verändert. Es Jahren auf Bändern oder Festmüssen kreative und innovative Ansätze www.elektroniknet.de durch die 44 Elektronik 5/2006 platten gesichert wurde. Allerdings ist es vielen Produzenten elektronischer Baugruppen und Geräte nicht verständlich, warum sie sechs bis zehn Jahre, nachdem sie bereits die Entwicklung der ASICs bezahlt haben, schon wieder eine Entwicklung bezahlen sollen. Die Kosten für eine Technologie-Umsetzung bestehen aus regulären NREKosten. Das sind Entwicklungsleistungen zuzüglich der Kosten für Masken, Engineering Run und Prototypen gehäuse. Bei analogen ICs sollte man wie bei jedem Design - mit einem Redesign rechnen. Aus Kostengründen empfiehlt es sich, für den ersten Durchlauf entweder Multiprojekt-Wafer Durchläufe (MPW) oder Multi-Level Mask (MLM) zu nutzen. Wenn das IC gemäß Spezifikation funktioniert, wird auf die Single-Mask-Herstellung und damit die Serienfertigung gewechselt. Ein Beispiel aus der Praxis In einer Industriesteuerung des Kunden befinden sich ASICs, die mittelfristig nicht mehr hergestellt werden. Eines dieser ASICs enthält einen 8-bitMikrocontroller und die ihn umgebende Logik sowie RAM-Speicher (Bild). Der Controller wurde als IP-Block ohne bekannte Schaltungsdetails imple- mentiert und nicht dokumentiert. Allerdings fanden sich in den archivierten Verzeichnissen noch Stimuli- und Ergebnisvektoren, die ausschließlich für den Prozessor ohne Umgebung aufgezeichnet wurden. Genutzt haben die Entwickler ferner eine frei verfügbare VHDL-Beschreibung des Prozessors, die bei der Simulation anfänglich noch mehr als 15 000 Unterschiede beim Vergleich der Vektoren ergab. Nach entsprechenden Anpassungen konnten die Designer allerdings bei den Ergebnisvektoren weitestgehende Gleichheit zwischen altem und neuem Prozessordesign herstellen. Anschließend wurde der geänderte VHDL-Code des Prozessors synthetisiert und mit der übrigen Schaltung zum kompletten ASIC zusammengeführt. Die umgebende Logik haben die Ingenieure auf Netzlisten- und Zellenniveau analysiert und dann über TCL-Scripting in die neue Zieltechnologie umgesetzt. Die ursprüngliche Bibliothek lag allerdings nur noch im Papierformat vor, was einen zusätzlichen Aufwand bedeutete. Alle Speicherblöcke mussten die Chipdesigner aus kleineren Blöcken mit Multiplexem und EnableLogik zusammenfügen, zumal die RAMGeneratoren die geforderte Größe nicht erzeugen konnten. Die Pads haben sie wie die Netzliste der Logik - aus der Ursprungsbibliothek von Hand passend umgesetzt. Abschließend kann gesagt werden, dass jedes ältere ASIC, das durch den Hersteller abgekündigt wird, bei Vorhandensein der originalen Daten wieder zu neuem Leben erweckt werden kann. Productivity Engineering (www. peicdesign.de) hat 2005 mehrere vollkommen unterschiedliche ASICs erfolgreich umgesetzt. Unter anderem wurden für einen Kunden mehrere ASICs in kurzer Folge durch ein neues Design wieder verfügbar gemacht, so dass die Industriesteuerung noch viele Jahre länger in neuen Anlagen ihren Dienst verrichten wird. Stefan Schubert/go