- Kirchhoff-Institut für Physik

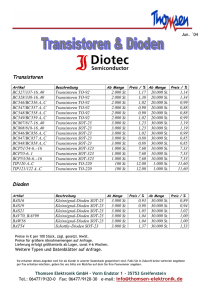

Werbung