Big

Werbung

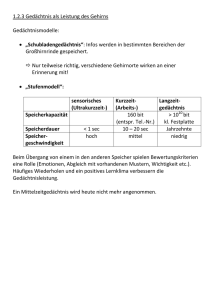

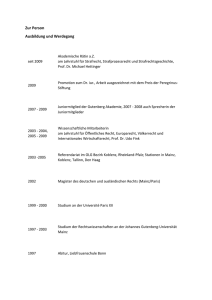

Grundlagen der Rechnerarchitektur und -organisation: The Big Picture Part 2 Lehrstuhl für Informatik 3 28.05.15 Übung zu Grundlagen der Rechnerarchitektur und -organisation Burkhard Ringlein SS 2015 int diff2 = ( wert[i] − 42 ) ∗ ( wert[i] − 42 ) ; Speicher ??? 1. Wozu die Hierarchie unter den Speichern? 2. Warum verstecken moderne CPUs Daten? 3. Wieso funktionierts? Lehrstuhl für Informatik 3 28.05.15 Übung zu Grundlagen der Rechnerarchitektur und -organisation Burkhard Ringlein The Big Picture 1. Wozu die Hierarchie unter den Speichern? Ideal: Großer, schneller Speicher Lehrstuhl für Informatik 3 28.05.15 Übung zu Grundlagen der Rechnerarchitektur und -organisation Burkhard Ringlein The Big Picture 1. Wozu die Hierarchie unter den Speichern? Ideal: Großer, schneller Speicher Jedoch in Realität: Kapazität Fläche/Bit Zugriffszeiten Preis / Bit Lehrstuhl für Informatik 3 28.05.15 Übung zu Grundlagen der Rechnerarchitektur und -organisation Burkhard Ringlein The Big Picture 1. Wozu die Hierarchie unter den Speichern? Ideal: Großer, schneller Speicher → sinnvolle Mischung nötig Jedoch in Realität: Kapazität Fläche/Bit Zugriffszeiten Preis / Bit Lehrstuhl für Informatik 3 28.05.15 Übung zu Grundlagen der Rechnerarchitektur und -organisation Burkhard Ringlein The Big Picture 2. Warum verstecken moderne CPUs Daten? RAM: z.B. 4GB Register: z.B. 8 * 32bit (x86) CPU Lehrstuhl für Informatik 3 28.05.15 Übung zu Grundlagen der Rechnerarchitektur und -organisation Burkhard Ringlein The Big Picture 2. Warum verstecken moderne CPUs Daten? RAM: z.B. 4GB Register: z.B. 8 * 32bit (x86) CPU Kapazität Preis / Bit Zugriffszeiten Lehrstuhl für Informatik 3 28.05.15 Übung zu Grundlagen der Rechnerarchitektur und -organisation Burkhard Ringlein The Big Picture 2. Warum verstecken moderne CPUs Daten? RAM: z.B. 4GB Register: z.B. 8 * 32bit (x86) CPU 1 Takt, 256 Bit (z.B.) 25 – 40 Takte Kapazität Preis / Bit Zugriffszeiten Lehrstuhl für Informatik 3 28.05.15 Übung zu Grundlagen der Rechnerarchitektur und -organisation Burkhard Ringlein The Big Picture 2. Warum verstecken moderne CPUs Daten? Französisch: cache f. Deutsch: das Versteck, der Schlupfwinkel Pl.: die Verstecke, die Schlupfwinkel (leo.org) RAM: z.B. 4GB Register: z.B. 8 * 32bit (x86) CPU Cache 1 Takt, 256 Bit (z.B.) 25 – 40 Takte Kapazität Preis / Bit Zugriffszeiten Lehrstuhl für Informatik 3 28.05.15 Übung zu Grundlagen der Rechnerarchitektur und -organisation Burkhard Ringlein The Big Picture 2. Warum verstecken moderne CPUs Daten? Französisch: cache f. Deutsch: das Versteck, der Schlupfwinkel Pl.: die Verstecke, die Schlupfwinkel (leo.org) RAM: z.B. 4GB Register: z.B. 8 * 32bit (x86) CPU Cache 1 Takt, 256 Bit (z.B.) 1 - 3 Takt(e), 1 – 128 KB 25 – 40 Takte Kapazität Preis / Bit Zugriffszeiten Lehrstuhl für Informatik 3 28.05.15 Übung zu Grundlagen der Rechnerarchitektur und -organisation Burkhard Ringlein The Big Picture 2. Warum verstecken moderne CPUs Daten? Französisch: cache f. Deutsch: das Versteck, der Schlupfwinkel Pl.: die Verstecke, die Schlupfwinkel (leo.org) RAM: z.B. 4GB Register: z.B. 8 * 32bit (x86) Addressbereich Programm lena.c .text: for-Schleife CPU Cache 1 Takt, 256 Bit (z.B.) .data: image 1 - 3 Takt(e), 1 – 128 KB 25 – 40 Takte Kapazität Preis / Bit Zugriffszeiten Lehrstuhl für Informatik 3 28.05.15 Übung zu Grundlagen der Rechnerarchitektur und -organisation Burkhard Ringlein The Big Picture 2. Warum verstecken moderne CPUs Daten? Französisch: cache f. Deutsch: das Versteck, der Schlupfwinkel Pl.: die Verstecke, die Schlupfwinkel (leo.org) RAM: z.B. 4GB Register: z.B. 8 * 32bit (x86) hardwarebestimmte Zuordnungsfunktion Addressbereich Programm lena.c .text: for-Schleife CPU Cache 1 Takt, 256 Bit (z.B.) .data: image 1 - 3 Takt(e), 1 – 128 KB 25 – 40 Takte Kapazität Preis / Bit Zugriffszeiten Lehrstuhl für Informatik 3 28.05.15 Übung zu Grundlagen der Rechnerarchitektur und -organisation Burkhard Ringlein The Big Picture 2. Warum verstecken moderne CPUs Daten? Französisch: cache f. Deutsch: das Versteck, der Schlupfwinkel Pl.: die Verstecke, die Schlupfwinkel (leo.org) RAM: z.B. 4GB Register: z.B. 8 * 32bit (x86) hardwarebestimmte Zuordnungsfunktion Addressbereich Programm lena.c .text: for-Schleife CPU Cache 1 Takt, 256 Bit (z.B.) .data: image 1 - 3 Takt(e), 1 – 128 KB 25 – 40 Takte Kapazität Preis / Bit Zugriffszeiten Lehrstuhl für Informatik 3 28.05.15 Übung zu Grundlagen der Rechnerarchitektur und -organisation Burkhard Ringlein The Big Picture 2. Warum verstecken moderne CPUs Daten? Französisch: cache f. Deutsch: das Versteck, der Schlupfwinkel Pl.: die Verstecke, die Schlupfwinkel (leo.org) RAM: z.B. 4GB Register: z.B. 8 * 32bit (x86) hardwarebestimmte Zuordnungsfunktion Addressbereich Programm lena.c .text: for-Schleife CPU Cache 1 Takt, 256 Bit (z.B.) 1 - 3 Takt(e), 1 – 128 KB Inklusionsbedingung Kapazität Preis / Bit Zugriffszeiten Lehrstuhl für Informatik 3 28.05.15 .data: image Übung zu Grundlagen der Rechnerarchitektur und -organisation Burkhard Ringlein The Big Picture 25 – 40 Takte 2. Warum verstecken moderne CPUs Daten? heutige CPUs: Festplatte 1 - 3 Takt(e), 1 – 128 KB Lehrstuhl für Informatik 3 28.05.15 3 - 6 Takt(e), 256KB - 4MB Übung zu Grundlagen der Rechnerarchitektur und -organisation Burkhard Ringlein The Big Picture 25 - 40 Takt(e), 5 – 15ms, TB ? GB ? 3. Wieso funktionierts? Eigenschaften von Programmen: zeitliche Lokalität: räumliche Lokalität: Lehrstuhl für Informatik 3 28.05.15 Nach Zugriff auf eine Adresse erfolg in naher Zukunft erneut ein Zugriff auf diesselbe Adresse. Nach Zugriff auf eine Adresse erfolg in naher Zukunft ein Zugriff auf eine benachbarte Adresse. Übung zu Grundlagen der Rechnerarchitektur und -organisation Burkhard Ringlein The Big Picture to be continued.... Lehrstuhl für Informatik 3 28.05.15 Übung zu Grundlagen der Rechnerarchitektur und -organisation Burkhard Ringlein The Big Picture