Kapazizätsmessverfahren - European Patent Office

Werbung

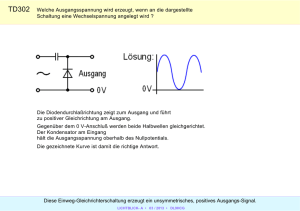

Europäisches Patentamt (19) European Patent Office Office europeen brevets »peen des brevets EUROPÄISCHE (12) EP 0 745 861 A2 PATENTANMELDUNG (43) Veröffentlichungstag: 04.12.1996 Patentblatt 1996/49 (51) intci.6: G01R 27/26, G01R 1 7 / 0 2 (21) Anmeldenummer: 96890093.6 (22) Anmeldetag: 31.05.1996 (84) Benannte Vertragsstaaten: AT CH DE FR GB IT LI SE (72) Erfinder: Klementschitz, Peter A-8430 Leibnitz (AT) (30) Prioritat: 01.06.1995 AT 931/95 (74) Vertreter: Gibler, Ferdinand, Dipl.lng. Dr. techn. Dorotheergasse 7/1 4 1010 Wien (AT) (71) Anmelder: AVL Gesellschaft fur Verbrennungskraftmaschinen und Messtechnik mbH.Prof.Dr.Dr.h.c. Hans List A-8020 Graz (AT) (54) < Kapazizätsmessverfahren Verfahren zum Messen kleiner Kapazitäten mit (57) einer selbstabgleichenden Brückenschaltung (A), wobei die Kapazität oder die Kapazitätsänderung eines unbekannten Kondensators (C1) in einem Brückenzweig bzw. die Kapazitäten oder die Kapazitätsänderung zweier unbekannter Kondensatoren (C1, C2) in zwei verschiedenen Brückenzweigen bestimmt wird, wobei fortlaufend nur während des ersten Pegels (T(1)) des Rechtecksignals die Spannungsdifferenz an zwei zweiten Diagonalpunkten (X, Y) der Brücke in einem Synchronverstärker (D), vorzugsweise einem Komparator, leerlaufverstärkt wird, und während des zweiten Pegels (T(0)) der Synchronverstärker (D) ein vorbestimmtes Potential abgibt, sodann das leerlaufverstärkte Ausgangssignals des Synchronverstärkers mittels eines Reglers, vorzugsweise eines Integralreglers (E), auf einen Sollwert geregelt wird, welcher Sollwert durch den Zeitmittelwert der Ausgangsspannung des Synchronverstärkers bei abgeglichener Brücke festgelegt ist, daß mittels der Ausgangspannung des Reglers (E) über einen Gegenkopplungszweig (G) und eine abgleichbare Klemmschaltung (C) die Brücke (A) an den zweiten Diagonalpunkten (X, Y) in Abgleich gebracht wird, wobei die Ausgangsspannung (UA) des Reglers (E) im wesentlichen proportional der Kapazität oder der Kapazitätsänderung des unbekannten Kondensators (C1) bzw. der unbekannten Kondensatoren (C1, C2) ist. CO 00 io ^> o Q_ LU Printed byJouve, 75001 PARIS(FR) FIG. Za EP 0 745 861 A2 Beschreibung 5 10 15 20 25 30 35 40 45 so 55 Die Erfindung betrifft ein Verfahren zum Messen kleiner Kapazitäten mit einer selbstabgleichenden Brückenschaltung, wobei die Kapazität oder die Kapazitätsänderung eines unbekannten Kondensators in einem Brückenzweig bzw. die Kapazitäten oder die Kapazitätsänderung zweier unbekannter Kondensatoren in zwei verschiedenen Brückenzweigen bestimmt wird und die aus Referenzkondensatoren und einem unbekannten Kondensator oder unbekannten Kondensatoren gebildete Brücke an zwei ersten Diagonalpunkten mit einer periodischen, im wesentlichen rechteckförmigen Spannung mit konstanter Amplitude gespeist wird, wobei die Rechteckspannung in einer Periode jeweils von einem ersten auf einen zweiten Pegel wechselt. Bekannte Verfahren dieser Art werden vor allem in der Sensorik bei der Messung sehr kleiner Kapazitäten bzw. Kapazitätsänderungen angewendet und haben den Nachteil einer sehr geringen erreichbaren Meßfrequenz, sodaß sehr lange Meßzeiten in Kauf genommen werden müssen. Aus der WO-91/09812 ist eine Schaltungsanordnung zur Bestimmung von Kapazitätsänderungen bekanntgeworden, bei der ein Rechteckoszillator eine Brückenschaltung speist, deren Zweige mit einem veränderbaren bzw. festen Kondensator und mit je einem Zweig aus einer Kapazitätsdiode gebildet sind. Die an den Diagonalpunkten der Brücke anliegende Brückenspannung wird über Koppelkondensatoren an die Eingänge eines Differenzverstärkers gelegt, welcher die Differenzspannung verstärkt und dessen Ausgangspannung über einen Tiefpaß und einen Gegenkopplungszweig an einen der Diagonalpunkte zum Abgleich der Brückenschaltung rückgeführt wird. Der andere Diagonalpunkt wird über eine Abgleich-Schaltung auf einem vorbestimmbaren Potential gehalten. Der Nachteil dieser bekannten Schaltungsanordnung besteht in der Verwendung von Kapazitätsdioden zum Einstellen des Brückengleichgewichts, wodurch Koppelkondensatoren zur Gleichspannungsabtrennung für den Eingang des Differenzverstärkers notwendig sind. Weiters kann der zu messende Kondensator in dieser bekannten Schaltung nicht mit Masse verbunden sein, sodaß sich daraus eine Beschränkung für viele Anwendungen, z.B. der Sensorik, ergibt. In der EP-B-0 285 070 ist ein Verfahren zum Messen der Kapazität eines einstellbaren Kondensators und wenigstens eines festen Bezugskondensators in einer Brückenschaltung geoffenbart, in dem der Bezugskondensator und die Meßkapazität an einem gemeinsamen Knoten miteinander verbunden sind und eine feste Spannung direkt über die Anschlüsse eines der Kondensatoren und eine einstellbare Spannung direkt über die Anschlüsse des anderen Kondensators zum Laden während einer ersten Phase eines sich wiederholenden Zweiphasenmeßzyklus angelegt sind, und die Kondensatoren in einer Regelschleife während der zweiten Phase verbunden werden, wobei die Änderung des Potentials an dem genannten Knoten erkannt wird und das Laden der Kondensatoren automatisch modifiziert wird, sodaß die Änderung des Potentials über mehrere Meßzyklen auf Null verringert wird, und wobei die Ladungsänderungen integriert und danach die einstellbare Spannung bestimmt wird und diese Spannung proportional der Kapazität des einstellbaren Kondensators ist. Nachteilig an diesem Verfahren ist die Verwendung zweier Spannungsquellen zum Laden des Meß- und Referenzkondensators, wodurch die Abhängigkeiten dieser Spannungen von den Umgebungsparametern, z.B. Temperatur, in das Meßergebnis eingehen. Aufgabe der Erfindung ist es daher, ein Verfahren der eingangs genannten Art anzugeben, mit dem kleine Kapazitäten mit sehr hoher Meßfrequenz und damit sehr schnell gemessen werden können. Ein weiteres Ziel der Erfindung ist es, eine sehr hochauflösende Messung der unbekannten Kondensatoren zu ermöglichen. Schließlich besteht eine weitere Aufgabe der Erfindung darin, eine sehr gute Temperaturstabilität der Messung zu erreichen. Dies wird erfindungsgemäß dadurch erreicht, daß fortlaufend nur während des zweiten Pegels des Rechtecksignals die Spannungsdifferenz an zwei zweiten Diagonalpunkten der Brücke in einem Synchronverstärker, vorzugsweise einem Komparator, leerlaufverstärkt wird, und während des ersten Pegels der Synchronverstärker ein vorbestimmtes Potential abgibt, sodann das leerlaufverstärkte Ausgangssignal des Synchronverstärkers mittels eines Reglers, vorzugsweise eines Integralreglers, auf einen Sollwert geregelt wird, welcher Sollwert durch den Zeitmittelwert der Ausgangsspannung des Synchronverstärkers bei abgeglichener Brücke festgelegt ist, daß mittels der AusgangSpannung des Reglers über einen Gegenkopplungszweig und eine abgleichbare Klemmschaltung die Brücke an den zweiten Diagonalpunkten in Abgleich gebracht wird, wobei die Ausgangsspannung des Reglers im wesentlichen proportional der Kapazität oder der Kapazitätsänderung des unbekannten Kondensators bzw. der unbekannten Kondensatoren ist. Durch diese Maßnahmen kann eine sehr hohe Meßfrequenz erreicht werden, da beispielsweise bei Integralregelung sehr schnelle Regelzeiten möglich sind. Es wird dabei während des zweiten Pegels des Rechtecksignals durch den Potentialvergleich an den zweiten Diagonalpunkten die Brückenverstimmung ermittelt, und die Stellgröße der Regelung, die die Abweichung der verstärkten Differenzspannung vom Mittelwert der Ausgangsspannung des Synchronverstärkers darstellt, als ein der Verstimmung proportionaler Meßwert erfaßt. 2 EP 0 745 861 A2 5 10 15 20 25 30 35 40 45 so 55 In weiterer Ausbildung der Erfindung kann vorgesehen sein, daß die integrierte Spannung mit einem Tiefpaß-Filter geglättet wird, wobei die geglättete Ausgangsspannung proportional der Kapazität oder der Kapazitätsänderung des unbekannten Kondensators bzw. der unbekannten Kondensatoren ist. Dadurch kann die Zeitkonstante des Integriervorganges klein gehalten und die Welligkeit des Ausgangssignals durch die Tiefpaß-Filterung verringert werden. Weiters kann vorgesehen sein, daß zur quasistatischen Kapazitätsmessung die geglättete Ausgangsspannung in einem weiteren Integralregler in bezug auf einen weiteren Sollwert integriert und diese integrierte Spannung einem dem Abgleich dienenden Eingang der Klemmschaltung zugeführt wird, wobei die geglättete Ausgangsspannung proportional der Kapazität oder der Kapazitätsänderung des unbekannten Kondensators bzw. der unbekannten Kondensatoren ist. Durch diese Maßnahmen können sehr langsame Kapazitätsänderungen gemessen werden, die insgesamt größer als die dem Meßsignal entsprechende Kapazität sind. Ein weiteres Ziel der Erfindung ist es, eine Schaltungsanordnung zur Durchführung des erfindungsgemäßen Verfahrens anzugeben. Dies wird bei einer aus Referenzkondensatoren und einer oder zwei unbekannten Kapazitäten gebildeten Brükkenschaltung, welche an den zwei ersten Diagonalpunkten mit einem Rechteckgenerator verbunden ist, der eine konstante im wesentlichen rechteckförmige Rechteckausgangsspannung liefert, erfindungsgemäß dadurch erreicht, daß die zwei zweiten Diagonalpunkte mit den Eingängen eines Synchronverstärkers verbunden sind, welcher die Differenz der an den beiden zweiten Diagonalpunkten gemessenen Potentiale nur während des zweiten Pegels des Rechteckgenerators verstärkt, daß der Ausgang des Synchronverstärkers mit einem ersten Eingang eines Reglers, vorzugsweise eines Integralreglers, verbunden und während des ersten Pegels der Rechteckspannung auf einem vorbestimmbaren Potential gehalten ist, und der Ausgang des Reglers mit dem Eingang einer Gegenkopplungsschaltung verbunden ist, daß deren Ausgang mit einem ersten Eingang einer Klemmschaltung verbunden ist, daß ein zweiter Eingang des Reglers mit einer konstanten Sollspannungsquelle verbunden ist und ein erster bzw. zweiter Ausgang der Klemmschaltung mit den beiden zweiten Diagonalpunkten verbunden sind, wobei ein zweiter Eingang der Klemmschaltung mit einer Abgleichsspannungsquelle verbunden ist und daß am Ausgang des Reglers eine dem Wert des unbekannten Kondensators bzw. der unbekannten Kondensatoren oder deren Änderungen proportionale Ausgangsspannung abgreifbar ist. Durch diese Maßnahmen ist die Ausgangsspannung der erfindungsgemäßen Schaltungsanordnung direkt proportional zur Brückenverstimmung, ratiometrisch zur Versorgungsspannung und unabhängig von der Frequenz der Brückenspeisung. Der Schaltungsaufwand ist relativ gering, da übliche Standardbauteile verwendet werden können. Deshalb ist die Schaltung auch für integrierte Anwendungen sehr vorteilhaft. In diesem Zusammenhang kann weiters vorgesehen sein, daß dem Ausgang des Integralreglers ein Tiefpaß-Filter nachgeschaltet ist. Dadurch kann die Welligkeit des Ausgangssignals des Integralreglers, besonders wenn dieser eine sehr kleine Zeitkonstante hat, vermindert werden. Besonders vorteilhaft in Hinblick auf die Erhöhung der Grenzfrequenz der Messung ist es dabei, wenn das TiefpaßFilter ein aktives Tiefpaß-Filter ist. Besonders gute Meßergebnisse werden erzielt, wenn das aktive Tiefpaß-Filter ein zweipoliges Filter ist und an dessen Ausgang ein RC-Tiefpaß nachgeschaltet ist. Bei einer besonders bevorzugten Ausführungsform der Erfindung kann vorgesehen sein, daß das aktive TiefpaßFilter durch einen Operationsverstärker mit einer zwischen Ausgang und invertierendem Eingang gekoppelten Parallelschaltung aus einem Kondensator und einem Widerstand gebildet ist, und daß der nichtinvertierende Eingang mit einer konstanten Referenzspannung verbunden ist. In weiterer Ausgestaltung der Erfindung kann vorgesehen sein, daß das aktive Tiefpaß-Filter mehrpolig ist. Dadurch ist es möglich die Welligkeit der Ausgangsspannung noch weiter zu reduzieren. Weiters kann vorgesehen sein, daß der Synchronverstärker aus einem Differenzverstärker gebildet ist, wobei der Ausgang des Differenzverstärkers zur Synchronisation mit einem Widerstand und einem vom Rechtecksignal gesteuerten Schalter in Serie verbunden ist. Dadurch läßt sich ein sehr einfacher und kostengünstiger Aufbau eines erfindungsgemäßen Synchronverstärkers erreichen. Gemäß einer weiteren Variante der Erfindung kann der Synchronverstärker durch eine Abtast- und Halteschaltung gebildet sein. Dadurch vereinfacht sich die synchrone Verstärkung des von der Brücke kommenden Differenzsignals. Gemäß einer besonders bevorzugten Ausführungsart kann vorgesehen sein, daß der Synchronverstärker durch einen Pulsbreitenmodulator gebildet ist und die Pulsmodulation durch die Abhängigkeit der Antwortzeit des Ausgangs eines Differenzverstärkers von der Größe der Spannung am Eingang des Differenzverstärkers erfolgt. Durch diese Maßnahmen wird eine hohe Verstärkung bei gleichzeitig sehr hoher Meßfrequenz ermöglicht. Weiters 3 EP 0 745 861 A2 5 10 15 20 25 30 35 40 45 so 55 ergibt sich eine besonders niedrige Temperaturabhängigkeit dieser Anordnung. Besonders bevorzugt ist eine Variante der Erfindung, die darin besteht, daß der Pulsbreitenmodulator einen Komparator umfaßt, dessen Eingänge mit den beiden zweiten Diagonalpunkten verbunden sind, wobei die Antwortzeit des Ausgangssignals des Komparators eine Funktion des an seinem Eingang angelegten Spannungswertes ist. Dadurch ergibt sich eine Pulsbreitenmodulation, die über die entsprechende Antwort-Kennlinie des Komparators mit der Verstimmung der Brücke in funktionalem Zusammenhang steht. In diesem Zusammenhang kann vorgesehen sein, daß der Ausgang des Komparators zur Synchronisation über einen Pull-up-Widerstand mit dem Ausgang des Rechteckgenerators verbunden ist. Dadurch wird eine synchronisierte Pulsbreitenmodulation erreicht. Weiters kann zur Synchronisierung des Komparators der Komparator einen Latch- oder Inhibit- Eingang aufweisen. Zur Umwandlung des Spannungsausgangs eines Komparators in einen Open-Collector-Ausgang ist es besonders vorteilhaft, wenn der Ausgang des Komparators mit einer Basis eines Schalttransistors mit kurzer Schaltzeit verbunden ist, dessen Kollektor einen Open-Collector bildet. In einer weiteren bevorzugen Ausführungsform der Erfndung kann vorgesehen sein, daß der Integralregler aus einem Differenzverstärker gebildet ist, bei dem ein Integrierkondensator zwischen Ausgang und invertierendem Eingang vorgesehen ist, welcher invertierender Eingang über einen Widerstand den Eingang des Integralreglers bildet und bei dem der nichtinvertierende Eingang mit einer Sollspannungsquelle verbunden ist, wobei die Zeitkonstante des Integralreglers durch das Produkt von Widerstand und Integrierkondensator bestimmt ist. Diese Bauteilkombination läßt einen sehr einfachen Aufbau der erfindungsgemäßen Schaltungsanordnung zu. Gemäß einer erfindungsgemäßen Variante kann die Zeitkonstante des Integralreglers größer oder gleich der Periode der Ausgangsspannung des Rechteckgenerators sein. Dadurch kann der Brückenabgleich während jeder Periode auf einfache Weise erreicht werden. Bei einer besonders bevorzugten Ausführungsform der Erfindung ist vorgesehen, daß das Verhältnis der Zeitkonstante des Integralreglers zur Periodendauer des Rechtecksignals in einem Bereich zwischen 1 und 10 liegt. Dadurch können besonders schnelle Kapazitätsmessungen mit hohen Meßfrequenzen durchgeführt werden. Besonders bevorzugt ist dabei, wenn die Sollspannungsquelle eine konstante Spannung aufweist, deren Wert ein 1/4 des Hochpegels des Rechteckgenerators beträgt, für den Fall, daß der Ausgang des Synchronverstärkers in der Tiefpegelphase auf Masse liegt. In weiterer Ausbildung der Erfindung kann vorgehen sein, daß die Gegenkopplungsschaltung aus einem ersten mit einem der zweiten Diagonalpunkte verbundenen Gegenkopplungswiderstand und einem mit diesem verbundenen zweiten Gegenkopplungswiderstand, der an seinem anderen Ende mit Masse verbunden ist, gebildet ist. Dadurch kann auf einfache Weise die Gesamtverstärkung des Synchronverstärkers und des Integralreglers festgelegt werden. Eine weitere Variante der Erfindung kann darin bestehen, daß die Klemmschaltung über einen ersten Klemmwiderstand einen der zweiten Diagonalpunkte mit dem Verbindungspunkt zwischen den Gegenkopplungswiderständen verbindet und über einen zweiten Klemmwiderstand den anderen der zweiten Diagonalpunkte mit dem Abgriffspunkt eines aus Widerständen gebildeten Spannungsteiler verbindet, wobei eine am zweiten Eingang der Klemmschaltung anliegende Abgleichspannung durch den Spannungsteiler geteilt wird. Dadurch kann auf einfache Weise eine Gegenkopplung der Ausgangsspannung des Integralreglers für die zweiten Diagonalpunkte der Brücke erreicht werden, wobei die Klemmwiderstände auf die gewünschte Grenzfrequenz und die dabei vorliegende Phasendrehung abgestimmt werden müssen, um eine Rückkopplung zu vermeiden. Vorzugsweise ist dabei zum ersten bzw. zweiten Klemmwiderstand eine erste bzw. zweite Klemmdiode parallel geschaltet. Durch diese Maßnahme können die Klemmwiderstände sehr hochohmig ausgeführt werden, wodurch die Kondensatoren der Brückenschaltung in geringerem Ausmaß entladen werden. Dabei ist es besonders vorteilhaft, wenn die erste und die zweite Klemmdiode als Doppeldiode in einem Gehäuse angeordnet sind. Dadurch kann bei Temperaturschwankungen die Nullpunktsdrift der erfindungsgemäßen Schaltungsanordnung minimiert werden. Schließlich besteht eine weitere Ausführungsform der Erfindung darin, daß ein weiterer Integralregler zwischen dem Ausgang des Tiefpaß-Filters und dem zweiten Eingang der Klemmschaltung geschaltet ist. Dadurch kann eine quasistatische Messung der Kapazitäten durchgeführt werden, sodaß auch sehr langsame Änderungen nicht die Auflösung der Messung verschlechtern. Weiters hat diese Maßnahme den Vorteil, daß der Eingang der erfindungsgemäßen Schaltungsanordnung nicht leicht übersteuert werden kann. In weiterer Ausbildung der Erfindung kann vorgesehen sein, daß an den Verbindungspunkt zwischen Begrenzungswiderstand und Brücke eine Kompensationsschaltung über einen Widerstand angeschlossen ist. Dadurch wird auf einfache Weise ein Kompensieren verschiedener äußerer Einflüsse wie Temperatur o.ä. oder der Nichtlinearität des Ausgangssignals in bezug auf eine andere physikalische Größe ermöglicht. 4 EP 0 745 861 A2 5 10 15 20 25 30 35 40 45 so 55 In diesem Zusammenhang kann vorgesehen sein, daß zur Kompensation des Temperaturganges einer der Kompensationseingänge über einen temperaturabhängigen Widerstand mit einer temperaturstabilen Referenzspannung verbunden sind. Dadurch kann die Messung auf einfache Weise von Temperaturänderungen der Umgebung unabhängig gemacht werden. Ein weiteres Merkmal der Erfindung kann sein, daß zur Kompensation des Temperaturganges die beiden Kompensationseingänge mit einem aktiven Temperatursensor verbunden sind. Auf diese Weise kann eine die Messung nur sehr wenig beeinflussende Kompensation des Temperaturganges erzielt werden. Weiters kann vorgesehen sein, daß zur Kompensation der Nichtlinearität der der Kapazität bzw. der Kapazitätsänderung proportionalen Ausgangsspannung der Kompensationseingang über einen Linearisierungs-Widerstand mit dem Ausgang des Integralreglers bzw. dem Ausgang des Tiefpaß-Filters verbunden ist, und das Verhältnis von Widerstand zu Linearisierungs-Widerstand gleich vs-1 beträgt, wobei v die Verstärkung, s= C3/(Cp + C3) ist und Cp eine konstante zu C1 parallele Kapazität darstellt. Dadurch gelingt es z.B. eine zu einem Abstand indirekt proportionale Kapazitätsänderung zu linearisieren. Die Erfindung wird im folgenden anhand der in den Zeichnungen dargestellten Ausführungsformen näher erläutert. Dabei zeigt Fig. 1a ein Schaltbild einer erfindungsgemäßen Brückenschaltung; Fig. 1b eine Darstellung der an der Brücke anliegenden bzw. abgreifbaren Pegel in Abhängigkeit von der Zeit; Fig. 2a und Fig. 2b ein Blockschaltbild einer erfindungsgemäßen Schaltungsanordnung zur Durchführung des erfindungsgemäßen Verfahrens; Fig. 3 Ausgangsspannungen verschiedener Ausführungsformen von Synchronverstärkern; Fig. 4a eine Kennlinie der Eingangsübersteuerung eines Komparators in Abhängigkeit von der Antwortzeit seines Ausganges; Fig. 4b ein Schaltbild eines synchronisierten Komparators; Fig. 4c den Verlauf einer erfindungsgemäßen Pulsbreitenmodulation in Abhängigkeit von der Zeit; Fig. 5 ein Blockschaltbild einer erfindungsgemäßen Schaltungsanordnung; Fig. 6 eine äußere Beschaltung der Schaltungsanordnungen gemäß Fig. 9 bis 11 zur Temperaturkompensation; Fig. 7 eine äußere Beschaltung der Schaltungsanordnungen gemäß Fig. 9 bis 11 zur Linearitätskompensation und Fig. 8 und 9 Ausführungsformen von erfindungsgemäßen Schaltungsanordnungen mit Kompensationseingängen. In Fig. 1a ist eine beim erfindungsgemäßen Verfahren verwendete Brückenschaltung A gezeigt, wobei die Kapazität oder die Kapazitätsänderung eines unbekannten Kondensators C1 in einem Brückenzweig bzw. die Kapazitäten oder die Kapazitätsänderung zweier unbekannter Kondensatoren C1 , C2 in zwei verschiedenen Brückenzweigen bestimmt wird. Die aus Referenzkondensatoren C2, C3, C4 bzw. C3, C4 und einem unbekannten Kondensator C1 oder unbekannten Kondensatoren C1, C2 gebildete Brücke A wird an zwei ersten Diagonalpunkten, die mit Clock T und Masse verbunden sind, mit einer periodischen, im wesentlichen rechteckförmigen Spannung T mit konstanter Amplitude gespeist, wobei die Rechteckspannung T in einer Periode jeweils von einem ersten T(0) auf einen zweiten Pegel T(1) wechselt, wie aus dem Spannungs-Zeitdiagramm in Fig. 1b zu erkennen ist. Erfindungsgemäß wird fortlaufend nur während des zweiten Pegels T(1) des Rechtecksignals die Spannungsdifferenz an zwei zweiten Diagonalpunkten X, Y der Brücke A in einem Synchronverstärker D, vorzugsweise einem Komparator, leerlaufverstärkt. Während des ersten Pegels T(0) gibt der Synchronverstärker D ein vorbestimmtes Potential ab. Das leerlaufverstärkte Ausgangssignal des Synchronverstärkers wird mittels eines Reglers, vorzugsweise eines Integralreglers E, auf einen Sollwert geregelt, welcher Sollwert durch den Zeitmittelwert der Ausgangsspannung des Synchronverstärkers bei abgeglichener Brücke festgelegt ist. Mittels der Ausgangspannung des Reglers E wird über einen Gegenkopplungszweig G und eine abgleichbare Klemmschaltung C die Brücke A an den zweiten Diagonalpunkten X, Y in Abgleich gebracht wird, wobei die Ausgangsspannung des Reglers E im wesentlichen proportional der Kapazität oder der Kapazitätsänderung des unbekannten Kondensators Cl bzw. der unbekannten Kondensatoren C1 , C2 ist. Je eine Ausführungsform der Erfindung ist anhand eines Blockschaltbildes in Fig. 2a und Fig. 2b beschrieben, wobei der Regler E als Integralregler ausgeführt ist, die integrierte Spannung mit einem Tiefpaß-Filter F geglättet wird und die geglättete Ausgangsspannung U_out proportional der Kapazität oder der Kapazitätsänderung des unbekannten Kondensators C1 bzw. der unbekannten Kondensatoren C1, C2 ist. Das in Fig. 2b gezeigte Blockschaltbild unterscheidet sich von dem in Fig. 2a durch eine Linearisierungsschaltung die zwischen Brückengenerator B und der Brücke A geschaltet ist. Die konkrete Ausgestaltung einer solchen SchalH, ist in Fig. 8 wiedergegeben. tung In Fig. 5 ist eine weitere Ausführungsform des erfindungsgemäßen Verfahren und der erfindungsgemäßen Schal- 5 EP 0 745 861 A2 5 10 15 20 25 30 35 40 45 te 55 tungsanordnung dargestellt, wobei zur quasistatischen Kapazitätsmessung die geglättete Ausgangsspannung in einem weiteren Integralregler E in bezug auf einen weiteren Sollwert integriert und diese integrierte Spannung einem dem Abgleich dienenden Eingang (Offset) der Klemmschaltung C zugeführt wird, wobei die geglättete Ausgangsspannung proportional der Kapazität oder der Kapazitätsänderung des unbekannten Kondensators C1 bzw. der Kapazitätsdifferenz oder deren Änderung der unbekannten Kondensatoren C1 , C2 ist. Zur Erklärung der Wirkungsweise des erfindungsgemäßen Synchronverstärkers sind in Fig. 3 die Speisespannung T der Brücke A und die Ausgangsspannungen verschiedener Ausführungsformen von Synchronverstärkern dargestellt. Dabei kann es sein, daß der Synchronverstärker D aus einem Differenzverstärker gebildet ist, wobei der Ausgang des Differenzverstärkers zur Synchronisation über einen Widerstand mit dem Rechteckgenerator B verbunden ist (Fig. 4b). Die Ausgangsspanung eines solchen mit seiner Leerlaufverstärkung betriebenenen Differenzverstärkers ist in Fig. 3 i) gezeigt. Weiters kann der Synchronverstärker D durch eine Abtast- und Halteschaltung gebildet sein. Eine bevorzugte Ausführungsform ist es, wenn der Synchronverstärker D durch einen Pulsbreitenmodulator gebildet ist und die Pulsmodulation durch die Abhängigkeit der Antwortzeit des Ausgangs eines Differenzverstärkers von der Größe der Spannung am Eingang des Differenzverstärkers erfolgt. Der zugehörige Spannungsverlauf am Ausgang eines solchen Pulsbreitenmodulators ist in Fig. 3ii) für niedrige und in Fig. 3iii) für hohe Frequenzen angegeben. Durch die Antwortzeit der Leerlaufverstärkung eines Komparators ergibt sich die in Fig. 4a gezeigte Charakteristik, die eine Pusbreitenmodulation des Eingangssignals ermöglicht. Dabei umfaßt der Pulsbreitenmodulator einen Komparator, dessen Eingänge mit den beiden zweiten Diagonalpunkten X, Y verbunden sind, wobei die Antwortzeit des Ausgangssignals des Komparators eine Funktion des an seinem Eingang angelegten Spannungswertes ist. Dabei kann der gewählte Arbeitspzunkt beispielsweise so gewählt werden, daß bei einer Übersteuerung von 2mV die Antwortzeit 150ns beträgt. Die daraus resultierende Pulsbreitenmodulation zeigt Fig. 4c. Die in Fig. 8 dargestellte Schaltungsanordnung zur Durchführung des Verfahrens weist eine aus Referenzkondensatoren C2, C3, C4 bzw. C3, C4 und einer oder zwei unbekannten Kapazitäten C1 bzw. C1, C2 gebildete Brückenschaltung A auf, die an den zwei ersten Diagonalpunkten mit einem Spannungsgenerator B verbunden ist, der eine konstante im wesentlichen rechteckförmige Rechteckausgangsspannung T liefert. Erfindungsgemäß ist dabei vorgesehen, daß die zwei zweiten Diagonalpunkte X, Y mit den Eingängen eines Synchronverstärkers D, hier durch einen Komparator ausgeführt, verbunden sind, welcher die Differenz der an den beiden zweiten Diagonalpunkten X, Y gemessenen Potentiale nur während des zweiten Pegels T(1 ) des Rechteckgenerators B leerlaufverstärkt, daß der Ausgang des Synchronverstärkers D mit einem ersten Eingang eines Reglers, vorzugsweise eines Integralreglers E, verbunden und während des ersten Pegels T(0) der Rechteckspannung auf einem vorbestimmten Potential gehalten ist, und der Ausgang des Reglers E über einen Gegenkopplungszweig R2, R1 mit dem Eingang einer Klemmschaltung C verbunden ist, wobei ein zweiter Eingang des Reglers E mit einer konstanten Sollspannungsquelle UB/4 verbunden ist, und ein erster bzw. zweiter Ausgang der Klemmschaltung C mit den beiden zweiten Diagonalpunkten X, Y verbunden sind, wobei ein zweiter Eingang Offset der Klemmschaltung C mit einer Abgleichsspannungsquelle verbunden ist. Am Ausgang des Integralreglers E ist eine dem Wert des unbekannten Kondensators bzw. der unbekannten Kondensatoren oder deren Änderungen proportionale Ausgangsspannung abgreifbar. Dabei ist in diesem Ausführungsbeispiel weiters vorgesehen, daß dem Ausgang des Integralreglers E ein TiefpaßFilter F nachgeschaltet ist. Das Tiefpaß-Filter F ist in Fig. 8 als aktives zweipoliges Tiefpaß-Filter ausgebildet, an dessen Ausgang ein RC-Tiefpaß R41, C31 nachgeschaltet ist. Das aktive Tiefpaß-Filter F kann aber auch mehrpolig ausgebildet sein. Die im wesentlichen rechteckförmige Speisespannung für die Brücke A kann durch einen handelsüblichen Quarzoszillator in integrierter Form erzeugt werden, der den Vorteil eines geringen Platzbedarfes und eines niedrigen Preises aufweist. Um einen handelsüblichen Komparator zu einem Synchronverstärker umzufunktionieren, kann wie in Fig. 8 gezeigt, der Ausgang des Komparators zur Synchronisation über einen Pull-up-Widerstand R8 mit dem Ausgang des Rechteckgenerators B verbunden sein. Der Integralregler E aus Fig. 8 ist erfindungsgemäß aus einem Differenzverstärker gebildet, bei dem ein Integrierkondensator C5 zwischen Ausgang und invertierendem Eingang vorgesehen ist, welcher invertierender Eingang über einen Widerstand R9 den Eingang des Integralreglers bildet und bei dem der nichtinvertierende Eingang mit einer Sollspannungsquelle verbunden ist, wobei die Zeitkonstante des Integralreglers durch das Produkt von Widerstand R9 und Integrierkondensator C9 bestimmt ist. Vorteilhaft ist es dabei, wenn die Zeitkonstante des Integralreglers E größer oder gleich der Periode der AusgangsSpannung des Rechteckgenerators B ist. Besonders bevorzugt ist dabei ein Bereich, in dem das Verhältnis der Zeitkonstante des Integralreglers zur Periodendauer des Rechtecksignals in einem Bereich zwischen 1 und 10 liegt. Für eine gute Ausnützung des vorhandenen Modulationshubes der Pulsbreitenmodulation weist Sollspannungsquelle eine konstante Spannung auf, deren Wert 6 EP 0 745 861 A2 5 10 15 20 25 30 35 ein Viertel des ersten Pegels des Rechteckgenerators B beträgt. Die Gegenkopplungsschaltung G ist in Fig. 8 aus einem ersten mit einem der zweiten Diagonalpunkte verbundenen Gegenkopplungswiderstand R2 und einem mit diesem verbundenen zweiten Gegenkopplungswiderstand R1 gebildet, der an seinem anderen Ende mit Masse verbunden ist. Die Klemmschaltung C verbindet über einen ersten Klemmwiderstand R5 einen der zweiten Diagonalpunkte mit dem Verbindungspunkt zwischen den Gegenkopplungswiderständen R2, Rl und über einen zweiten Klemmwiderstand R6 den anderen der zweiten Diagonalpunkte mit dem Abgriffspunkt eines aus Widerständen R3, R4 gebildeten Spannungsteiler, wobei eine am zweiten Eingang (Offset) der Klemmschaltung anliegende Abgleichsspannung durch den Spannungsteiler geteilt wird. Zum ersten bzw. zweiten Klemmwiderstand R5 bzw. R6 ist dabei eine erste bzw. zweite Klemmdiode D1 bzw. D2 parallel geschaltet, wobei es für die Temperaturstabilisierung vorteilhaft ist, wenn die erste und die zweite Klemmdiode D1, D2 als Doppeldiode in einem Gehäuse angeordnet sind. In den Ausführungsbeispielen nach Fig. 8 und 9 ist gemäß Fig. 2b die Ausgangsspannung (Clock) des Rechteckgenerators B über je einen Widerstand R10, R11 mit den Referenzkondensatoren C3, C4 verbunden, wobei die Verbindungspunkte der Widerstände R10, R11 mit den Referenzkondensatoren C3, C4 über je eine Diode D5, D4 Kompensationseingänge Comp_x, Comp_y bilden, die wie in Fig. 6 und Fig. 7 beschaltet werden können. Zur Temperaturkompensation wird dabei eine temperaturstabile Referenzspannung U_Temp über einen temperaturabhängigen Widerstand R_Temp oder ein aktiver Temperatursensor mit den beiden Kompensationseingängen verbunden. Zur Linearitätskompensation wird ein Linearisierungswiderstand R_Lin (bzw. R7 in Fig. 9) mit einem der Kompensationseingänge Comp_x verbunden. Für eine solche Schaltung sind die zu Fig. 9 weiter unten angegebenen Gleichungen gültig. Der nicht benötigte Eingang Comp_y soll bei dieser Form der Linearisierung auf eine Spannung, die etwas größer als die Durchlaßspannung einer Diode ist, also etwa 1,5 bis 2V, gelegt werden. Dies hat den Vorteil, daß der Temperaturgang der Dioden ausbalanciert wird. Für eine verbesserte Temperaturstabiität können die Dioden D4, D5 als Schottky-Dioden in einem gemeinsamen Gehäuse ausgeführt sein. 1. Allgemeines Dieses Schaltprinzip wurde entwickelt zum Messen kleinster Kapazitäten bei gleichzeitig hoher Meßfrequenz, hoher Auflösung und großer Temperaturstabilität. Die Ausgangsspannung ist direkt proportional zur Brückenverstimmung, ratiometrisch zur Versorgungsspannung und unabhängig von der Frequenz der Brückenspeisung. Die Brükkenspeisung erfolgt mit einem symmetrischen Rechtecksignal und wird im folgenden kurz als 'Clock' bezeichnet. Der Schaltungsaufwand ist gering, und es werden übliche Standardbauteile verwendet. Die Schaltung ist sehr gut für einen integrierten Aufbau in einem ASIC - Chip geeignet. Typisches Anwendungsgebiet ist die Sensorik. 2. Meßbrücke Fig. 1a: 40 45 so Die Brücke ist als Wheatstone-Brücke aufgebaut und wird mit dem Clock-Signal versorgt. Die Brückenelemente C1 ... C4 sollen für eine optimale Empfindlichkeit in etwa den gleichen Wert haben. Es kann entweder nur C1 oder C1 und C2 (Diflerentialkondensator) gemessen werden. Der typische Kapazitätswert der Brückenelemente liegt unter 10OpF bei größeren Werten muß die Clock-Frequenz entsprechend niedriger gewählt werden oder man muß die Schaltung für einen hohen Stromverbrauch umdimensionieren. Das Clock-Signal hat in der Low-Phase (= T(0) ) eine Spannung von null Volt, in der High-Phase (= T(1) ) die Versorgungsspannung +UB. Da im folgenden die Verstärkung direkt proportional zu Brückenversorgungsspannung ist und dadurch in der High-Phase gleich +UB, ist eine stabilisierte Versorgungsspannung sehr wichtig. An den Punkten X, Y ergeben sich die Spannungsänderungen AX, AY. In Fig. 1bNerden auch die Spannungsdiagramme für das Clocksignal T und für für die Meßpunkte X, Y gezeigt. Die Meßpunkte X,Y können im Prinzip jede beliebige Gleichspannung aufweisen, denn durch die Kondensatoren C1...C4 sind sie gleichspannungsmäßig entkoppelt. Der Gleichspannungsanteil wird hier so gewählt, daß zum Zeitpunkt(1) gilt : X(1) = Y(1). Zwangsläufig ergibt sich dann für den Zeitpunkt (0) : 7 EP 0 745 861 A2 X(0) = X(1 ) - AX, Y(0) = Y(1 ) - AY. 5 10 Dies hat schaltungsmäßig den Vorteil, daß der Spannungsvergleich X(1) = Y(1) bei ungefähr UB/2 erfolgt und somit kein Problem mit dem Meßbereich besteht. Bei einer Wahl von X(0) = Y(0) = 0 Volt im Zeitpunkt (0) wäre dies nicht der Fall. Die Grundidee der darauf basierenden Schaltung besteht darin, den Gleichspannungsanteil in den Punkten X,Y so nachzuregeln, daß zum Zeitpunkt(l) diese Punkte die gleiche Spannung aufweisen. Die Regelspannung ist dabei direkt proportional zur Verstimmung der Brücke und stellt somit die gewünschte Ausgangsgröße dar. 3. Blockschaltbild Fig. 2a: 15 20 25 30 Hier wird die vorhin genannte Grundidee schaltungsmäßig realisiert : Die Brücke wird von einem symmetrischen ( Pulsdauer = Pausendauer ) RechteckOszillator versorgt. An den Punkten X legt eine vom Ausgang U_out gesteuerte Klemmschaltung, am Punkt Y eine von der Offsetspannung gesteuerte Klemmschaltung den Gleichspannungsanteil fest. Die Differenzspannung X - Y wird von einem synchronisierten Verstärker im Zeitpunkt (1) mit der Leerlaufverstärkung verstärkt. Im Zeitpunkt (0) darf der Verstärker nicht aktiv sein, es wird daher der Ausgang des Verstärkers in dieser Phase auf einen konstanten Wert gehalten. Der darauf folgende Integralregler hat eine größere Zeitkonstante als die Periode des Clocksignals. Die Phase des Ausgangssignal wird so gewählt, daß eine Gegenkopplung zum Meßpunkt Xzum Zeitpunkt (1) besteht. Die Referenzgröße für den Integralregler ist eine konstante Spannung. Der Ausgang des Synchron-Verstärkers zum Zeitpunkt (1) beträgt im Schnitt UB/2. Wenn für den Zeitpunkt (0) a) 0 Volt b) letzter Wert ( = UB/2 im statistischen Mittel ) C) UB gewählt wird, dann ergeben sich folgende Referenzspannungen : 35 a) 1/4 UB b) 1/2 UB c) 3/4 UB. 4. Realisierungsmöglichkeiten für den Synchronverstärker 40 Theoretisch kann der Synchronverstärker auf folgende Arten realisiert werden : 45 a) Differenzverstärker : Nur für sehr niedere Clockfrequenzen ( bis ca. 10 kHz ) geeignet. Um bei einer hohen Clockfrequenz von z. B. 1MHz und einer geforderten Verstärkung von mindestens 1000 ein Rechtecksignal noch gut wiedergeben zu können, ist ein Gewinn-Bandbreite-Produkt (=GBP) von > 10 GHz notwendig. Standardmäßige Operationsverstärker haben ein GBP von max. 1 GHz. Die Synchronisation erfolgt durch eine zusätzliche Beschaltung des Ausgangssignals, z.B. ein Transistor schließt das Ausgangssignal nach einem Serienwiderstand kurz. 50 b) Sample-Hold : Hier gilt das Gleiche wie für a). Der Sample-Hold Baustein hat nur den Vorteil einer einfacheren Synchronisierung. 55 c) Pulsbreitenmodulation : Das Ausgangsignal wird als Puls-Pausen-Verhältnis ausgegeben In Fig. 3 wird die Äquivalenz zwischen Differenzverstärker und Pulsbreitenmodulator veranschaulicht. Wie im nächsten Punkt gezeigt wird, kann der Pulsbreitenmodulator auf besonders einfache Weise realisiert werden. In Fig. 3 werden die Spannungsdiagramme für i) Differenzverstärker / Sample-Hold und ii) Pulsbreitenmodulator 8 EP 0 745 861 A2 gezeigt. Bei sehr hohen Clockfrequenzen verändert sich der Rechteckimpuls durch die begrenzte Flankensteilheit zu einem Dreiecksimpuls iii) 5 5. Realisierungsmöglichkeiten synchron. Pulsbreitenmodulator Anforderungen : 10 - hohe Verstärkung ( > 1000 ) hohe Geschwindigkeit ( Periodendauer < 1u.s ) hohe Temperaturstabilität Nicht gefordert : Linearität, da durch die Regelung ein konstanter Arbeitspunkt vorliegt. 15 20 25 Möglichkeiten : Es gibt eine große Anzahl von Präzisions-Komparatoren, die in Analog-Digitalwandlern nach sukzessiver Approximation oder Sigma-Delta-Verfahren angewendet werden. Es gelten dort die gleichen hohen Anforderungen. Durch die hohe Stückzahl sind dies sehr preiswerte und übliche Bauteile. Pulsbreitenmodulation durch Antwortzeit ( response time ) eines Komparators : Fig. 4a: Die Antwortzeit ist abhängig von der Übersteuerung ( overdrive ) der Eingänge. Es tritt sowohl eine positive als auch eine negative Übersteuerung auf. Die dazugehörigen Antwortzeiten können durchaus verschieden sein. Für die Realisierung wird die Betriebsart mit der kürzeren Antwortzeit gewählt, da man damit eine höhere Grenzfrequenz bzw. eine kleinere Übersteuerung und damit verbunden eine bessere Genauigkeit erreicht. Die Betriebsart mit der kürzeren Antwortzeit ergibt den stabileren Arbeitspunkt. Synchronisation des Komparators : 30 Während der Low-Phase des Clock-Signals soll der Komparatorausgang nicht reagieren bzw. konstant sein, z.B. durch Schalten des Ausgangs auf Masse. Komparator mit Open-Collector-Ausgang : 35 40 45 so Der Ausgang wird über einen Pull-up-Widerstand mit dem Clocksignal verbunden. Der Komparator kann dadurch in nur der High-Phase des Clocksignals reagieren, in der Low-Phase ist der Ausgang auf Masse. Für sehr schnelle Anwendungen ist eine zum Pull-up-Widerstand parallel und in Sperrichtung zum Clocksignal geschaltene SchottkyDiode von Vorteil. Komparator mit Spannungs-Ausgang : Der Spannungsausgang kann durch einen nachfolgenden schnellen Schalttransistor in einen Open Collector Ausgang umgewandelt werden. Komparator mit Latch-(oder lnhibit-)Eingang : Der Ausgangszustand des Komparators wird während der Low-Phase des Taktsignals durch einen geeigneten Eingang eingefroren. Meist weisen derartige Komparatoren einen Spannungsausgang auf. Ein nachfolgender schneller Schalttransistor ist möglicherweise trotzdem empfehlenswert, da der Spannungsausgang üblicherweise nur zum Ansteuern von digitalen Eingängen ausgelegt ist und unter Umständen die Sättigungsspannung über den Temperaturbereich beträchtlich schwankt. 6. Realisierung einer Gesamtschaltung ( Beispiel ) 55 Fig. 8: Das Blockschaltbild nach Fig. 2b wird hier zu einer konkreten Schaltung umgesetzt. 9 EP 0 745 861 A2 6.1 Brücke : 5 10 15 20 25 C1, C2 : C3, C4 : Meßkondensatoren Referenzkondensatoren 6.2 Synchronverstärker : Aufgebaut als synchronisierter Pulsbreitenmodulator. Die Modulation erfolgt über die Kennlinie response time zu input overdrive eines schnellen Präzisionskomparators. Es wird hier die positive Übersteuerung als Arbeitspunkt benutzt, da sie die kleinere response time aufweist. Die Auswahl ergibt sich ohne weitere Bauteile von selbst, da sich die Schaltung auf Grund der schnelleren Reaktionszeit auf diesen Punkt hin regelt. Der Komparator hat einen OpenCollector-Ausgang. Die Synchronisierung erfolgt über den Pull-up-Widerstand R8. 6.3 Integralregler : Sollwert : UB/4, da der Ausgang der vorhergehenden Stufe in der Low-Phase des Clock-Signals auf Masse liegt und in der High-Phase UB/2 im Mittel gewählt wurde. Istwert : Das Ausgangssignal der vorhergehenden Stufe ( Komparatorausgang ). Rückkopplung :Der Spannungsteiler R1, R2 sowie die Klemmschaltung D1, R5. Mit R2 wird die Verstärkung eingestellt. Stellglied : Der Synchronverstärker, hier realisiert durch einen Komparator. Zeitkonstante für Integralregler : R9, C5. Sie soll größer als die Periodendauer des Clocksignals sein. 6.4 Integralregler : Operationsverstärker ( OpAmp ). 30 'Störgröße': Der sich ändernde Kapazitätswert in der Brücke. Dies ist die eigentliche Meßgröße. Der Ausgang des Integralreglers stellt bereits das Meßsignal dar. Bei sehr schnellen Anwendungen wird man das Verhältnis Integrationszeitkonstante zu Periodendauer relativ klein ( zwischen 1 und 10 ) wählen, um auch eine hohe Meßfrequenz erzielen zu können. Dies hat dann eine relativ große Welligkeit am Ausgang des Integrators zur Folge. Es wird daher noch ein mehrpoliges aktives Filter nachgeschaltet, mit dem dieser Trägerrest beseitigt wird und das dennoch eine hohe Meßfrequenz erlaubt. Bei sehr langsamen Anwendungen kann die Integrationszeitkonstante sehr groß gewählt werden, die Welligkeit ist entsprechend gering und man kann auf eine folgende Filterstufe auch verzichten. 35 6.5 Gegenkopplung Der Synchronverstärker wird mit der Leerlaufverstärkung betrieben, und der Integralregler hat keinen Proportionalanteil. Die Verstärkung v wird allein von der Gegenkopplung, das ist hier der Spannungsteiler R1 , R2 , bestimmt : 40 V= 45 ^L=1+R_2 R1 UX-UY Wenn nur C1 verändert wird : C1 = C + AC, C2, C3, C4 = C Ux"UY " U B ^ Wenn C1 und C2 verändert wird (Differentialkondensator): 55 C1 = C + AC, C2 = C - AC, C3, C4 = C UX-UY * U B ^ 10 EP 0 745 861 A2 Die Offseteinstellung braucht nicht über Trimmkondensatoren zu erfolgen, sondern wird über eine Spannung am Eingang 'Offset' durchgeführt. Lineare Messung des Plattenabstandes eines Plattenkondensators : Gegeben sei eine Halbbrücke mit dem Meßkondensator C1 und dem Referenzkondensator C3. Der Meßkondensator C1 läßt sich als physikalisches Modell in eine konstante Parallelkapazität Cp und eine sich mit dem Plattenabstand Ad sich ändernden Plattenkondensator CO aufteilen. Ad := d0 := C0 := Cp := s := Abstand von der Ruhelage Abstand in Ruhelage Kapazitätswert des Plattenkondensators bei d0 Parallelkapazität 1 + Ad / d0 Es gibt somit ein Abstandsmaß zur Ruhlage an und ist linear zu Ad. Es gilt C1 = Cp + CO/s. Es erfolgt eine Gegenkopplung vom Ausgang uA zum Steuereingangeingang der Spannnungsamplitude des Brükkenzweig des Meßkondensators. w := Faktor für Größe des Spannungshubs im Brückenzweig ( 0 < w < 1 ). Es ist nun eine zu Ad bzw. zu s lineare Ausgangsgröße gewünscht. Behauptung : Durch geeignete Rückkopplung der Ausgangsspannung y an den Kompensationseingang läßt sich ein zu s vollkommen lineares Ausgangssignal erreichen. Die Linearitätsabstimmung ist dabei unabhängig vom Nullpunkt. Beweis : Die Gleichung (2) wird dadurch folgenderweise verändert : ua=vub(-;-w^|-3) 0) Rückkopplungsfaktor uA nach uc betrage k . (4) k= 1 + R7/R10. Die Verstärkungskorrektur w beträgt dann UA w= 1-ur/uR = 1-— - (5) <6> ^ " b ^ ^ c T ^ Der Kondensator C1 wird nun durch das physikal. Modell Cp + CO / s ersetzt : (7) ua C3 1 "A^B^n-^-^Cp+CO/s^ 11 EP 0 745 861 A2 Diese für uA implizite Gleichung läßt sich in die folgende explizite umformen : s(Cp+(1+n)C3)+C0 uA -ku B v s n (k Cp+(k - v) C3)+k n CO (8)1 K Damit uA linear zu s ist, muß der s-Term im Nenner null werden : (9) 10 => k Cp + (k-v)C3 = 0 Es gilt somit folgende Linearitätsbedingung für k : k = VCp%3 15 20 25 Die Linearitätsbedingung ist somit unabhängig von der Mittenabstimmung m. die Wenn die Linearitätsbedingung mit einer Einstellung k für jedes v gelten soll, dann muß k proportional zu jedem v sein. Dies kann durch eine der folgenden Maßnahmen erreicht werden : a) es gibt nur ein v => v ist konstant, d. h. die Verstärkung wird fest in Form von Fixwiderständen vorgegeben => es gibt nur ein k => k ist konstant. b) v ist variabel : Die Linearität wird bei einem beliebigen v über einen Widerstand abgeglichen. Die Bedingung (10), daß k und v zueinander direkt proportional sind kann in Form eines Tandem-Potentiometers auf einfache Weise und mit hoher Genauigkeit erfüllt werden. Die Gleichung (7) ändert sich unter der Bedingung (10) auf: /n\ 30 35 40 45 so 55 / (n+1)C3+Cp 1, Das Ausgangssignal uA ist somit linear zum Abstandsmaß s. Ende des Beweises. 6.6 Klemmschaltung Aufgebaut durch : Positiver Komparatoreingang : D1, R5, C1, C3. Negativer Komparatoreingang : D2, R6, C2, C4. Die Dioden D1, D2 sind vorzugsweise als eine Doppeldiode in einem Gehäuse ausgeführt. Dies hat den Vorteil, daß bei Temperaturschwankungen die Nullpunktsdrift minimiert wird. Da die Brückenkapazitätswerte sehr gering sind, kann bei gewöhnlichen Dioden der Sperrstrom über die Temperatur bereits zu großen Nullpunkts- und Verstärkungsänderungen führen. Es wird daher die Verwendung von FET-Dioden empfohlen, die einen spezifizierten Sperrstrom von bis zu kleiner als 1pA bei Raumtemperatur aufweisen. Damit läßt sich ein extrem gutes Temperaturverhalten erreichen. Die Dioden D1 , D2 werden jeweils von R5, R6 überbrückt. R5, R6 sind relativ hochohmig ( ca. 100 kQ); die Zeitkonstante R5, C1 + C3 bzw. R6, C2 + C4 ist somit wesentlich größer als die Periodendauer des Clocksignals. Mit den Überbrückungswiderständen weist die Schaltung einen wesentlich verbesserten Frequenzgang auf. D1 , D2 könnten auch zur Gänze entfallen. Die Überbrückungswiderstände müssen dann auf einen kleineren Wert dimensioniert werden. Dies ist notwendig, um eine hohe Grenzfrequenz erreichen zu können und um zu verhindern, daß die Phasendrehung des Integrators und die Phasendrehung des RC-Glieds R5*(C1 +C3) zusammen -1 80° beträgt, da sonst aus der Gegenkopplung eine Mitkopplung wird, und die Schaltung schwingt. Durch den kleineren Wert von R5, R6 wird die Kapazitätsbrücke bereits deutlich entladen; die Rechteckspannung in den Punkten X, Y verändert sich von einem Rechteck zu einem fallenden Trapez. Bei gleichen Werten der Gegenkopplung R1, R2 veringert sich die Verstärkung um den Faktor 2, da nun die Gegenkopplung nicht nur in der High-Phase des Clocksignals aktiv ist, sondern auch in der Low-Phase. Ohne die Dioden D1, D2 ist die Schaltung zwar einfacher, man verliert aber durch die fallende Flanke relativ viel an Temperaturstabilität der Gesamtschaltung. 12 EP 0 745 861 A2 6.7 Rechteckoszillator Fig.12: 5 Anforderungen : 10 Das Puls-Pausen Verhältnis soll ungefähr 1:1 sein und muß präzise konstant bleiben, hohe Flankensteilheit Ausgangspegel von Masse bis +UB. Die Sättigungsspannung soll relativ gering sein und darf sich über die Temperatur auch nicht nennenswert ändern. Nicht gefordert: Konstante Frequenz. 15 20 25 30 35 40 7. Quasistatische Anwendungen Fig. 5 : Die bis jetzt beschriebene Anwendung ist auch echt statisch, das heißt, es kann auch ein konstant gleichbleibender Meßkondensator C1 gemessen werden. Es gibt aber sehr schwierige Anwendungsfälle, wo sich C1 langsam, aber wesentlich größer als das Meßsignal ändert und C2 nicht oder nur ungenügend als Referenzwert verwenden läßt. In solchen Fällen begnügt man sich mit einer sehr niedrigen unteren Grenzfrequenz. Eine quasistatische Variante der Schaltung kann dadurch erreicht werden, indem das Ausgangssignal von ein Integralregler an den Offset-Eingang zurückgeführt wird. Gegenüber einer einfacheren AC-Auskopplung hat dies den Vorteil, daß der Eingang nicht so leicht übersteuert werden kann, da er in der Regelschleife liegt. Damit läßt sich in weiterer Folge eine bessere Auflösung erzielen. Bei der quasistatischen Ausführung kann man auch einen Brückenzweig völlig weglassen. Der Offset-Eingang befindet sich dann direkt am Komparator. 8. Eigenschaften der Gesamtschaltung 8.1 Geschwindigkeit : Das Schaltungskonzept wurde so ausgelegt, daß sich eine hohe Meßfrequenz erreichen läßt. Dafür verantwortlich sind : - Hohe Clockfrequenz Schnelle Pulsbreitenmodulation mittels response time eines schnellen Komparators. Die Zeitkonstante des Integralreglers ist relativ klein. Die dadurch in Kauf genommene Welligkeit wird durch ein aktives Tiefpaßfilter mit relativ hoher Grenzfrequenz eleminiert. Die Dioden in der Klemmschaltung werden mit Widerständen überbrückt. Mit diesen Maßnahmen ist z.B. bei einem Komparator mit 100ns response time eine Grenzfrequenz von 100 kHz erreichbar. 45 8.2 Hohe Auflösung : so Trotz der hohen Geschwindigkeit hat die Schaltung eine sehr hohe Auflösung. Wenn nur eine niedrige Grenzfrequenz gewünscht wird, dann reicht es aus, die letzte Ausgangsstufe auf diese Grenzfrequenz zu dimensionieren. Die Clock-Frequenz soll nicht verändert werden, da die response time des Komparators nicht beliebig verlängert werden kann. Bei einer sorgfältigen Auslegung des Layout's ist eine Auflösung von 12 bit bei 100 kHz Grenzfrequenz ohne weiteres möglich. Bei einer tieferen Grenzfrequenz ergibt sich eine entsprechend weitere höhere Auflösung. Getroffene Maßnahmen für eine hohe Auflösung : 55 - Wheatstone-Brücke mit gleich großen Brückenelementen. Die Brücke wird mit dem vollen Aussteuerbereich, das ist zwischen Masse und +UB, gespeist. Die Eingangsstufe, das ist der Komparator, hat eine Verstärkung von > 1000. Der folgende Operationsverstärker hat bei der betriebenen Frequenz noch eine Verstärkung von 100. 13 EP 0 745 861 A2 5 10 Komparator und Operationsverstärker werden zusammen im Open Loop betrieben. Die Open Loop Gesamtverstärkung ist das Produkt der beiden Komponenten ( hier : 100000 ). Die tatsächliche Verstärkung wird nur durch die Gegenkopplung R1, R2 ( Fig. 8 ) bestimmt. Niederer Eingangswiderstand, dadurch auch geringes Rauschen. Der kapazitive Eingangswiderstand liegt je nach Kapazitätwert der Brücke und Clock-Frequenz zwischen 1 kQ -10 kQ. Durch das aktive Filter wird die Grenzfrequenz auf den gewünschten Wert herabgesetzt, was ebenfalls der Auflösung zugute kommt. Die Versorgung für den Komparator erfolgt über einen zusätzlichen RC-Tiefpaß. Die Auflösung könnte zusätzlich noch um den Faktor 2 erhöht werden, indem die Brücke mit C1 , C2 nicht auf Masse geht, sondern mit einem genau gegenphasigen Clock-Signal verbunden wird. 8.3 Gute Temperaturstabilität : 15 20 25 Die Schaltung wurde für eine extrem hohe Temperaturstabilität konzipiert. Bei den meisten Anwendungsfällen ist der Temperaturkoeffizient der Schaltung wesentlich geringer als der des Meßkondensators. Maßnahmen für eine hohe Temperaturstabilität: Die Brückenreferenzkondensatoren sollen einen möglichst kleinen Temperaturkoeffizienten aufweisen. Der Arbeitspunkt des Komparators in der Eingangsstufe wird so gewählt, daß sich eine kleine overdrive-Spannung ( < 5 mV ) ergibt. Bei der Auswahl des Komparators ist darauf zu achten, daß sich die response time bei der gewählten overdrive-Spannung über die Temperatur sich relativ wenig ändert. Die Temperaturabhängigkeit der Eingangsstufe wird dann im wesentlichen durch die Formel .... -ris „,n0o, = Aoverdrive.,Verstärkung TKEingangsstufe r[mV/0°C] ^ 30 35 bestimmt. Die Verstärkung ergibt sich aus ( 1 + R2/R1 ). Die Offsetspannungsänderung des folgenden Operationsverstärkers hat praktisch keinen Einfluß, da diese Größe mit dem Faktor der Leerlaufverstärkung der ersten Stufe ( > 1000 ) dividiert wird. Die Offsetspannungsänderung des Operationsverstärkers im aktiven Filter geht nur mit dem Faktor ein und kann somit vernachläßigt werden. Die Brücke wird in der High-Phase des Clocks durch den Sperrstrom der Klemmdioden D1 , D2 teilweise entladen. Dies hat folgenden Einfluß auf Verstärkung und Nullpunkt : Oflse,TKDbd,„[%0/-Cl=1°°°^^-;'2'-' 45 50 55 wobei Air: Cp : t: Sperrstromänderung über die Temperaturänderung AT C1 + C3 bzw. C2 + C4 Halbe Periodendauer des Clock-Signals Mit üblichen Silizium - Universaldioden kommt man hier auf einen temperaturabhängigen Verstärkungskoeffizienderbereits inderNähevon 1 Promill/°C ist. Bei großem Temperaraturbereich (z.B. 100°C ) und hoher Verstärkung ten, 100 läuft ( ca. ) man bei der Drift bereits Gefahr, außerhalb des Meßbereichs zu kommen. Es gibt FET-Dioden die ca. einen um den Faktor 100 bis 1000 kleineren Sperrstrom haben. Bei Einsatz eines solchen Typs erreicht man selbst bei hoher Verstärkung und großem Temperaturbereich einen Driftbereich in Größenordnungen von wenigen Promill. Es ist von Vorteil, wenn D1 , D2 als eine Dualdiode ausgeführt ist, da dadurch beide Dioden dieselbe Umgebungstemperatur haben. 14 EP 0 745 861 A2 Für eine quasistatische Ausführung genügt eine Silizium-Diode, da hier die Offsetspannung nachgeregelt wird. Die Dioden sollen vorzugsweise als Dualdiode ausgeführt sein. Einzeldioden sollen thermisch gekoppelt werden und eine möglichst gleiche Durchlaßkennlinie aufweisen. Während der Low-Zeit des Clock-Impulses sind die Dioden leitend. Die Durchlaßspannung UF ist temperaturabhängig. Es entsteht dabei folgender Offstfehler: 5 ALU - AUF2 Offset TK Diode F [ mV / °C] = — ^— — - Verstärkung 15 Diese Offsetspannung ist linear mit der Temperatur und kann somit relativ leicht kompensiert werden. Bei extrem hohen Anforderungen kann man die Dioden auch auf konstante Temperatur halten. Prinzipiell kann man die Dioden ebenso durch Schaltemente ersetzen. In der High-Phase ist dann der Zustand AUS und in der Low-Phase der Zustand EIN. 20 Rechteckoszillator mit geregeltem Puls-Pausen-Verhältnis. Eine Änderung dieses Wertes geht direkt proportional ins Meßergebnis ein. Bei der Ausführung mit einem Komparator ändert sich der Umschaltpunkt nur um soviel, wie sich die Offsetspannung über die Temperatur ändert. Bei Einsatz eines Präzisionskomparators kann dieser Wert vernachläßigt werden. 8.4 Geringe Störempfindlichkeit 25 Tests haben gezeigt, daß die Störfestigkeit erstaunlich hoch ist. Neben den üblichen Entstörmaßnahmen ist dies auf folgende Gründe zurückzuführen : Niederer Innenwiderstand des Rechteckoszillators. Durch die hohe Clockfrequenz ergibt sich auch ein niederer kapazitiver Eingangswiderstand für die Schaltung. Niederer Innenwiderstand der Rückkopplung durch niederohmigen Widerstand R1 , R3. Der Komparator in der Eingangsstufe reagiert praktisch auf einen Mittelwert während der response time. Die Eingangsstufe kann nicht übersteuert werden, da sie als Pulsbreitenmodulator arbeitet. Die Störungen werden durch den nachfolgenden Integrator gedämpft. Das aktive Tiefpaßfilter filtert Störfrequenzen, die über der Meßfrequenz liegen, wirkungsvoll aus. 30 - 35 Verfahren zum Messen kleiner Kapazitäten oder Kapazitätsänderungen 40 45 50 55 Das Verfahren arbeitet mit einer 2-Phasenmethode. Das Grundprinzip basiert darauf, den Gleichspannungsanteil mindestens einer Brückenspannung (X, Y) in einer zweiten Phase so nachzuregeln, daß in einer ersten Phase die Brückendifferenzspannung null, bzw. exakter einen konstant sehr kleinen Wert e aufweist. Die Regelspannung ist dann das Maß für die Brückenverstimmung. Der Regler ist vorzugsweise ein Integralregler. Die Brückendiflerenzspannung wird dabei in einer ersten Phase von einem Pulsbreitenmodulator mit sehr hoher Empfindlichkeit erfaßt und als Pulsbreite abgebildet. Dieses Signal wird dann an den Integrator weitergegeben. Die Ausgangsspannung des Integrators stellt über eine Gegenkopplung in einer zweiten Phase unter Änderung des Gleichspannungsanteils mindestens einer Brückenspannung (X, Y) das Brückengleichgewicht (X= Y - e) für die erste Phase her. Für den Pulsbreitenmodulator ergibt sich eine besonders vorteilhafte Realisierung dadurch, daß ein Komparator zum Einsatz kommt, wobei als Eingangsgröße die überstejerungsspannung AU und als Ausgangsgröße die Antwortzeit At dient. Der Arbeitspunkt ( AU, At ) wird dabei günstigerweise so festgelegt, daß At gleich der halben Intervallzeit der ersten Taktphase ist und AU einen noch ausreichend kleinen Wert darstellt. Ein kleiner AU - Wert hat den Vorteil, daß sich Änderungen in der Ansprechzeit des Komparators über die Temperatur nur geringfügig auf AU und somit auf die Meßgenauigkeit auswirken. Da die Ansprechzeit schneller Komparatoren im ns-Bereich liegt, kann bei dieser Realisierung eine sehr hohe Taktfrequenz und in weiterer Folge eine sehr hohe Meßfrequenz erreicht werden. Der Pulsbreitenmodulator soll in einer zweiten Taktphase kein Signal liefern. Dies kann dadurch erreicht werden, daß entweder die Eingänge oder der Ausgang auf inaktiv geschaltet werden oder auch daß der Ausgang während dieser Zeit auf ein konstantes Potential, vorzugsweise Masse, geschaltet wird. Das Brückengleichgewicht (X = Y - e) wird in einer ersten Phase dadurch hergestellt, daß ein Teil der Integratorspannung über eine Gegenkopplung (G) an an mindestens eine Brückenspannung, das ist an die Brückenspannung X oder invertiert an die Brückenspannung Y zurückgeführt wird und daß eine konstante Gleichspannung N mindestens 15 EP 0 745 861 A2 einer Brückenspannung (X, Y) überlagert wird, wobei die Beziehung gilt: Nx + Ny = konstant = vorzugsweise U_Batterie. Bei einer Vollbrücke ist dann im einfachsten Fall der eine Brückenzweig mit der Gegenkopplung und der andere mit dem Abgleich verbunden. Bei Anwendungen, wo der Meßkondensator keinen Gleichspannungsanteil aufweisen darf, schaltet man einen Kondensator mit theoretisch °°, in der Praxis mit dem mindestens 100-fachen Wert der Meßkapazität in Serie zum Meßkondensator. Bei einer Halbbrücke ist der Brückenzweig mit der Gegenkopplung und der Abgleich mit dem zweiten Eingang des Pulsbreitenmodulators verbunden. Unter Beachtung der Gegenkopplungsbedingung ist auch der umgekehrte Fall möglich : Der Brückenzweig wird mit dem Abgleich und der zweite Eingang mit der Gegenkopplung verbunden. Die erste Methode hat den Vorteil, daß die Spannungen (X, Y) in einer ersten Phase konstant bleiben und dadurch nur geringe Anforderungen an die Gleichtaktunterdrückung des Pulsbreiten-modulators bestehen. Bei einer Vollbrücke gilt analog dies ebenso. Es gibt Anwendungen, wo eine statische Messung z.B. infolge von großen Temperatureinflüssen nicht sinnvoll ist und ein automatischer Nullpunktsabgleich bevorzugt wird. Dies wird erfindungsgemäß dadurch erreicht, indem ein zweiter Integralregler mit großer Integrationszeitkonstante in Abhängigkeit vom Integrationsergebnis des ersten Integralreglers auf einen konstanten Referenzwert regelt. Die Stellgröße des zweiten Integralreglers wird mit dem Eingang 'Offset' verbunden. Bei einem anderen Anwendungsfall wird ein bestimmter Verstärkungs-Temperaturkoeffizient gewünscht um z.B. den der Mechanik zu kompensieren. Dies wird erfindungsgemäß dadurch erreicht, daß die Spannungsamplitude des Taktsignals in mindestens einem Brückenzweig von einer temperaturabhängigen Spannung gesteuert wird. Die Steuerung der Amplitude in beiden Brückenzweigen ist dabei vorzuziehen, weil dadurch keine Nullpunktsänderungen entstehen. Die Änderung der Spannungsamplitude kann dabei auf einfache Weise durch eine Hubbegrenzung des Taktsignals ausgeführt sein. Bei einem weiteren Anwendungsfall soll die Ausgangsgröße linear zum Normalabstand eines Platten kondensators sein. Dies kann dann erreicht werden, wenn man in linearer Abhängigkeit vom Integrationsergebnis die Amplitude der vom Taktsignal abgeleiteten Spannung des Brückenzweiges verringert, in dem sich auch der Meßkondensator befindet. Mit dieser Methode läßt sich eine perfekte Linearisierung des ansonsten hyperbelförmigen Verlaufs erreichen. Die Umsetzung von Kapazität auf Spannung läßt sich auf folgende Formel zurückführen : Bei einer Vollbrücke ( 2 Brückenzweige ) : . . . C4 . C3 1, wobei C1 , C2 auf einer Seite mit Masse und C3, C4 mit einer Seite mit der Brückenspeisung verbunden sind. C1 bildet mit C3 den 1. Brückenzweig, C2 mit C4 den 2. Brückenzweig. Bei einer Halbbrücke ( nur 1. Brückenzweig ) : (2) ua=vub(J-ct^3) wobei v := n := uA := uB := Verstärkungsfaktor Faktor für die Nullpunktseinstellung Ausgangsspannung Spannungshub Brückenspeisung Die beiden Kompensationen für Temperatur und Linearität schließen sich gegenseitig nicht aus und können daher auch gleichzeitig angewandt werden. Das Taktsignal soll ein festes Taktverhältnis aufweisen, da das Tastverhältnis über die Integration in das Meßergebnis eingeht. Das günstigste Tastverhältnis ist 1 : 1, da beide Taktphasen die annähernd gleichen Einschwingzeiten benötigen. Die Gegenkopplung (G) kann den Gleichspannungsanteil entweder in beiden Taktphasen über einen Widerstand in die Brückenspannung (X) oder invertiert in (Y) einkoppeln, oder es wird nur in einer zweiten Phase über eine Klemmschaltung oder einen Analogschalter eingekoppelt. Im ersten Fall ist bei gleicher Gegenkopplung (G) die Verstärkung um den Faktor 2 - bei symmetrischem Tastverhältnis des Taktsignals - kleiner. Der zweite Fall ist zum Erreichen einer hohen Meßfrequenz günstiger, da man im ersten Fall relativ hochohmig einkoppeln muß, damit die Meßbrücke nicht zu sehr entladen wird und sich dadurch auch große Zeitkonstanten ergeben. Die höchste Meßfrequenz wird mit einer 16 EP 0 745 861 A2 Dioden-Klemmschaltung ermöglicht. Zum Erreichen einer sehr hohen Meßfrequenz ist es auch sehr vorteilhaft die Integrationszeitkonstante relativ klein ( 1 .. 10 - fache der Taktperiode) zu wählen und dafür eine größere Welligkeit des Integratorausgangs in Kauf zu nehmen. Diese Welligkeit kann sehr leicht durch Nachschalten eines steilen Tiefpaßfilters, dimensioniert auf die gewünschte Meßfrequenz, beseitigt werden. Patentansprüche 1. Verfahren zum Messen kleiner Kapazitäten mit einer selbstabgleichenden Brückenschaltung (A), wobei die Kapazität oder die Kapazitätsänderung eines unbekannten Kondensators (C1) in einem Brückenzweig bzw. die Kapazitäten oder die Kapazitätsänderung zweier unbekannter Kondensatoren (C1 , C2) in zwei verschiedenen Brükkenzweigen bestimmt wird und die aus Referenzkondensatoren (C2, C3, C4 bzw. C3, C4) und einem unbekannten Kondensator (C1) oder unbekannten Kondensatoren (C1, C2) gebildete Brücke (A) an zwei ersten Diagonalpunkten mit einer periodischen, im wesentlichen rechteckförmigen Spannung (T) mit konstanter Amplitude gespeist wird, wobei die Rechteckspannung (T) in einer Periode jeweils von einem ersten (T(0)) auf einen zweiten Pegel (T(1)) wechselt, dadurch gekennzeichnet, daß fortlaufend nur während des zweiten Pegels (T(1)) des Rechtecksignals die Spannungsdifferenz an zwei zweiten Diagonalpunkten (X, Y) der Brücke in einem Synchronverstärker (D), vorzugsweise einem Komparator, leerlaufverstärkt wird, und während des ersten Pegels (T(0)) der Synchronverstärker (D) ein vorbestimmtes Potential abgibt, sodann das leerlaufverstärkte Ausgangssignals des Synchronverstärkers mittels eines Reglers, vorzugsweise eines Integralreglers (E), auf einen Sollwert geregelt wird, welcher Sollwert durch den Zeitmittelwert der Ausgangsspannung des Synchronverstärkers bei abgeglichener Brücke festgelegt ist, daß mittels der Ausgangspannung des Reglers (E) über einen Gegenkopplungszweig (G) und eine abgleichbare Klemmschaltung (C) die Brücke (A) an den zweiten Diagonalpunkten (X, Y) in Abgleich gebracht wird, wobei die Ausgangsspannung (UA) des Reglers (E) im wesentlichen proportional der Kapazität oder der Kapazitätsänderung des unbekannten Kondensators (C1) bzw. der unbekannten Kondensatoren (C1, C2) ist. 2. Verfahren nach Anspruch 1, dadurch gekennzeichnet, daß die integrierte Spannung mit einem Tiefpaß-Filter (F) geglättet wird, wobei die geglättete Ausgangsspannung (U_out) proportional der Kapazität oder der Kapazitätsänderung des unbekannten Kondensators (C1) bzw. der unbekannten Kondensatoren (C1, C2) ist 3. Verfahren nach Anspruch 2, dadurch gekennzeichnet, daß zur quasistatischen Kapazitätsmessung die geglättete Ausgangsspannung in einem weiteren Integralregler in bezug auf einen weiteren Sollwert integriert und diese integrierte Spannung einem dem Abgleich dienenden Eingang (Offset) der Klemmschaltung zugeführt wird, wobei die geglättete Ausgangsspannung proportional der Kapazität oder der Kapazitätsänderung des unbekannten Kondensators (C1 ) bzw. der Kapazitätsdifferenz oder deren Änderung der unbekannten Kondensatoren (C1 , C2) ist. 4. Schaltungsanordnung zur Durchführung des Verfahrens nach Anspruch 1, wobei eine aus Referenzkondensatoren (C2, C3, C4 bzw. C3, C4) und einer oder zwei unbekannten Kapazitäten (C1 bzw. C1, C2) gebildete Brückenschaltung (A) an den zwei ersten Diagonalpunkten mit einem Rechteckgenerator (B) verbunden ist, der eine konstante im wesentlichen rechteckförmige Rechteckausgangsspannung (T) liefert, dadurch gekennzeichnet, daß die zwei zweiten Diagonalpunkte (X, Y) mit den Eingängen eines Synchronverstärkers (D) verbunden sind, welcher die Differenz der an den beiden zweiten Diagonalpunkten (X, Y) gemessenen Potentiale nur während des zweiten Pegels (T(1)) des Rechteckgenerators (B) verstärkt, daß der Ausgang des Synchronverstärkers (D) mit einem ersten Eingang eines Reglers, vorzugsweise eines Integralreglers (E), verbunden und während des ersten Pegels (T(0)) der Rechteckspannung auf einem vorbestimmten Potential gehalten ist, und der Ausgang des Reglers (E) mit dem Eingang einer Gegenkopplungsschaltung (G) verbunden ist, daß deren Ausgang mit einem ersten Eingang einer Klemmschaltung (C) verbunden ist, daß ein zweiter Eingang des Reglers (E) mit einer konstanten Sollspannungsquelle (Ref) verbunden ist und ein erster bzw. zweiter Ausgang der Klemmschaltung (C) mit den beiden zweiten Diagonalpunkten verbunden sind, wobei ein zweiter Eingang (Offset) der Klemmschaltung (C) mit einer Abgleichsspannungsquelle verbunden ist und daß am Ausgang des Reglers (E) eine dem Wert des unbekannten Kondensators bzw. der unbekannten Kondensatoren oder deren Änderungen proportionale Ausgangsspannung abgreifbar ist. 5. Schaltungsanordnung nach Anspruch 4, dadurch gekennzeichnet, daß dem Ausgang des Integralreglers (E) ein Tiefpaß-Filter (F) nachgeschaltet ist. 17 EP 0 745 861 A2 5 6. Schaltungsanordnung nach Anspruch 5, dadurch gekennzeichnet, daß das Tiefpaß-Filter (F) ein aktives TiefpaßFilter ist. 7. Schaltungsanordnung nach Anspruch 6, dadurch gekennzeichnet, daß das aktive Tiefpaß-Filter durch ein zweipoliges Filter gebildet ist und an dessen Ausgang ein RC-Tiefpaß (R41 , C31) nachgeschaltet ist. 8. Schaltungsanordnung nach Anspruch 6 oder 7, dadurch gekennzeichnet, daß das aktive Tiefpaß-Filter (F) durch einen Operationsverstärker mit einer zwischen Ausgang und invertierendem Eingang gekoppelten Parallelschaltung aus einem Kondensator (C21) und einem Widerstand (R31) gebildet ist, und daß der nichtinvertierende Eingang des Operationsverstärkers mit einer konstanten Referenzspannung verbunden ist. 9. Schaltungsanordnung nach Anspruch 6, dadurch gekennzeichnet, daß das aktive Tiefpaß-Filter (F) mehrpolig ist. 10 15 20 25 30 35 40 45 50 55 10. Schaltungsanordnung nach einem der vorhergehenden Ansprüche 4 bis 9, dadurch gekennzeichnet, daß der Synchronverstärker (D) aus einem Differenzverstärker gebildet ist, wobei der Ausgang des Differenzverstärkers zur Synchronisation mit einem Widerstand und einem vom Rechtecksignal gesteuerten Schalter in Serie verbunden ist. 11. Schaltungsanordnung nach einem der vorhergehenden Ansprüche 4 bis 10, dadurch gekennzeichnet, daß der Synchronverstärker (D) durch eine Abtast- und Halteschaltung gebildet ist. 12. Schaltungsanordnung nach Anspruch 11 , dadurch gekennzeichnet, daß der Synchronverstärker (D) durch einen Pulsbreitenmodulator gebildet ist und die Pulsmodulation durch die Abhängigkeit der Antwortzeit des Ausgangs eines Differenzverstärkers von der Größe der Spannung am Eingang des Differenzverstärkers erfolgt. 13. Schaltungsanordnung nach Anspruch 12, dadurch gekennzeichnet, daß der Pulsbreitenmodulator einen Komparator umfaßt, dessen Eingänge mit den beiden zweiten Diagonalpunkten (X, Y) verbunden sind, wobei die Antwortzeit des Ausgangssignals des Komparators eine Funktion des an seinem Eingang angelegten Spannungswertes ist. 14. Schaltungsanordnung nach Anspruch 13, dadurch gekennzeichnet, daß der Ausgang des Komparators zur Synchronisation über einen Pull-up-Widerstand (R8) mit dem Ausgang des Rechteckgenerators (B) verbunden ist. 15. Schaltungsanordnung nach Anspruch 13, dadurch gekennzeichnet, daß der Komparator einen Latch- oder Inhibit- Eingang aufweist. 16. Schaltungsanordnung nach Anspruch 13 oder 15 ,dadurch gekennzeichnet, daß der Ausgang des Komparators mit einer Basis eines Schalttransistors mit kurzer Schaltzeit verbunden ist, dessen Kollektor einen Open-Collector bildet. 17. Schaltungsanordnung nach einem der vorhergehenden Ansprüche 4 bis 16, dadurch gekennzeichnet, daß der Integralregler (E) aus einem Differenzverstärker gebildet ist, bei dem ein Integrierkondensator (C5) zwischen Ausgang und invertierendem Eingang vorgesehen ist, welcher invertierender Eingang über einen Widerstand (R9) den Eingang des Integralreglers bildet und bei dem der nichtinvertierende Eingang mit einer Sollspannungsquelle verbunden ist, wobei die Zeitkonstante des Integralreglers durch das Produkt von Widerstand (R9) und Integrierkondensator (C9) bestimmt ist. 18. Schaltungsanordnung nach Anspruch 17, dadurch gekennzeichnet, daß die Zeitkonstante des Integralreglers (E) größer oder gleich der Periode der Ausgangsspannung des Rechteckgenerators (B) ist. 19. Schaltungsanordnung nach Anspruch 17, dadurch gekennzeichnet, daß das Verhältnis der Zeitkonstante des Integralreglers zur Periodendauer des Rechtecksignals in einem Bereich zwischen 1 und 10 liegt. 20. Schaltungsanordnung nach Anspruch 17, 18 oder 19, dadurch gekennzeichnet, daß die Sollspannungsquelle eine konstante Spannung aufweist, deren Wert ein Viertel des Hochpegels des Rechteckgenerators (B) beträgt. 21. Schaltungsanordnung nach einem der vorhergehenden Ansprüche 4 bis 20, dadurch gekennzeichnet, daß die Gegenkopplungsschaltung (G) aus einem ersten mit einem der zweiten Diagonalpunkte verbundenen Gegenkopp- 18 EP 0 745 861 A2 lungswiderstand (R2) und einem mit diesem verbundenen zweiten Gegenkopplungswiderstand (R1), der an seinem anderen Ende mit Masse verbunden ist, gebildet ist. 5 10 15 20 25 30 35 22. Schaltungsanordnung nach einem der vorhergehenden Ansprüche 4 bis 21 , dadurch gekennzeichnet, daß die Klemmschaltung (C) über einen ersten Klemmwiderstand (R5) einen der zweiten Diagonalpunkte mit dem Verbindungspunkt zwischen den Gegenkopplungswiderständen (R2, R1) verbindet und über einen zweiten Klemmwiderstand (R6) den andern der zweiten Diagonalpunkte mit dem Abgriffspunkt eines aus Widerständen (R3, R4) gebildeten Spannungsteiler verbindet, wobei eine am zweiten Eingang (Offset) der Klemmschaltung anliegende Abgleichsspannung durch den Spannungsteiler geteilt wird. 23. Schaltungsanordnung nach Anspruch 22, dadurch gekennzeichnet, daß zum ersten bzw. zweiten Klemmwiderstand (R5 bzw. R6) eine erste bzw. zweite Klemmdiode (D1 bzw. D2) parallel geschaltet ist. 24. Schaltungsanordnung nach Anspruch 23, dadurch gekennzeichnet, daß die erste und die zweite Klemmdiode (D1 , D2) als Doppeldiode in einem Gehäuse angeordnet sind. 25. Schaltungsanordnung nach einem der vorhergehenden Ansprüche 4 bis 24, dadurch gekennzeichnet, daß ein weiterer Integralregler zwischen dem Ausgang des Tiefpaß-Filters (F) und dem zweiten Eingang (Offset) der Klemmschaltung (C) geschaltet ist. 26. Schaltungsanordnung nach einem der vorhergehenden Ansprüche 4 bis 25, dadurch gekennzeichnet, daß die Referenzkondensatoren (C3, C4) über je einen Widerstand (R10, R11) mit dem Ausgang des Rechteckgenerators (B) verbunden sind, wobei die Verbindungspunkte zwischen den Referenzkondensatoren (C3,C4) und den Widerständen (R10, R11) über je eine Diode (D5, D4) Kompensationseingänge (Comp_x, Comp_y) bilden. 27. Schaltungsanordnung nach Anspruch 26, dadurch gekennzeichnet, daß zur Kompensation des Temperaturganges die beiden Kompensationseingänge (Comp_x, Comp_y) über einen temperaturabhängigen Widerstand mit einer temperaturstabilen Referenzspannung (U_Temp) verbunden sind. 28. Schaltungsanordnung nach Anspruch 26, dadurch gekennzeichnet, daß zur Kompensation des Temperaturganges die beiden Kompensationseingänge (Comp_x, Comp_y) mit einem aktiven Temperatursensor verbunden sind. 29. Schaltungsanordnung nach einem der vorhergehenden Ansprüche 4 bis 28, dadurch gekennzeichnet, daß zur Kompensation der Nichtlinearität der der Kapazität (C1) bzw. der Kapazitätsänderung proportionalen AusgangsSpannung der Kompensationseingang (Comp_x) über einen Linearisierungs-Widerstand (R7) mit dem Ausgang des Integralreglers (E) bzw. dem Ausgang des Tiefpaß-Filters (F) verbunden ist, und das Verhältnis von Widerstand (R10) zu Linearisierungs-Widerstand (R7) gleich vs-1 beträgt, wobei v die Verstärkung, s= C3/(Cp + C3) ist und Cp eine konstante zu C1 parallele Kapazität darstellt. 40 45 50 55 19 EP 0 745 861 A2 Clock T _ _ n _ j H T(0) T(1) Y X = OV = UB X(1) = X(0) + Y(1) = Y(0) + AX AY AX = C 3 / ( C 1 +C3) AY = C4 / ( C2 + C4 ) F I G . gewählt :X(1) = Y(1) X(0) Y(0) X(1) Y(1) - AX - AY T * > T(o) t X Y C1 -> > C2 t F I G . 20 l b EP 0 745 861 A2 B Offset FIG. 21 2 a EP 0 745 861 A2 Fl 22 6. 2 b EP 0 745 861 A2 T ^ m > t > t > t m a b m • • • I a b F I G 23 EP 0 745 861 A2 Z A | |— | j j ! | L_1_J a b a response time b active time ( on ) c clock low —i i — i > t c F I G . 24 EP 0 745 861 A2 Offset I <r -• Ret Integralregler F I G . 25 $ EP 0 745 861 A2 • U_Temp R_Temp Comp_y i 1 Comp_x U out F I G . 6 R Lin Comp_y* UA Comp_x U out F I G . ? 26 ZJ 1—l~H>h-* J — 1— T T ^ l 1 sfl as 'cJ 1 1 Y 3 -r, 7} M ^ (DM !2 V r 1 \