3.6 Addition und Subtraktion von Gleitkommazahlen 3.7

Werbung

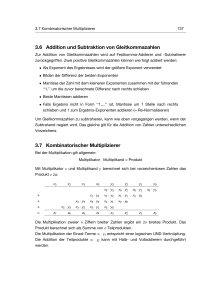

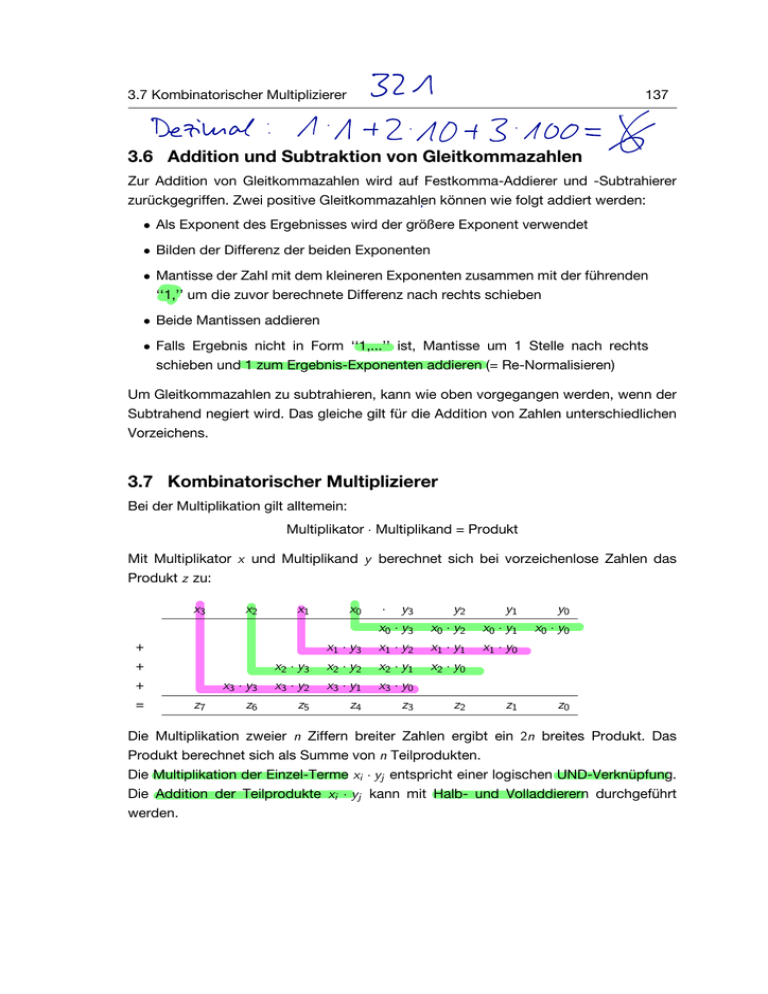

321 3.7 Kombinatorischer Multiplizierer Bethnal : 1 . 137 1+2.10+3.100=6 3.6 Addition und Subtraktion von Gleitkommazahlen Zur Addition von Gleitkommazahlen wird auf Festkomma-Addierer und -Subtrahierer zurückgegriffen. Zwei positive Gleitkommazahlen können wie folgt addiert werden: . • Als Exponent des Ergebnisses wird der größere Exponent verwendet • Bilden der Differenz der beiden Exponenten • Mantisse der Zahl mit dem kleineren Exponenten zusammen mit der führenden ‘‘1,’’ um die zuvor berechnete Differenz nach rechts schieben • Beide Mantissen addieren • Falls Ergebnis nicht in Form ‘‘1,...’’ ist, Mantisse um 1 Stelle nach rechts schieben und 1 zum Ergebnis-Exponenten addieren (= Re-Normalisieren) Um Gleitkommazahlen zu subtrahieren, kann wie oben vorgegangen werden, wenn der Subtrahend negiert wird. Das gleiche gilt für die Addition von Zahlen unterschiedlichen Vorzeichens. 3.7 Kombinatorischer Multiplizierer Bei der Multiplikation gilt alltemein: Multiplikator · Multiplikand = Produkt Mit Multiplikator x und Multiplikand y berechnet sich bei vorzeichenlose Zahlen das Produkt z zu: x3 + + + = z7 x2 x 3 · y3 z6 x1 x0 x2 · y 3 x3 · y 2 z5 x1 · y3 x2 · y2 x3 · y1 z4 · y3 x 0 · y3 x 1 · y2 x 2 · y1 x 3 · y0 z3 y2 x0 · y 2 x1 · y 1 x2 · y 0 y1 x0 · y1 x1 · y0 y0 x 0 · y0 z2 z1 z0 Die Multiplikation zweier n Ziffern breiter Zahlen ergibt ein 2n breites Produkt. Das Produkt berechnet sich als Summe von n Teilprodukten. Die Multiplikation der Einzel-Terme xi · yj entspricht einer logischen UND-Verknüpfung. Die Addition der Teilprodukte xi · yj kann mit Halb- und Volladdierern durchgeführt werden. 138 a) 3 Arithmetische Schaltungen Tragen Sie in nachfolgende Abbildung Verbindungen zur Realisierung der vorzeichenlosen Multiplikation ein. x3 Eigene Lösung: x3 · y3 x 0 · y3 x 1 · y2 x 2 · y1 x 3 · y0 z3 x0 y2 x0 · y 2 x1 · y 1 x2 · y 0 y1 x0 · y1 x1 · y0 y0 x 0 · y0 z2 z1 z0 MM A z7 x1 x0 x1 · y3 x2 · y2 x3 · y1 z4 x2 · y 3 x3 · y 2 z5 x 3 · y3 z6 y3 · y2 y1 y0 • y • x1 of + + + = x2 x2 IEEE ? * ni at .fi#hg&&b.: a b a s cout cin a HA cout a b cin a VA cout a b cin a VA cout VA s cout cin a VA s z7 b cout z6 b b cout z5 a cin a s cout s cout cin a b VA b b VA cout s cin a b cout s HA cout z3 s z2 z1 b HA HA s s z4 cin VA VA s b z0 s . 3.7 Kombinatorischer Multiplizierer 139 Zur Mitschrift: x3 + + + = x3 x2 z7 x1 x0 a x2 x1 x0 x 3 · y3 z6 x2 · y 3 x3 · y 2 z5 x1 · y3 x2 · y2 x3 · y1 z4 y3 · b a HA cout a b cin a VA cout a b cin a VA cout s cout cin a cout z6 b s cout cin a cout z5 b y2 x0 · y 2 x1 · y 1 x2 · y 0 y1 x0 · y1 x1 · y0 y0 x 0 · y0 z2 z1 z0 y1 a b y0 cin a VA cout s cin a b cout HA cout s cin a b cout s HA cout z3 s z2 z1 b HA s s s z4 cin VA VA s y2 VA VA VA s z7 b b b · y3 x 0 · y3 x 1 · y2 x 2 · y1 x 3 · y0 z3 z0 s 140 3 Arithmetische Schaltungen b) Tragen Sie in die Multiplizierer-Schaltung den längsten Pfad ein. Wie lange (in Gatterlaufzeiten ⌧ ) dauert die Ausführung? 13¥ 16T Der Hardwareaufwand der gezeigten Schaltung ist sehr hoch: Mit steigender Wortbreite n steigt der notwendige Hardwareaufwand mit ca. n2 . 3.8 Sequentieller Multiplizierer 141 3.8 Sequentieller Multiplizierer Mit einer sequentiellen Schaltung kann der Hardwareaufwand reduziert werden. Die nächste Abbildung skizziert eine sequentielle Schaltung, die zur Multiplikation vorzeichenloser Zahlen der Wortbreite n = 4 verwendet werden kann. MR y3 y2 y1 y0 Add PR 0 0 0 0 PR0 0 x3 x2 x1 x0 Das Multiplikand-Register MR ist n = 4 Bit breit, das Produkt-Register PR ist 2n + 1 = 9 Bit breit. PR0 ist das niederwertigste Bit des im Produktregister gespeicherten Werts. Der sequentielle Ablauf ist wie folgt: • Zunächst wird der Multiplikand im Multiplikand-Register MR und der Multiplikator in den unteren n Bits des Produkt-Registers abgelegt. Die restlichen Bits des Produktregisters werden mit 0 initialisiert. • Anschließend wird iterativ n = 4 mal folgendes ausgeführt: • Wenn PR0 = 1, dann • wird der in MR stehende Wert zu den Bits PR7 ... PR4 des Produktsregisters addiert; ein ggf. auftretender Überlauf wird in PR8 abgelegt; anschließend • wird das gesamte Produktregister um eine Stelle nach rechts geschoben; dabei wird von links mit Nullen aufgefüllt. • Wenn PR0 = 0, dann • wird keine Addition durchgeführt, sondern lediglich das gesamte Produktregister um eine Stelle nach rechts geschoben; dabei wird wieder von links mit Nullen aufgefüllt. • Nach n = 4 Iterationen (=Runden) steht im Produktregister das Ergebnis. 142 a) 3 Arithmetische Schaltungen Tragen Sie in folgende Abbildung für n = 4 die Registerinhalte ein, die sich für die Multiplikation 13 · 5 = 65 ergeben. ÷ Add 0 Nach Addition: Nach Schieben: Nach Addition: Nach Schieben: Nach Addition: 0 0010 Nach Schieben: 0 1 1 1 01 Initialisierung 01 Erste Runde 11 Doorway Erste Runde .d¥¥#u old 10 001 Nach Schieben: Nach Addition: 0 Ott Agata 6000^1 0^11 ogyiobotoyiox Zweite Runde Zweite Runde Dritte Runde Dritte Runde Vierte Runde Vierte Runde 3.8 Sequentieller Multiplizierer 143 Nachfolgende Abbildung zeigt den (unvollständigen) Aufbau einer Schaltung zur Implementierung des gezeigten Multiplikationsverfahrens. b) Vervollständigen Sie die Schaltung so, dass sie vorzeichenlose Binärzahlen multipliziert. Steuerung Multiplikator . . o¥- PRO 3.7 Multiplizierer 141 n Init/>>1 Sequentielle Multiplikation vorzeichenloser Zahlen 0..n-1 Schaltung zur 0..n-1 ±¥¥EIE8¥ PR ' Mit einer sequentiellen Schaltung kann der Hardwareaufwand deutlich reduziert werden. Die nächste Abbildung skizziert eine sequentielle Schaltung, die zur Multiplikation von n..2n n..2n-1 vorzeichenloser Zahlen der Wortbreite n = 4 verwendet werden kann: MR y3 y2 y1 y0 Add PR 0 0 0 0 Produkt 2n PR0 0 x3 x2 x1 x0 Addierer MR Multiplikand n Das Multiplikand-Register MR ist n = 4 Bit breit, das Produkt-Register PR ist 2n + 1 = 9 Bit breit. PR0 ist das niederwertigste Bit des im Produktregister gespeicherten Werts. Der Ablauf ist wie folgt: • Zunächst wird der Multiplikand im Multiplikand-Register MR und der Multiplikator in den unteren n Bits des Produkt-Registers abgelegt. Die restlichen Bits des Produktregisters werden mit 0 initialisiert. • Anschließend wird iterativ n = 4 mal folgendes ausgeführt: • Wenn PR0 = 1, dann • wird der in MR stehende Wert zu den Bits PR7 ... PR4 des Produktsregisters addiert; ein ggf. auftretender Überlauf wird in PR8 abgelegt; anschließend • wird das gesamte Produktregister um eine Stelle nach rechts geschoben; dabei wird von links mit Nullen aufgefüllt. • Wenn PR0 = 0, dann • wird keine Addition durchgeführt, sondern lediglich das gesamte Produktregister um eine Stelle nach rechts geschoben; dabei wird wieder von links mit Nullen aufgefüllt. • Nach n = 4 Iterationen (=Runden) steht im Produktregister das Ergebnis.