Thema: Speicher-Schaltungen in CMOS

Werbung

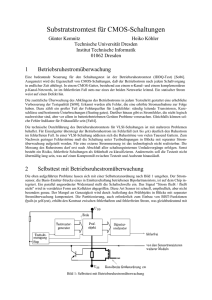

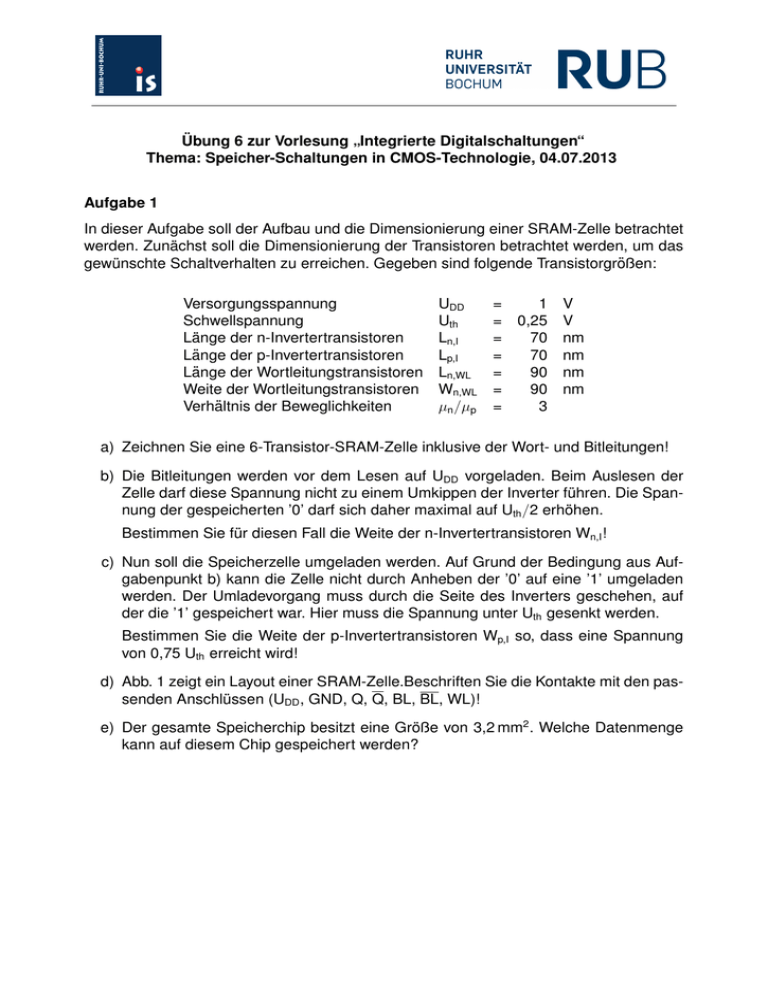

Übung 6 zur Vorlesung Integrierte Digitalschaltungen“ ” Thema: Speicher-Schaltungen in CMOS-Technologie, 04.07.2013 Aufgabe 1 In dieser Aufgabe soll der Aufbau und die Dimensionierung einer SRAM-Zelle betrachtet werden. Zunächst soll die Dimensionierung der Transistoren betrachtet werden, um das gewünschte Schaltverhalten zu erreichen. Gegeben sind folgende Transistorgrößen: Versorgungsspannung UDD Schwellspannung Uth Länge der n-Invertertransistoren Ln,I Länge der p-Invertertransistoren Lp,I Länge der Wortleitungstransistoren Ln,WL Weite der Wortleitungstransistoren Wn,WL Verhältnis der Beweglichkeiten µn /µp = 1 = 0,25 = 70 = 70 = 90 = 90 = 3 V V nm nm nm nm a) Zeichnen Sie eine 6-Transistor-SRAM-Zelle inklusive der Wort- und Bitleitungen! b) Die Bitleitungen werden vor dem Lesen auf UDD vorgeladen. Beim Auslesen der Zelle darf diese Spannung nicht zu einem Umkippen der Inverter führen. Die Spannung der gespeicherten ’0’ darf sich daher maximal auf Uth /2 erhöhen. Bestimmen Sie für diesen Fall die Weite der n-Invertertransistoren Wn,I ! c) Nun soll die Speicherzelle umgeladen werden. Auf Grund der Bedingung aus Aufgabenpunkt b) kann die Zelle nicht durch Anheben der ’0’ auf eine ’1’ umgeladen werden. Der Umladevorgang muss durch die Seite des Inverters geschehen, auf der die ’1’ gespeichert war. Hier muss die Spannung unter Uth gesenkt werden. Bestimmen Sie die Weite der p-Invertertransistoren Wp,I so, dass eine Spannung von 0,75 Uth erreicht wird! d) Abb. 1 zeigt ein Layout einer SRAM-Zelle.Beschriften Sie die Kontakte mit den passenden Anschlüssen (UDD , GND, Q, Q, BL, BL, WL)! e) Der gesamte Speicherchip besitzt eine Größe von 3,2 mm2 . Welche Datenmenge kann auf diesem Chip gespeichert werden? 560 nm n−Si p−Si PolySi Kontakt 1280 nm Abb. 1: Layout einer SRAM-Zelle Aufgabe 2 In dieser Aufgabe soll eine Ein-Transistor-DRAM-Speicherzelle betrachtet werden. Für den Speicher gelten folgende Werte: Versorgungsspannung UDD Schwellspannung Uth Leckstrom ILeck Speicherkapazität CS Bitleitungskapazität CBL = = = = = 3,3 0,7 0,5 40 160 V V pA fF fF a) Zeichnen Sie die Schaltung einer DRAM-Speicherzelle inklusive ihrer Bit- und Wortleitungen! b) Eine DRAM-Speicherzelle soll die Information ’1’ speichern. Dazu wird an die Bitleitung UDD angeschlossen und die Wortleitung schaltet den Transistor durch. Welche maximale Spannung US,max kann im Speicherkondensator gespeichert werden? c) Diese Spannung ist nun im Kondensator gespeichert und soll nach einiger Zeit wieder ausgelesen werden. Die Bit-Leitung ist vor dem Lesezugriff nicht vorgeladen. Bestimmen Sie die Spannung, die in diesem Fall beim Auslesen auf der Bitleitung maximal erreicht wird! d) Damit die ’1’ vom Schreib-Lese-Verstärker richtig erkannt wird, muss allerdings an der Bitleitung noch eine Spannung von UBL = 0,51 · UDD anliegen. Die Bit-Leitung wird deshalb vor dem Lesen auf 0,5 · UDD vorgeladen. Bestimmen Sie die Spannung, die am Kondensator anliegen muss, um die Bitleitung beim Auslesen der ’1’ auf 0,51 · UDD zu laden! e) Durch Leckströme sinkt die Spannung am Speicherkondensator zwischen dem Schreib- und dem Lesezyklus ab. Bestimmen Sie aus der maximalen Speicherspannung und der erforderlichen Spannung (bei vorgeladener Bitleitung) die maximale Haltezeit! 2