Systemprogrammierung (37-023)

Werbung

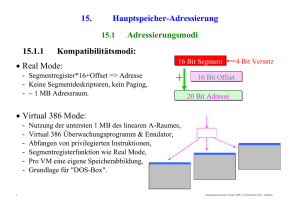

Systemprogrammierung (37-023) Assemblerprogrammierung Betriebssystemgrundlagen Maschinenmodelle Dozent: Prof. Thomas Stricker Unterrichtssprache: Deutsch Begleit-/Textbuch: R. P. Paul: SPARC Architecture, Assembly Language Programming and C, Prentice Hall, 1994 Heute: • Fliesspunktarithmetik • Repräsentation • IEEE Standard 754 • Addition / Multiplikation • FPUs und Parameterübergabe 24.1.00 - 1 37-023 Systemprogrammierung © Stricker Repräsentation • In vielen Applikationen müssen Nicht-Integer Zahlen behandelt werden • Es gibt diverse Verfahren, um Nicht-Integer Zahlen zu repräsentieren. Einfachste Möglichkeit ist Fixpunkt-Arithmetik • Allgemeine Repräsentation einer Zahl N durch Verschieben des Exponenten: N = Sdn – 1 × R n–1 + … + d0 + … + d– f × R – f (0.1) • Die Genauigkeit ist dabei durch den Faktor f vorgegeben, welcher die Verschiebung der Kommastelle (Dezimal, Binär) im jeweiligen Zahlensystem festlegt. (+/-10-f) Beispiel: Pi in verschiedenen Zahlensystemen 24.1.00 - 2 37-023 Systemprogrammierung © Stricker • Somit kann eine einfache binäre FixpunktRepräsentation wie folgt gegeben werden: • Addition und Subtraktion sind ohne Änderung des Algorithmus durchführbar, wobei sich bei Erhöhung der Genauigkeit um ein Bit der Bereich darstellbarer Zahlen im Register halbiert. • Bei Multiplikation muss die zusätzliche Verschiebung des Exponenten beachtet werden: a*2-4 *b*2-4 = a*b*2-8 • Daher muss Ergebnis auf die Genauigkeit der Operanden begrenzt und gerundet werden. • Dies kann durch Rechtsshift erfolgen: smul %o0, %o1, %o0 sra %o0, 4, %o0 !Ergebnis auf 4 Nachkommastellen begrenzt, %Y ignoriert oder sll sdiv 24.1.00 - 3 %o0, 4, %o0 %o0, %o1, %o0 37-023 Systemprogrammierung !Vornormierung © Stricker • Mantisse und Exponent müssen also getrennt repräsentiert und behandelt werden. • Im Binärsystem wird Mantisse (auch significand genannt) typischerweise auf 1<=f<=2 beschränkt. • Somit liegt das Ergebnis von Addition und Multiplikation einzelner Mantissen immer zwischen 2 und 4 und die Renormierung kann durch einen Shift implementiert werden. • Werden zwei 32 Bit Register zur Repräsentation herangezogen und Binärpunkt rechts von Bit 29 angesetzt, ergeben sich folgende Beispiele: 1.5 3 9 24.1.00 - 4 .word .word .word 0x30000000, 0x0 0x30000000, 0x1 0x24000000, 0x3 37-023 Systemprogrammierung © Stricker IEEE Floating Point Format • Bei floating point Repräsentationen können viele Parameter, wie z.B. Anzahl der Bits von Mantisse und Exponent, Rundung etc. individuell gewählt werden. • Führt zu einer Hardwareabhängigkeit bei der Implementierung von Numerik-Software • Daher Floating Point Repräsentation innerhalb IEEE 754-1985 (IEC 559) als internationaler Standard verfasst und von fast allen Herstellern übernommen. Wesentliche Merkmale von IEEE 754: • Verschiedene Modi zur Rundung von Ergebnissen • Beinhaltet Sonderzeichen für NaN, ∞ und - ∞ • Verwendet denormal numbers zur Repräsentation von Zahlen, die kleiner als 1.0x2Eminsind. • Rundung von Zwischenwerten IMMER auf EVEN 24.1.00 - 5 37-023 Systemprogrammierung © Stricker Rundung • IEEE 754 hat insgesamt 4 Rundungsmodi: • Rundung nach NEAREST, 0, - ∞ , ∞ • Bei Zahlen, welche genau zwischen zwei möglichenWerten liegen, wird immer auf die Zahl gerundet, deren LS Digit EVEN ist. • Beispiel im Dezimalsystem: 3.05 wird auf 3.0 gerundet Sonderzeichen und Denormals • Wesentliches Merkmal des Standards ist, dass bei Exeptions (Null-Division, Wurzel aus negativer Zahl) die Berechnung weitergeführt werden kann. • Dazu wird in diesen Fällen ein Sonderzeichen, NaN (Not a Number) zurückgegeben sowie Exeption flags gesetzt. • In der IEEE Arithmetik wird NaN als Argument akzeptiert, wobei jede Operation auf NaN wiederum NaN zurückliefert (3 + NaN =NaN) 24.1.00 - 6 37-023 Systemprogrammierung © Stricker • Nur sehr wenig Sonderbehandlungen in mathematischen Routinen nötig • Z.B. arctan(sqrt((1-x)/(1+x))) liefert NaN, wenn x=NaN • sqrt(-1)=NaN • 1/0= ∞ sowie 1/ ∞ =0 oder arctan( ∞ ) =Pi/2 • Denormalized numbers verlieren graduell an Signifikanz Beispiel im Dezimalsystem: x = 1.234 *10Emin • x/10 = 0.123 *10Emin, somit Verlust einer Stelle an Genaugkeit • x/100 = 0.012 *10Emin usw. bis schliesslich die 0 durch Rundung erreicht wird • Dadurch Erhöhung der Genauigkeit bei Berechnungen 24.1.00 - 7 37-023 Systemprogrammierung © Stricker Repräsentation von fp-Zahlen • Insgesamt 3 Formate definiert: single, double und quad (extended double) • Single fp-Format wie folgt definiert: • Bit 31 ist Sign Bit • Bits 23-30 beinhalten den Exponenten e, welcher um 0x3f = 127 verschoben (biased) und somit immer positiv ist. • Bits 0 - 22 enthalten die Stellen hinter dem Komma der Mantisse, da diese immer mit 1. beginnt. • Somit folgende Darstellung: s e – 127 N = ( – 1 ) × 1. f × 2 24.1.00 - 8 37-023 Systemprogrammierung (0.2) © Stricker • Bsp: für Zahlen im IEEE 754 fp-single Format: • Format Parameter für IEEE 754 fp-Standard: 24.1.00 - 9 37-023 Systemprogrammierung © Stricker • Repräsentation von Sonderzeichen: • Biased Exponenten von 0 und 255 werden zur Darstellung der Sonderzeichen verwendet • NaN wird durch f!=0 sowie e=255 dargestellt. Somit keine Eindeutigkeit. • 0 ist aufgrund führender 1 ebenfalls als Sonderzeichen implementiert. • Vorteile von biased Exponenten beim Vergleicher zweier Zahlen, der mittels Integer Operatoren implementiert werden kann. Ferner 0 durch 0x00000000 abgedildet 24.1.00 - 10 37-023 Systemprogrammierung © Stricker FP-Multiplikation • Gegeben die Operanden als x = s*2e • Folgt für die Multiplikation: e1 e2 e1 + e2 s × 2 × s × 2 = (s × s ) × 2 1 2 1 1 (0.3) • Zur Mult. können gewöhnliche unsigned Integer Operatoren herangezogen werden • Resultat s1 x s2 ist jeodch i.A. 2p Bits lang und muss wieder auf p Bits gerundet werden (p=24 bei single) • Exponent durch Addition berechenbar, wobei jedoch der bias 0x3f subtrahiert werden muss • Beispiel -1*23 *1*24: 1 10000010 000..... 0 10000011 000..... Produkt der Mantissen bleibt bei 1.0 Berechne Exponent als e1 + e2 - bias: 10000010 10000011 10000001 10000110 = 134 (7+127) 24.1.00 - 11 37-023 Systemprogrammierung © Stricker • Rundungsoperationen müssen korrekt durchgeführt werden. • Verschiedene Fälle: Beispiel p=3 im Dezimalsystem 24.1.00 - 12 37-023 Systemprogrammierung © Stricker FP-Addition • Allgemein wandelt eine arithmetische fp-Operation p-Bit lange Operanden in ein p-Bit langes Ergebnis um. • Idealerweise zunächst korrekte Berechnung, wie bei Multiplikation, mit anschliessender Rundung. • Nachteil: Längere Register notwendig, mehr Aufwand. • Addition kann hierbei optimiert werden: • Man beachte Addition zweier 6 Bit Zahlen, z. B. 1.10011 und 1.10001x2-5 //ideal// 1.10011 0.0000110001 // bei 6 Bit Addierer // 1.10011 0.00001 1.10100 24.1.00 - 13 37-023 Systemprogrammierung © Stricker • 8-stufiger Algorithmus zur Addition zweier Zahlen a1 und a2. Mantissen s1 und s2 sowie Exponenten e1 und e2 seien bereits decodiert 1. Wenn e1<e2 ->vertausche Operanden, so dass immer >0 2. Wenn sign1 != sign2 ersetze s2 durch Zweierkomplement 3. s2 in p-Bit Register laden und um d=e2-e1 Bits nach rechts schieben. Falls Zweierkomplement -> 1-shift. Speichere g als MSB, r als next MSB sowie s als OR der restlichen ausgeschobenen Bits. 4. Berechne eine vorläufige Mantisse S=s1+s2. Wenn sign1 !=sign2 UND MSB(S)=1 UND kein carry out, dann S<0 daher S->Zweierkomplement 5. Shift von S: Wenn sign1=sign2 UND carry out in 4) ->S um 1 Bit nach rechts sowie auffüllen des MSB von S mit 1. Andernfalls Linksshift bis normiert, wobei das g Bit mit berücksichtigt werden muss (g000000..). Exponent angleichen! 6. Neuberechnung von r und s: Wenn Rechtsshift in 5) >r:=LSB(S) vor shift. Wenn kein shift in 5) -> r:=g, s:=rORs. Wenn Linksshift um 1 Bit ->r und s bleiben unverändert. Wenn zwei oder mehr Linksshifts ->r:=0, s:=0. 7. Rundung von S gemäss Tabelle. Bei Eintrag inkrementieren. Wenn carry out bei Rundung -> Rechtsshift von S sowie Exponent anpassen. 24.1.00 - 14 37-023 Systemprogrammierung © Stricker 8. Berechnung des Vorzeichens des Ergebnisses: wenn sign1=sign2 -> Ergebnis. Andernfalls wird gemäss Tabelle verfahren. 24.1.00 - 15 37-023 Systemprogrammierung © Stricker FP-Division • Methode 1: führt fpdiv auf Int-Division zurück e e e –e s × 2 1 / s × 2 1 = ( s / s ) × 2 1 2 1 2 1 1 (0.4) • Int. Divisionsalgorithmus wird verwendet • Methode 2: ein iterativer Divisionsalgorithmus, welcher auf der Newton-Methode beruht. • Gegeben sei die Funktion f(x) = x-1 - b • Mit f‘(x) = -1/x2erhält man die folgende Rekursion zur Berechnung von 1/b aus b: xi + 1 = xi ( 2 – xi b ) (0.5) • Hieraus resultiert folgender Algorithmus zur Berechnung von a/b: 1. Skaliere b, so dass 1<=b<=2 2. Wähle Initialwert von 1/b=x0 aus lookup table 3. Iteriere gemäss obiger Gleichung bis xn eine Genauigkeitsschranke überschreitet 4. Berechne a*xn und kehre Skalierung um • Vorteil der Iteration: FP-Co-Prozessoren müssen keine Divisionshardware implementieren. Weiterhin Verdopplung der Resultatziffern in jedem Schritt • Nachteil: Rundungsprobleme von a/b, selbst wenn 1/b korrekt gerundet. Iteration produziert keinen Remainder und kann somit nicht für Integer Division herangezogen werden • TI 8847 verwendet iterative Division in verbesserter Form 24.1.00 - 17 37-023 Systemprogrammierung © Stricker FP-Exeptions nach IEEE 754 • Standard unterstützt insgesamt 5 exeptions: underflow, overflow, divide by zero, inexact, invalid • Werden durch individuelle Flags gekennzeichnet • Können durch einen trap handler des Systems entsprechend behandelt werden • Beispiel für invalid: sqrt(-1), 0/0 -> NaN • inexact Exeption wird bei Rundung und overflow aufgerufen. Da sie häufig vorkommen kann, beeinträchtigt Aufruf des trap handlers die Performanz • underflow wird ebenfalls gesondert behandelt und bei unexakten Ergebnissen signalisiert. 24.1.00 - 18 37-023 Systemprogrammierung © Stricker Der FP Unit der SPARC • FPU für arithmetische Ops auf Real-Variablen • 32 fp-Register %f0-%f31 • Keine Register Windows für die fp-Register • Elementare Load/Store Instruktionen: ldf stf lade Wort in fp-Register speichere fp-Register auf Adresse • Single floating point Instruktionen, wie z. B. • Konversion von fp nach Integer und umgekehrt • fp-Vergleichs-Operation fcmps zum Setzen der condition codes E,L,G,U 24.1.00 - 19 37-023 Systemprogrammierung © Stricker • Double Precision 64bit fp-Operationen basieren auf einer doubleword float Definition mit 52 Bits Mantisse und 11 Bits Exponent • Ferner gibt es noch 80bit floats und quad floats • 64bit weerden typischerweise von HW unterstützt 24.1.00 - 20 37-023 Systemprogrammierung © Stricker