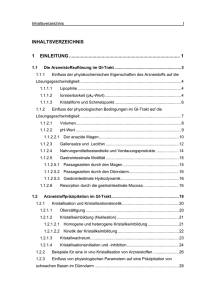

Folien der Verteidigung

Werbung

Verteidigung der Studienarbeit Charakterisierung und Modellierung von Analogschaltungen 27.03.2006 A. Plänitz 1 Charakterisierung und Modellierung von Analogschaltungen Gliederung des Vortrags 1. Technischer Hintergrund » » » Motivation Charakterisierung Schaltungsmodellierung 2. Operationsverstärker » » Charakterisierung Modellierung 3. Softwareentwurf » » » Analyse Entwurf Vorstellung 4. Zusammenfassung 27.03.2006 A. Plänitz 2 1. Technischer Hintergrund – Motivation Motivation Stand der Technik » kleinere Strukturbreiten » höhere Integrationsdichten » steigende Komplexität Werkzeuge zur Unterstützung » Steigerung der Produktivität » Reduzierung anfallender Kosten » Automatisierung, Verifikation Ziel der Arbeit » » 27.03.2006 automatisierter Vergleich von Entwurfsvarianten durch Charakterisierung Generierung von Verhaltensmodellen zur Verifikation von Gesamtsystemen A. Plänitz Abbildung 1 – allgemeiner Schaltungsentwurfsprozess 3 1. Technischer Hintergrund – Charakterisierung Charakterisierung Ziel » Bestimmung charakteristischer Kennwerte Messschaltung » Erregung des DUT » Betriebsparameter » Generierung von Kennlinien durch Simulation Extraktionsgleichungen » Berechnung der Modellparameter aus Simulationskennlinien » Extraktionsparameter Abbildung 3 – DUT mit Testbench 27.03.2006 A. Plänitz 4 1. Technischer Hintergrund – Schaltungsmodellierung Schaltungsmodellierung Ziele der Modellierung » Simulation und Verifikation in akzeptabler Zeit » Top-Down-Entwurfspfad kann konsequent durchgeführt werden » Wiederverwendung und Verkauf von Schaltungskomponenten Eingangsstufe gewünschte Modelleigenschaften » schnell in der Simulation » einfache Struktur » Vernachlässigung unwichtiger Effekte » hohe Übereinstimmung mit Original Parametrisierbare Verhaltensmodelle Übertragungsstufe Ausgangsstufe Abbildung 2 – Aufbau parametrisierbarer Modelle 27.03.2006 A. Plänitz 5 2. Operationsverstärker – Charakterisierung Bestimmung der Ausgangsimpedanz Ziel » Bestimmung der Kenngrößen R out und Cout Extraktion » Yout Iout 1 ReYout j Im Yout j 2f Cout Uout R out Abbildung 4 – Ersatzschaltung » R out 1 Iout (f m ) Uout (f m ) Re Iout (f m ) 1 C Im » out 2f m Uout (f m ) Abbildung 5 – Messschaltung 27.03.2006 A. Plänitz 6 2. Operationsverstärker – Modellierung Modellierung Eingangsstufe: U os , CMRR, PSRR, CinGnd , CinDiff » Übertragungsstufe: UoutMax , U outMin , f o , Vd0 , SR » Ausgangsstufe: R out , Cout Modellparameter » Modell Abbildung 6 – Modell des OPV 27.03.2006 A. Plänitz 7 3. Softwareentwurf – Analyse Idee Abbildung 7 – prinzipielle Funktionsweise des Werkzeuges 27.03.2006 A. Plänitz 8 3. Softwareentwurf – Analyse Anforderungen Vergleich » CADENCE: Virtuoso Characterization & Modeling Environment (VCME ) » MENTOR GRAPHICS: ADVanced Design ToolBox 27.03.2006 Ziel » umfangreiche und einfache Möglichkeiten zur Erweiterung von Testbenches und Modellen » übersichtliche, flexible Programmstruktur für Funktionserweiterungen A. Plänitz 9 3. Softwareentwurf – Entwurf Entwurfsmuster Entwurfsmuster » Kapselung durch Objektschnittstellen » helfen bei Definition der Schnittstellen MVC-Entwurfsmuster » strikte Trennung von Daten, Dialogaufbau und Dialogverhalten Abbildung 8 – MVC – Model-View-Controller 27.03.2006 A. Plänitz 10 3. Softwareentwurf – Entwurf Simulatoranbindung Entwurfsmuster Schablonenmethode » Einfache Erweitung externer Werkzeuge möglich Entwurfsmuster Singleton » Sicherung von Zugriffsrechten auf die externen Werkzeuge Abbildung 9 – Klassendiagramm Simulatoranbindung 27.03.2006 A. Plänitz 11 3. Softwareentwurf – Vorstellung Charakterisierungsumgebung besondere Merkmale » » » » Intuitive Bedienung Keine Kenntnisse über Skript- oder Hardwarebeschreibungssprachen notwendig Simulation und Extraktion auf Knopfdruck Darstellung und Auswertung der Ergebnisse möglich Abbildung 10 – Bildschirmfoto Charakterisierungsumgebung 27.03.2006 A. Plänitz 12 3. Softwareentwurf – Vorstellung Anlegen einer Testbench » » » Einfache Erweitung der Testbenchbibliothek möglich Keine Einschränkung in der Beschreibung von Schaltungsaufbau, Simulatorsteuerung und Extraktionsgleichungen Kenntnisse in entsprechenden Sprachen nötig # Extraktion der Leerlaufverstärkung GAINdB = yval( WDBVd, 10 ) # Bestimmung der oberen Grenzfrequenz I3dB = yval ( WDBVd, 10 ) - 3 F3dB = xdown( WDBVd, I3dB ) # Bestimmung der Transitfrequenz Ft = xdown(WDBVd,1) Abbildung 11 – Extraktionsgleichungen 27.03.2006 A. Plänitz ** Einbinden des DUT ** YDUT DUT PORT: 0 nvbias nvdd ninp1 ninp2 noutp ** SCHALTUNG ** * Versorgungsspannungen Vdd nvdd Vbias nvbias * Eingangsspannungen Vin ninp1 Vcm ninp2 * Ausgangsgrößen Rload noutp Vref n6 ** GLOBALE PARAMETER .param Uoffset = .param Uin = .param Ucm = .param Uref = .param Udd = .param Ubias = .param Rload = 0 0 Udd Ubias ninp2 0 DC Uoffset AC Uin Ucm n6 0 Rload Uref MIT DEFAULT-WERTEN** 0V 1V 0.108V 0.107V 5V 3.7V 1e12 ** ANALYSE ** .dc .ac dec 20 1 1e20 ** AUSGABE ** .defwave Vd=V(noutp,n6)/V(ninp1,ninp2) .probe ac WDB(Vd) .end Abbildung 12 – Aufbau der Messschaltung 13 3. Softwareentwurf – Vorstellung Anlegen einer Testbench im Werkzeug Möglichkeiten » » Beliebiges Editieren von Modellen und Testbenches Copy&Paste Abbildung 13 – Bildschirmfoto Testbench bearbeiten 27.03.2006 A. Plänitz 14 3. Softwareentwurf – Vorstellung Verwaltung der Testbenches Abbildung 13 – Bildschirmfoto Testbenchverwaltung 27.03.2006 A. Plänitz Abbildung 14 – Bildschirmfoto Eigenschaften einer Testbench 15 4. Zusammenfassung Zusammenfassung Operationsverstärker » » Charakterisierung Modellierung Werkzeug-Entwurf » Automatisierung der Charakterisierung » Parametrisierung einer Modellschaltung aus den Kennwerten » Vergleich Modell und Originalschaltung » Anbindung eines Simulators » Bereitstellung einer Modell- und Testbenchbibliothek » einfache Erweiterung der Modell- und Testbenchbibliothek möglich weitere Aufgabengebiete » » 27.03.2006 Funktionserweiterung Untersuchung weiterer Modellierungsmethoden A. Plänitz 16