Versuch 3: Halbleiterbauelemente im Schaltbetrieb

Werbung

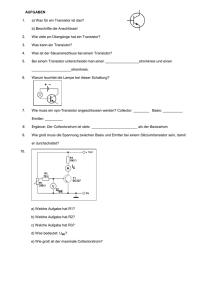

Labor Elektronische Schaltungen Prof. Dr. P. Stuwe Dipl.-Ing. A. Hoppe Versuch 3: Halbleiterbauelemente im Schaltbetrieb Gruppennr. Name: ……………………………….……… Matr.-Nr.: …….…………… Name: …………………………….…………. Matr.-Nr.: ………….……… ………….. Datum Vortestat Note / Bemerkung ………….. ………….. ………………………………………………………………….. 1 Theorie Bipolare Transistoren und Feldeffekttransistoren lassen sich sowohl zum Verstärken von Klein- und Großsignalen als auch zum kontaktlosen, schnellen Schalten kleiner und mittlerer Leistungen verwenden. Die Vorteile des FETs gegenüber dem bipolaren Transistor sind die kürzeren Schaltzeiten und die nahezu leistungslose Steuerung. Mit bipolaren Transistoren lassen sich dagegen geringere Restspannungen über der Schaltstrecke (pn-Übergang) erzielen. Speziell für Schalteranwendungen wurde daher der IGBT (Insulated Gate Bipolar Transistor) entwickelt, in dem ein bipolarer Transistor und ein FET kombiniert sind. Diese Transistorkombination wird wie ein FET angesteuert und verhält sich ausgangsseitig wie ein Bipolarer Transistor. Des Weiteren sind Transistoren die Grundbausteine der digitalen Schaltungstechnik, wo zur Realisierung von logischen Verknüpfungen, Flip-Flops, Speicherzellen etc. eine Vielzahl von Transistoren und Widerständen auf einem Substrat (IC) integriert sind. Für Anwendungen im Wechselspannungsbereich bei großer Leistung finden bevorzugt Thyristoren und TRIACs (Triode Alternating Current Switch) und gelegentlich GTOs (Gate Turn Off Thyristoren) Verwendung. Diese Bauteile werden nicht wie die Transistoren über Strom oder Spannung gesteuert, sondern werden mit Impulsen gezündet und löschen sich unter bestimmten Bedingungen selbst (der GTO kann auch mit einem Impuls gelöscht werden). 1.1 Bipolarer Transistor als Schalter in Emitterschaltung Bei Verwendung des bipolaren (npn-) Transistors als Schalter ist sowohl der statische Betrieb in den beiden Schaltzuständen EIN und AUS als auch der dynamische Übergang zwischen diesen Punkten von Interesse. Im Schaltzustand AUS wird der Transistor im Sperrzustand betrieben (s. Abb 1: Punkt 2 im Ausgangskennlinienfeld der Emitterschaltung). Es fließt nur ein sehr kleiner Kollektor-Emitter-Reststrom, welcher durch Anlegen einer Sperrspannung an die Basis-Emitter-Strecke noch verringert werden kann (s. Abb. 1: Punkt 1). Die max. Kollektor-Emitter-Sperrspannung UCEmax darf allerdings nicht überschritten werden. Im Schaltzustand EIN wird der Transistor in einem möglichst niederohmigen Durchlasszustand betrieben. Die korrekte Bemessung des Basisstromes IB ist dabei von Bedeutung. Wählt man den Basisstrom zu gering, so wird der Transistor nicht vollständig durchgesteuert und über V 1.7 28.09.2010 Ostfalia Fakultät Elektrotechnik Labor Elektronische Schaltungen der Kollektor-Emitter-Strecke fällt eine unerwünscht große Spannung ab, was auch zur Folge hat, dass eine unnötig große Verlustleistung PV ≈ UCE · IC umgesetzt wird. I UCB = 0 C IC m ax Ptot 5 4 3 RC 2 U 1 CE max U CE Abb. 1 : Arbeitspunkte des bipolaren Transistors als Schalter Im Kennlinienfeld (Abb. 1) ist dieser Fall als Punkt 3 eingezeichnet. Durch einen höheren Basisstrom erzielt man eine Verringerung von UCE. Im Punkt 4 (Abb 1) ist bei IB0 die Kollektor-Basis-Spannung auf UCE = 0 V abgesunken. Eine weitere Erhöhung von IB auf einen Wert IBx > IB0 führt zur so genannten Übersteuerung des Transistors (Betrieb im Bereich der Sättigung). Die Kollektor-Emitterspannung sinkt dabei bis auf die KollektorEmitter-Sättigungsspannung UCEsat im Arbeitspunkt ab (s. Abb. 1: Punkt 5). Das Verhältnis I zwischen IBx und IB0 wird als Übersteuerungsfaktor ü bezeichnet: ü Bx I B0 Das dynamische Verhalten des Transistors ist beim Schalten zwischen den Punkten 1↔4 und 1↔5 (oder 2↔4 und 2↔5) sehr unterschiedlich. Die Schaltzeiten sind wie folgt definiert (s. Abb. 2): Verzögerungszeit td (delay time): Zeit vom Einschalten des konstanten Steuerstromes IB bis zum Erreichen des 10%-Wertes des max. Kollektorstromes. Anstiegszeit tr (rise time): Zeit vom 10%-Wert bis zum Erreichen des 90%-Wertes des max. Kollektorstromes Speicherzeit ts (storage time): Zeit nach dem Abschalten des Steuerstromes bis zum Erreichen des 90%-Wertes des max. Kollektrstromes. Abfallzeit tf (fall time): Zeit vom 90%-Wert bis zum Erreichen des 10%-Wertes des max. Kollektorstromes. Die Einschaltzeit tein ist die Summe aus Verzögerungszeit td und Anstiegszeit tr. Die Ausschaltzeit taus. ist die Summe aus Speicherzeit ts und Abfallzeit tf ergibt die 2 Ostfalia Fakultät Elektrotechnik Labor Elektronische Schaltungen IB t IC 100% 90% 10% td tr ts t ein tf t t Abb. 2 : Schaltzeiten (bipolarer Transistor) I. A. sind bei Schalteranwendungen steile Schaltflanken (tr und tf möglichst kurz) und eine kurze Speicherzeit ts erwünscht. Je steiler die Schaltflanken verlaufen, desto geringer ist die Verlustleistung. Abb. 3 zeigt jeweils die qualitativen Verläufe des Kollektorstromes, der Kollektor-EmitterSpannung und der Verlustleistung bei unterschiedlich steilen Schaltflanken. Der Spitzenwert der Verlustleistung kann durchaus größer sein als die maximale Verlustleistung Ptot des Transistors. Die von der Schaltfrequenz abhängige mittlere Verlustleistung muss aber in jedem Fall geringer sein als Ptot. In Hinsicht auf die max. Schaltfrequenz und möglichst unverfälschtes Puls-Pausen-Verhältnis ist die Speicherzeit zu minimieren. P p V t i I,U uCE AUS EIN AUS t Abb. 3 : Abhängigkeit der Verlustleistung P vom Verlauf der Schaltflanken Eine kurze Speicherzeit erreicht man bei Betrieb an der Grenze zur Sättigung (Punkte 1↔4) und durch Anlegen einer Sperrspannung an die Basis-Emitter-Strecke (die maximal zulässige Sperrspannung UBE0 ist allerdings relativ gering). Die zuletzt genannte Maßnahme führt zusätzlich zu einer leichten Verringerung der Abfallzeit tf. 3 Ostfalia Fakultät Elektrotechnik Labor Elektronische Schaltungen Eine Verkürzung der Anstiegszeit tr bzw. Versteilerung der Schaltflanke kann man durch eine Erhöhung des Basisstromes erreichen (Betrieb in der Sättigung, z. B. Punkte 1↔5). In Abhängigkeit vom Übersteuerungsfaktor ü vergrößert sich allerdings beim Ausschalten aus der Sättigung wiederum die Speicherzeit ts und damit die Ausschaltzeit taus. Mit der in Abb. 4 gezeigten Beschaltung sind sehr kurze Schaltzeiten erreichbar. Der zusätzliche Kondensator C ist im Einschaltmoment niederohmig und überbrückt so RV, es fließt also kurzzeitig ein sehr großer Strom und tr ist entsprechend klein (Punkt 5). Nachdem der Kondensator RL geladen ist, fließt über den C Widerstand RV ein Strom, der so bemessen ist, dass der Transistor in RV Ri leichter Sättigung betrieben wird (in der Nähe von Punkt 4). Aufgrund dessen ist die Speicherzeit schon relativ kurz. Durch die Ansteuerung us 0V der Basis mit negativem Pegel in Verbindung mit dem Kondensator (großer Strom im Schaltmoment) erfolgt noch zusätzlich eine Abb. 4: Schaltung zur Erzielung kurzer Schaltzeiten Verringerung von ts und tf. 1.2 Feldeffekttransistor als Schalter in Sourceschaltung Für Schalteranwendungen werden vorwiegend selbst sperrende MOSFET-Typen verwendet. Im Schaltzustand AUS fließt bei UGS = 0 nur ein sehr kleiner Drain-Source-Reststrom im µABereich, welcher durch Verringerung der Steuerspannung UGS noch verringert werden kann (n-Kanal-Typ, Punkt 1 bzw. 2 im Ausgangskennlinienfeld der Sourceschaltung). Im Schaltzustand EIN wird der FET in einem niederohmigen Durchlasszustand betrieben (z.B. Punkt 3). Je größer die Steuerspannung ist (Punkt 3→4), desto geringer wird der DrainSource-Widerstand RDS und damit die Drain-Source-Spannung UDS und die Verlustleistung PV ≈UDS · ID. Die Ein- und Ausschaltzeiten des FET sind gegenüber dem bipolaren Transistor kürzer, da keine pn-Übergänge vorhanden sind. Allerdings hängen sie im stärkerem Maße von der Beschaltung des FET ab: Der Eingangskreis des FET entspricht einer RCKombination, die aus dem Generatorinnenwiderstand Ri und der Gate-Source-Kapazität CGS (C11S) besteht und im Wesentlichen die Einschaltzeit tON I D (10% → 90% von ID) bestimmt. Die I D max Ausschaltzeit tOFF (90% → 10 von ID UGSmax ) wird sowohl durch die eingangsPtot seitige Beschaltung als auch durch 4 3 die des Ausgangskreises bestimmt. Der Ausgangskreis entspricht ebenfalls einer RC-Kombination, die aus der Drain-Source-Kapazität CDS (C22S) und dem Lastwiderstand RL 2 besteht. U DS 1 max Die Einschaltverzögerungszeit td(ON) und die Ausschaltverzögerungzeit U DS Abb. 5 : Arbeitspunkte des FETs als Schalter 4 Ostfalia Fakultät Elektrotechnik Labor Elektronische Schaltungen td(OFF) fallen gegenüber dem bipolarem Transistor ebenfalls kürzer aus. Anstatt tON und tOFF wird auch wie beim bipolaren Transistor tr bzw. tf verwendet. UQ UGS t ID t 100% 90% 10% td(ON) tON td(OFF) toff t Die Betrachtungen zur Verlustleistung unter 1.1 gelten natürlich auch für den FET. Der Anteil der während der Schaltvorgänge umgesetzten Verlustleistung an der mittleren Verlustleistung fällt aber aufgrund der kürzeren Schaltzeiten geringer aus als beim bipolaren Transistor. Dafür ist i. A. die Verlustleistung im EIN-Zustand höher, da der minimale Widerstand der Drain-Source-Strecke größer ist als bei einem bipolaren Transistor. Abb. 6 : Schaltzeiten (FET) 1.3 Power MOS-FET Bei den sogenannten Power MOS-FETs (z.B. SIPMOS: Siemens Power MOSFET) wird eine Verringerung des Widerstands der Drain-Source-Strecke durch parallel schalten vieler tausend FETs auf einem einzigen Chip erreicht. Gegenüber den „normalen“ FETs erhält man dadurch allerdings größere Drain-Source- und Gate-Source-Kapazitäten. SIPMOS-FETs und entsprechende Varianten anderer Hersteller werden vorwiegend im Bereich großer (Schalt-) Leistungen verwendet. Die maximale Steuerspannung UGSmax darf nicht überschritten werden. 1.4 Insulated Gate Bipolar Transistor IGBT Ein IGBT besteht aus einer Kombination von FET und bipolarem Transistor. Der IGBT lässt sich aufgrund der FET-Eingangsstufe nahezu leistungslos steuern. Über den FET wird der bipolare Transistor angesteuert, dessen Vorteil gegenüber einem FET die geringe Restspannung UCEsat ist. Die C C Diode V1 ermöglicht einen hohen negativen Basisstrom im Ausschaltmoment und damit V2 eine geringe Ausschaltzeit taus. G Der Widerstand R bewirkt einen G geringen Kollektor-EmitterReststrom. Die Freilaufdiode V2 (nicht bei allen IGBT integriert) V1 R schützt vor einer zu hohen E E negativen Kollektor-EmitterAbb. 7 : Aufbau und Schaltzeichen eines IGBT Spannung, wie sie beim Schalten induktiver Lasten auftreten kann. 5 Ostfalia Fakultät Elektrotechnik Labor Elektronische Schaltungen 1.5 Schalten von Lasten mit kapazitiven oder induktiven Anteilen IC I C max Ptot U CE max U CE Werden Lasten mit kapazitiven oder induktiven Anteilen geschaltet, so ist die Verbindungslinie zwischen beiden - den Schaltzuständen EIN und AUS entsprechenden - Arbeitspunkten im Kennlinienfeld keine Gerade. Beim Schalten von Lasten mit kapazitiven Anteilen ergeben sich Verläufe wie sie in Abb. 8 exemplarisch für den bipolaren npn-Transistor dargestellt sind. Je geringer der kapazitive Anteil ist, desto mehr nähern sich die Verbindungslinien einer Geraden an. Während des Einschaltvorganges können sehr viel größere Verlustleistungen auftreten als beim Schalten reiner Wirklasten. Abb. 8 : Schalten von kapazitiven Lasten Werden Lasten mit induktiven Anteilen geschaltet, so ergeben sich Verläufe gemäß Abb. 9 (bipolarer I C max npn-Transistor). Auch in diesem Fall ähneln die Verbindungslinien umso Ptot eher einer Geraden, je geringer der induktive Anteil der Last ist. Größere Verlustleistungen gegenüber dem Schalten von Wirklast ergeben sich während des Ausschaltvorganges. Bei sehr großem induktiven Anteil kann die Spannung über dem Transistor beim Ausschalten sogar kurzzeitig über dem Wert im Schaltzustand AUS liegen. Zur dieser überhöhten U CE Vermeidung Spannungen werden Lasten mit induktiven Anteilen mit sogenannten Abb. 9 : Schalten von induktiven Lasten Freilaufdioden ausgestattet. Diese Dioden werden parallel zu der Last (z. B. auch Relais) geschaltet und schließen die beim Abschalten auftretenden (der Betriebsspannung entgegengerichteten) Spannungsspitzen kurz. IC U CE max 6 Ostfalia Fakultät Elektrotechnik Labor Elektronische Schaltungen 2 Versuchsdurchführung Benötigte Geräte: Funktionsgenerator HM 8030-5 Oszilloskop HM1507-3 Versuchsaufbau mit bipolarem Transistor, Vor- und Lastwiderständen und Kondensator Versuchsaufbau mit FET, ohmscher und induktiver Last und Diode Labornetzgerät 0 - 30 V / 3 A Spannungsversorgung HP E3630A 2.1 Bipolarer Transistor als Schalter, Messung der Schaltzeiten Ziel dieses Versuchsteils ist es die Schaltzeiten und die Sättigungsspannung eines bipolaren npn-Transistors in Abhängigkeit von der Ansteuerung bzw. seines EIN-Arbeitspunktes zu messen. Schaltung 1: Der Transistor wird im EIN-Zustand an der Grenze zur Sättigung betrieben. IB 10 mA Schaltung 2: Der Transistor im EIN-Zustand wird in leichter Sättigung betrieben. IB 20 mA, ü 2 Schaltung 3: Der Transistor wird im EIN-Zustand in starker Sättigung betrieben. IB 100 mA, ü 10 Schaltung 4: Betrieb mit Beschleunigungskondensator. IB 20 mA, ü 2 Der Kollektorstrom beträgt im EIN-Zustand jeweils ca. 1 A. Die jeweilige Schaltung ist über einen Schalter auf dem Versuchsaufbau auszuwählen (Schaltung 1 : Linksanschlag). Arbeiten Sie bei Schaltung 1 bis 3 eingangsseitig mit einer rechteckförmigen Wechselspannung mit f = 100 kHz, USS = 5 V und einem Gleichspannungsoffset von U= = 2,5 V. Bei Schaltung 4 verwenden Sie eine rechteckförmige Wechselspannung mit f = 100 kHz, USS = 7 V und U= = 1,5 V. Vermeiden Sie bei der Einstellung dieser Spannungen eine zu hohe Basis-Emitter-Sperrspannung. Sie darf für den Transistor maximal UEB0 = 5 V betragen. Die Betriebsspannung beträgt UB = 10 V. Messen Sie jeweils t d , t r , t s , t f und die Kollektor-Emitter-Restspannung U CE . Stellen Sie dazu das Steuersignal (Ausgangssignal des Funktionsgenerators) und die Spannung über der Schaltstrecke ( U CE ) auf dem Oszilloskop dar. Um eine Darstellung gemäß Abb. 2 zu erhalten, muss U CE invertiert werden. Zur Bestimmung der Schaltzeiten werden die 0%-, 10%-, 90%und 100% -Markierungen des Oszilloskop-Bildschirmes benutzt, an denen das Ausgangssignal ausgerichtet wird. Die Zeiten können unter Verwendung der Cursor des Oszilloskopes gemessen werden. Bei der Spannungsmessung empfiehlt es sich die Frequenz auf 10 kHz zu reduzieren. 7 Ostfalia Fakultät Elektrotechnik Labor Elektronische Schaltungen +U B +U B 10 10 BSX 62-10 BSX 62-10 430 210 56 62 Schaltung 2 Schaltung 1 +U B +U B 10 10 500pF BSX 62-10 BSX 62-10 39 174 39 62 Schaltung 3 Schaltung 4 Generatorinnenwiderstand: 50 Abb. 10 : Schaltungen zur Messung der Schaltzeiten 2.2 MOS-FET als Schalter In diesem Versuchsteil soll ein praktischer Vergleich zwischen dem Schalten ohmscher und induktiver Lasten stattfinden. Der Versuchsaufbau ist mit UB = 10 V zu versorgen. Steuern Sie den FET mit einer sinusförmigen Spannung mit USS = 8 V und einer Frequenz von f = 30 Hz an (Signal am Gate mittels Oszilloskop überprüfen!). Der Offset am Funktionsgenerator muss ausgeschaltet sein. Der Strom wird über den 1 - Widerstand gemessen. Stellen Sie für die folgenden Fälle den Drainstrom I D über der Drain-Source-Spannung U DS auf dem Oszilloskop dar (X-Y-Betrieb, Speichermodus, Abtastrate 40 KS/s) und drucken Sie jeweils das Ergebnis aus: 1. Ohmscher Lastwiderstand 2. Induktivität mit einem ohmschen Widerstand in Reihe 3. wie unter 2. aber mit Freilaufdiode Stellen Sie unter Punkt 2 zusätzlich zunächst Steuersignal U GS u. U DS und anschließend U DS und den Drainstrom I D und im Y(t)-Betrieb dar. Drucken Sie die Verläufe von U GS , I D , U DS aus und stellen Sie sie in der Auswertung untereinander (mit gleichem Zeitbezug) dar. 8 Ostfalia Fakultät Elektrotechnik Labor Elektronische Schaltungen Labor für elektronische Schaltungen Freilaufdiode D L BUK455 S G 100 k GND +UB Abb. 11 : Versuchsaufbau Auswertung: Zu 2.1: Stellen Sie die Ergebnisse (td, tr, ts, tf, tein, taus, UCE) graphisch dar und führen Sie eine kurze Diskussion. Zu 2.2: Zeichnen Sie in die Darstellungen von Punkt 1 und 2 jeweils eine Verlustleistungshyperbel für Ptot = 2 W ein. Halten Sie einen Transistor mit einer solchen max. Verlustleistung bei diesen Anwendungen für gefährdet? (Begründung) Stellen Sie für die Darstellung von Punkt 2 die im Transistor umgesetzte Verlustleistung über der Spannung UDS dar und bestimmen Sie die maximale und minimale auftretende Leistung. Markieren Sie auch die Schaltzustände EIN und AUS. Welchen Einfluss bezüglich der max. und der mittleren Verlustleistung hat die Diode? Das Ergebnis ist zu diskutieren. Ab welcher Steuerspannung UP geht der FET in den leitenden Zustand über? (siehe Darstellung von UGS, ID, , UDS) Literatur: [1] P. Stuwe: Umdruck zur Vorlesung Elektronische Schaltungen [2] U. Tietze, Ch. Schenk: Halbleiter-Schaltungstechnik, 12. Aufl., Springer, 2002 9