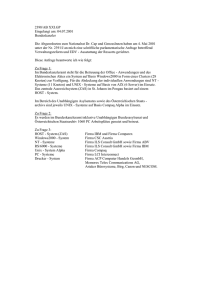

Diplomarbeit Axel Schneider

Werbung