Digitale Elektronik 2 Hirarchisches Design und Programmierbare

Werbung

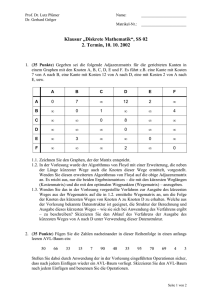

Digitale Elektronik 2 Hirarchisches Design und Programmierbare Logik Dr. T.J.H. Kluter A. Habegger March 7, 2012 Contents 1 Hierarchisches Design 1.1 Der Divide and Conquer Ansatz . . . . . . . . . . . . . . . . . . . . . . . 1.2 Kommunikation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.3 Zusammenfassende Übungsaufgabe . . . . . . . . . . . . . . . . . . . . . 2 Programmierbare Logik 2.1 Programmierbares Logik Array . . . . 2.2 Gate Array Logic . . . . . . . . . . . 2.3 Programmable Logic Device . . . . . 2.4 Complex Programmable Logic Device 2.5 Field Programmable Gate Array . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 1 1 3 5 5 8 10 13 14 1 Hierarchisches Design Dieses Kapitel beschreibt die Methodik ein Problem in kleinere Teilprobleme zu unterteilen bis man zu einen Abstraktionslevel gelangt, auf welchem die Teilprobleme verständlich und einfach lösbar sind. Diese Methodik wir pragmatisch divide and conquer (teilen und herrschen) Methode genannt. Sie umschreibt ein reduktionistischen Lösungsansatz, welcher nicht nur beim Entwickeln moderner digitaler Schaltungen (HW-Design) verwendet werden kann sondern auch für andere Problemstellungen in den angewandten Ingenieurdisziplinen. 1.1 Der Divide and Conquer Ansatz Bei einem “teile und herrsche”-Ansatz wird das eigentliche “grosse” Problem solange in kleinere und viel einfachere Teilprobleme zerlegt, bis man diese problemlos lösen, daher beherrschen, kann (siehe Abbildung 1.1). Das initiale Problem kann auch als Puzzle und die Teilprobleme, welche wir lösen können, als die einzelne Puzzle Teile bezeichnet werden. Die erste Phase des “teile und herrsche”-Ansatzes ist ein klassisches Top Down Design. Nach der Identifizierung aller Puzzle Teile folgt eine zweite Phase, in welcher die einzelnen Teile zusammen gefügt werden, um die Aufgabestellung schlussendlich zu lösen (Buttom Up). Unglücklicherweise müssen die einzelnen Puzzle Teile miteinander Kommunizieren. Die Kommunikation muss während der ersten Phase des “teile und herrsche”-Ansatzes identifiziert und festgelegt werden. 1.2 Kommunikation Die Kommunikation kann in zwei Hauptgruppen unterteilt werden: • Die erste Gruppe repräsentiert Datenoperationen. Diese Daten können durch e.g. Ganzzahlwerte repräsentiert werden und die dazugehörigen Oparande sind zum Beispiel Additions-, Multiplikations-Einheiten usw. Eine solche Kommunikationseinheit wird oft auch als Daten-Pfad bezeichnet. 1 Hierarchisches Design Big Problem P1 L1 P2 L2 L3 Root Phase 1: Top Down P3 L4 L5 Phase 2: Bottom Up Leaves Figure 1.1: Der “teile und herrsche”-Ansatz: Die Aufgabestellung (Puzzle) wir in einer ersten Phase (Top Down) in kleinere Teile unterteilt, welche einfach, verständlich und lösbar sind (Puzzle Teile). In einer zweiten Phase (Bottom Up) werden alle Teile zusammen gefügt, um das initiale grosse Problem zu lösen. • Die zweite Gruppe repräsentiert Kontrolloperationen. Diese Gruppe definiert, ob zum Beispiel eine Leuchte eingeschaltet wird, eine gewisse Datenoperation ausgeführt werden muss usw. Die zweite Gruppe wird oft als Kontroll-Pfad bezeichnet. In diesem Kurs wird die zweite Gruppe – der Kontroll-Pfad – vorwiegend behandelt. Der Kontroll-Pfad kann in zwei Kommunikationsablauf-Modelle unterteilt werden: 1. Master-Slave. Bei der Master-Slave-Kommunikation wird durch den Master eingeleitet, ob und wann der Slave eine bestimmte Aktion ausführen muss. Man kann auch sagen, dass der Slave durch den Master angestossen (gekickt) wird. Die einfachste Master-Slave-Kommunikation wird durch ein enable Signal umgesetzt. Das enable Signal ist aktiv wenn der Slave eine bestimmte Aufgabe zu erledigen hat und inaktiv wenn er warten muss. 2. Master-Master, Slave-Slave, or Slave-Master. Bei diesen Kommunikationsarten fragt der Eine Kommunikationspartner den Anderen, ob es in Ordnung sei, wenn er eine bestimmte Aktion ausführe. Dieser Anfrageprozess wird durch ein request Signal eingeleitet. Nach erfolgter Anfrage wird diese durch den anderen Partner entweder angenommen durch aktivieren des acknowledge Signals oder abgelehnt durchs aktivieren des nack Signals. Diese Mehrsignal-Kommunikation wird auch oft als handshaking bezeichnet. 2 Zusammenfassende Übungsaufgabe In praxisnahen Designs ist die Kommunikation meist um ein vielfaches komplexer und in sogenannten Protokollen spezifiziert. Ein Protokoll ist nichts anderes als eine standardisierte Formulierung, wie der Kommunikationsprozess abzulaufen hat und wie sich welcher Partner in welchem Fall verhalten muss. 1.3 Zusammenfassende Übungsaufgabe Um die gelernte Methode (“teilen und herrschen”) zusammen mit der MasterSlave Kommunikation zu festigen, soll ein Blinklicht entwickelt werden. Das Blinklicht hat eine Referenzfrequenz von 500 Hz. Die Blinkfrequenz soll jedoch nur 1 Hz sein mit den Ein- und Aus-Phasen von je 0.5 Sekunden. 3 2 Programmierbare Logik Programmierbare Logik ist eine Unterklasse der ASICs, welche es erlaubt Logik anhand von Funktionen zu beschreiben ohne einzelne Transistoren zu spezifizieren und zu implementieren. Einfach gesagt, abstrahiert die programmierbare Logik das digitale Schaltungsdesign auf das Level der funktionalen Beschreibung. Man kann dies Abstraktion mit der Verwendung von Assembly anstelle der Maschinensprache bei der Programmierung eines Mikrocontrollers vergleichen. 2.1 Programmierbares Logik Array Das erste Element in dieser Gruppe ist wohl die Programmable Array Logic (PAL). Die Architektur eines PAL basiert auf der Tatsache, dass jede logische Funktion durch die Form Sum of Product repräsentiert werden kann, e.g., Y = A·B+A·B. Daher beinhaltet die PAL Architektur ein Array von AND-Operatoren gefolgt von einem Array aus OR-Operatoren. Um nun jede erdenkliche logische Funktion zu realisieren, werden die Eingänge und jeweils ihr Invers durch “Sicherungen” (trennbare Verbindungen) mit einem AND-Operator verbunden. Der Aufbau der PAL kann anhand der Grafik 2.1 studiert werden. Um eine logische Funktion in ein PAL zu programmieren, müssen unerwünschte und daher überflüssige Verbindungen getrennt werden. Das Trennen wird durch anlegen einer zu hohen Spannung 12V-21V an unerwünschten Verbindungsstellen im “Sicherungs” -Netzwerk realisiert, worauf die Verbindung durchschmilzt und dauerhaft getrennt wird. Weil dieser Prozess irreversible ist, nennt man ein PAL auch ein One-Time-Programmable (OTP) Baustein. Ein Beispiel eines programmierten PALs ist in der Grafik 2.2 dargestellt. Eine spezielle Situation für ein PAL ist anhand der Grafik 2.1 aufgezeigt. Wir nehmen an, dass wir die XOR Funktion implementieren möchten: Y = A · B + A · B. Diese Funktion verwendet nur zwei AND-Operationen, jedoch beinhalten die Makro-Zellen in Grafik 2.1 vier AND-Operationen. Man könnte nun sagen, dass man diese Funktion somit nicht umsetzen könnte. Damit dies trotz dieser Tatsache möglich ist muss unsere Funktion wie folgt angepasst werden: 5 Programmierbare Logik Programmable fuses AND−Array OR−Array To other macro−cells Macro−cell VCC VCC VCC VCC Inputs A B C D VCC VCC X VCC Output Output Y VCC Figure 2.1: Aufbau der PAL Zelle. Jeder Ausgang wird durch eine Makro-Zelle generiert. Eine Makro-Zelle besteht aus einem “Sicherungs”-Netzwerk, AND-Operanden und OROperanden. 6 Programmierbares Logik Array To other macro−cells VCC VCC VCC VCC Inputs A B C D VCC VCC X VCC Output Output Y VCC Figure 2.2: Logik Funktionen werden durch den irreversiblen Prozess – durchschmelzen unerwünschter Verbindungen – in einem PAL dauerhaft gespeichert. Frage: Welche logische Funktion ist in diesem programmierten PAL enthalten? 7 Programmierbare Logik Y = A · B + A · B + A · A + A · A = A · B + A · B + 0 + 0. Der grosse Vorteil eins PALs ist die Tatsache, dass die Verzögerung irgend eines Eingangs (A, B, C, D, ...) zu irgend einem Ausgang (X, Y, ...) fix ist und durch tio charakterisiert wird. Die Vor- und Nachteile des PALs sind in der Tabelle 2.1 zusammengefasst dargestellt. Vorteil Sparsam puncto Energieverbrauch Fixe In-nach-Out Verzögerung(tio) Alle kombinierbaren Logikfunktionen Nicht-Flüchtig Nachteil One-Time-Programmable (OTP) Nur kombinatorische Logik möglich Anzahl der Makro-Zellen ist limitiert Table 2.1: Vor- und Nachteile der PAL Architektur. 2.2 Gate Array Logic Um den grössten Nachteil des PALs, die One-Time-Programmability (OTP), zu eliminieren hat Lattice Semiconductors die Gate Array Logic (GAL)-Architektur entwickelt. Der grösste Unterschied zischen GAL und PAL besteht in der Art und Weise, wie das Sicherungs-Netzwerk realisiert wurde (siehe Grafik 2.1). Bei der GAL Architektur sind die Sicherungen durch Floating Gate Transistors (FGMOS), siehe Grafik 2.3, ersetzt worden. Die FGMOS Zelle, dargestellt in der obersten Zeichnung der Grafik 2.4, ist ein Speicherelement, welches die Ladung auf seinem isolierten Floating-Gate Floating Gate Transistor Figure 2.3: Bei den GALs sind die vorher eingeführten “Sicherungen” durch “Floating Gate Transistors” ersetzt worden und machen dadurch GALs In-System-Programmable (ISP). 8 Gate Array Logic speichert. Die Ladung auf dem Floating-Gate verbleibt für etwa 10-20 Jahre. Die Funktionsweise eines FGMOS kann anhand der Prozesstrennung in Programmierund Betriebs-Modus erklärt werden. Im Programmiermodus werden das Kontroll-Gate und das Bulk verwendet, um das Floating-Gate zu Laden oder Entladen. Dies ist unten Links in Grafik 2.4 dargestellt. Im Betriebsmodus belässt man das Kontroll-Gate in unverbundenem (floatendem) Zustand, wobei der Ladungszustand auf dem floating-Gate den Funktionsmodus des FGMOS festlegt. Wenn das Floating-Gate geladen ist, wird ein N-Kanal zwischen Source und Drain in der FGMOS Zelle gebildet, wodurch der Strom zwischen Drain und Source fliessen kann. Man kann auch sagen, dass das FGMOS als Kurzschluss in der Source-Drain Strecke agiert. Wenn nun das Floating-Gate ungeladen ist, wird die Source vom Drain isoliert. In diesem Betriebsmodus agiert die FGMOS Zelle als ein Unterbruch in der Source-Drain Strecke. Beide Modi sind rechts unten in der Grafik 2.4 dargestellt. Aufgrund physikalischer Effekte können FGMOS Zellen nur rund 10’000 mal programmiert und/oder gelöscht werden. Nach dem erreichen der maximalen Programmier- und Löschzyklen kann ein Kurzschluss zwischen dem FloatingGate und dem Gate/Bulk entstehen. Weil man FGMOS Zellen elektrisch programmieren und löschen kann, hat man zusätzlich die Möglichkeit System nachträglich (im Betrieb) zu verändern. Dies nennt man auch die Fähigkeit der In-System-Programmability (ISP). Für den ISP Betrieb werden GAL Bausteine mit einer sogenannten ISP-Logik erweitert. Ein rundum Überblick ist anhand der Grafik 2.5 gegeben. Die Vor- und Nachteile von GALs sind in der Tabelle 2.2 zusammengefasst dargestellt. Vorteile Geringer Energieverbrauch Fixe In-nach-Out Verzögerung (tio ) Jegliche kombinatorischen Funktionen Nicht-flüchtig In-System-Programmable (ISP) Nachteile Informationsbestehen zirka 10-20 J Nur kombinatorische Logik Limitierte Anzahl von Makrozellen Nur etwa 10’000 Programmierzyklen Table 2.2: Überblick zu den Vor- und Nachteilen der GAL. 9 Programmierbare Logik Control Gate Source Drain Isolation n+ n+ p−bulk Bulk Floating Gate Programming: Normal Operation: The charged floating gate creates a n−channel between Source and Drain hence a "short−circuit" Electrons are tunneled from floating gate + 12V n+ SET: n+ n+ p−bulk − n+ p−bulk There is no charge on any of the gates; therefore, there is an isolation between Source and Drain Electrons are tunneled toward floating gate − 12V n+ + n+ ERASE: p−bulk n+ n+ p−bulk Figure 2.4: Vereinfachter Programmier- und Löschvorgang von Floating Gate Transistoren. 2.3 Programmable Logic Device Der gemeinsame Hauptnachteil der GAL und PAL Strukturen ist die Eigenschaft, dass nur Funktionen aus kombinatorischer Logik implementiert werden können. Um Beispielsweise einen endlichen Zustandsautomaten zu implementieren, müssen noch externe Komponenten einbezogen werden, damit man die sequenzielle Logikfunktion realisieren kann. Dies führte zum Verlangen und daher zur Entwicklung der Programmable Logic Devices (PLDs). Bei den PLDs sind die Makrozellen durch ein Speicherelement erweitert – einem D-Type FlipFlop 10 Programmable Logic Device VCC In System Programming Logic To other macro−cells VCC Inputs A B C D VCC VCC VCC VCC Y VCC Output Output X VCC Figure 2.5: Das GAL bietet die gleichen Möglichkeiten wie ein PAL, ausser dass es noch flexibler in der Verwendung ist, was durch das Feature der In-System-Programmability (ISP) erzielt wird. 11 Programmierbare Logik (D-FF). Um beides, kombinatorische und sequenzielle Logik implementieren zu können kann der Ausgang der Makrozellen entweder mit dem Ausgang des ORArrays oder demjenigen des D-FF verbunden werden. Dies bedeutet, dass zwei FGMOS Zellen dazwischen geschaltet werden müssen. Damit schlussendlich der angestrebte Zustandsautomat in einem PLD realisiert werden kann, muss der DFF Ausgang zusätzlich zum Eingang – AND-Array – zurückgekoppelt werden. Die PLD Architektur ist in der Grafik 2.6 dargestellt. VCC In System Programming Logic To other macro−cells VCC Inputs A B VCC VCC D Q VCC Output VCC VCC D Q Output Y X VCC C Figure 2.6: Die PLD Architektur fügt Speicher in Form eines D-FlipFolp zur Makrozelle hinzu. Dies ermöglicht nebst der Implementierung von kombinatorischen auch sequenzielle Logikfunktionen, was für Zustandsautomaten unabdingbar ist. Die Vor- und Nachteile von PLDs sind in der Tabelle 2.3 zusammenfassend dargestellt. 12 Complex Programmable Logic Device Vorteile Geringer Energieverbrauch Fixe In-nach-Out Verzögerung(tio) Alle logischen Funktionen möglich Nicht-flüchtig In-System-Programmable (ISP) Nachteile Information bleibt zirka 10-20 J Limitierte Anzahl von Makrozellen Nur ≈ 10’000 Programmierzyklen Table 2.3: Auflistung der Vor- und Nachteile der PLD Architektur. 2.4 Complex Programmable Logic Device Da die Komplexität digitaler Schaltungen stetig wächst, waren die “kleine” PLDs nicht mehr ausreichend. Dies führte dazu, dass ein weiter Typ – eine Abwandlung des PLDs – das Complex Programmable Logic Device (CPLD) entwickelt wurde. Die CPLD Architektur unterscheidet sich von der PLD Struktur in einem entscheidenden Punkt. Die Ein- und Ausgänge werden von den Makrozellen entkoppelt. (Beachte: Bei allen vorangegangenen Architekturen, waren die ICAusgänge direkt mit den Ausgängen der Makrozellen verbunden. In analoger Weise wurde mit den Eingängen der Makrozellen zu den IC-Eingänge verfahren.) Das CPLD bewerkstelligt das Verbinden mit einem Schaltnetzwerk (routing array). Das Schaltnetzwerk verfügt über eine sogenannte cross-bar, welche es ermöglicht jede erdenkliche Verbindung zwischen den Eingängen und Ausgängen zu realisieren. Diese Verbindungen werden durch FGMOS Zellen, wie in der Grafik 2.7 gezeigt wird, ermöglicht. Die Grafik 2.8 visualisiert eine vereinfachtes Blockdiagramm eines CPLDs und in Tabelle 2.4 werden dessen Vor- und Nachteile zusammengefasst. Vorteile Geringer Energieverbrauch Fixe In-nach-Out Verzögerung (tio ) Alle logischen Funktionen sind unterstützt Nicht-flüchtig In-System-Programmable (ISP) Nachteile Daten bleiben für 10-20 J Nur ≈ 10’000 Programmierzyklen Table 2.4: Zusammenfassung der Vor- und Nachteile der CPLD Architektur. 13 Programmierbare Logik 2.5 Field Programmable Gate Array Die Skalierbarkeit von CPLDs ist durch ihr Schaltnetzwerk und der Verzögerung der Verbindungen (read delay) limitiert. Zudem kommt hinzu, dass für gewisse Anwendungen, die maximale Anzahl von Wiederbeschreibzyklen der CPLDs nicht ausreichend sind. Dies war die Motivation eine “flüchtige”-Architektur, die sogenannte Field Programmable Gate Array (FPGA) Architektur, zu entwickeln. Der Aufbau von FPGAs (siehe Grafik 2.9) hat grosse Ähnlichkeit mit derjenigen des CPLDs. Ein offensichtlicher und grosser Unterschied liegt bei den Schaltnetzen, welche bei den FPGAs viel kleiner sind. Zudem wurden die Makrozellen der CPLDs bei der FPGA Architektur durch Look Up Tables (LUTs) ersetzt. Das Aufteilen der Schaltnetze führt zum grossen Vorteil der viel besseren Skalierbarkeit dieser Architektur. Tatsächlich kann die Kombination von Schaltnetzwerk und LUT gleichmässig in die X- und Y-Richtung fortgesetzt werden. Dies führt uns zum Nachteil der FPGA Architektur, welche dadurch die Eigenschaft einer Vorhersehbaren In-nach-Out Verzögerung verliert. Die Verzögerung zwischen Eingang und Ausgang ist abhängig von (1) der Anzahl LUTs, welche für eine logische Operation verwendet wurden und (2) der Anzahl verwendeter Schaltnetzwerke zum Verbinden der einzelnen LUTs. Die Grafik 2.10 visualisiert die Implementation der XOR Funktion in einem FPGA. Wie bereits vorher erwähnt, wird das Verschalten bei einem FPGA durch Schaltnetze realisiert. Diese Schaltnetze sind sehr ähnlich zu denjenigen, welche in den CPLDs verwendet werden. Im Gegensatz zu den CPLDs wird bei den FPGAs keine FGMOS Zelle verwendet, um die Verbindung zu realisieren. Es werden an dessen Stelle “pass-gates”, dargestellt in Grafik 2.11, eingesetzt. Beim CPLD wird die Information über eine Verbindung in Form von Ladung auf dem Floating-Gate der FGMOS Zelle gespeichert. Im Vergleich das FPGA, welches ein flüchtiges Speicherelement – ein D-FF – zur Speicherung dieser Information verwendet (siehe links in Grafik 2.11). Eine Speicherzelle, welche die Information 0 enthält repräsentiert eine Verbindung und ein Wert von 1 bedeutet konsequenterweise ein Unterbruch. Das FPGA hat zwei Modi (1) den Programmiermodus bei welchem die Funktionalität jeder Zelle abgebildet ist – links in Grafik 2.11 dargestellt – und (2) den Betriebsmodus in welchem die programmierte Funktion in der FPGA Struktur ausgeführt wird – in Grafik 2.10 und auf der rechen Seite in Grafik 2.11 dargestellt. Ähnlich zum Schaltnetzwerk weist auch das LUT diesen Programmier- und Betriebsmodus auf, siehe dazu Grafik 2.12. Die Grafik 2.12 zeigt zudem noch 14 Field Programmable Gate Array die Hauptunterschiede zwischen der LUT (FPGA) und der Makrozelle (CPLD). Die Makrozelle basiert auf einer Hardwareimplementation der Sum-Of-Product Form. Die LUT basiert auf einer Hardwareimplementation einer Wahrheitstabelle. Jeder Eintrag in der Wahreitstabelle gehört zu einem Speicherelement im Konfigurationsspeicher, wie in der Grafik 2.13 gezeigt wird. Unter Verwendung des Multiplexers (16-Eingänge) wird ein Eintrag in der Wahrheitstabelle selektiert und auf den Ausgang gelegt. Zudem beinhaltet das LUT auch D-FFs, um eine mögliche Implementation von sequenziellen Funktionen zu realisieren. Man beachte, dass die D-FFs in den LUTs für logische Funktionen verwendet werden können, im Gegensatz zu jenen bei der Konfigurierlogik, die nur zum Speichern der Funktionalität eingesetzt werden. Wen man den Programmiermodus des FPGAs genauer untersucht erkennt man, dass er am Besten als einziges grosses Schiftregister umschrieben werden kann. Das Schiftregister muss mit der zu konfigurierenden Information geladen werden (man könnte diesen Referenzdatensatz als bit-file bezeichnen), da das FPGA bei einem power off die Informationen wieder verliert. Dieses laden der Konfigurationen benötigt eine gewisse Zeit Tconf . Während der Konfiguration ist ein aktiver Betriebsmodus ausgeschlossen. Nach der Konfigurierung ist das FPGA bereit logische Funktionen auszuführen. Zusammenfassend werden die Vor-und Nachteile der FPGA Technologie in der Tabelle 2.5 visualisiert. Vorteile Während dem Betrieb re-programmierbar Alle logischen Funktionen sind unterstützt Skalierbare Architektur Nachteile Start-up Zeit grösser Null Tconf Verbraucht deutlich mehr Energie Table 2.5: Eine Auflistung der Vor- und Nachteile von FPGAs 15 Inputs Programmierbare Logik Outputs Figure 2.7: Vereinfachte Darstellung eines Schaltnetzwerks mit 4-Eingängen und 8Ausgängen. Die FGMOS werden verwendet um einen beliebigen Eingang mit einem beliebigen Ausgang zu verbinden. Die Anzahl verwendeter FGMOS Zellen ist das Produkt aus Anzahl Eingängen mit Anzahl der Ausgänge. 16 Field Programmable Gate Array Macro Cell VCC In System Programming Logic Macro Cell Macro Cell Macro Cell Macro Cell Macro Cell VCC D Q Macro Cell Routing Array VCC Macro Cell Macro Cell Macro Cell Macro Cell Macro Cell VCC Figure 2.8: Vereinfachtes Blockschaltbild eines CPLDs. Jede Makrozelle beinhaltet die Logik, welche auf der linken Seite dargestellt ist. Alle Verbindungen werden im programmierbaren Schaltnetzwerk realisiert (siehe Grafik 2.7). 17 Programmierbare Logik Field Programmable Gate Array (FPGA) Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Figure 2.9: Vereinfachtes Blockschaltbild eines FPGAs. Das FPGA basiert auf der Kombination von Schaltnetzwerk und LUT, dieses Strukturelement wird mehrfach repetiert und führt zur Struktur des FPGAs. 18 Field Programmable Gate Array Field Programmable Gate Array (FPGA) Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Routing Array LUT Figure 2.10: Eine XOR Funktion implementiert im FPGA. Die Eingang-nach-Ausgang Verzögerung hängt von (1) der Anzahl verwendeter LUTs und (2) der Anzahl eingesetzter Schaltnetzwerke ab. 19 Programmierbare Logik Configuration Logic (volatile) TDI D Q D Q D Q Routing Array (cross−bar) D Q TCK A TDO V D Q D Q D Q D Q B W D Q D Q D Q D Q C X D Q D Q D Q D Q D Y Figure 2.11: Vereinfachte Blockschaltbild des Schaltnetzwerks. Das Schaltnetzwerk hat zwei Modi (1) Programmiermodus (links) und (2) Betriebsmodus(rechts). 20 Field Programmable Gate Array Configuration Logic (volatile) TDI D Q D Q D Q Look Up Table (LUT) D Q 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 TCK TDO D Q D Q D Q D Q D Q D Q D Q D Q D Q D Q D Q D Q Y D Q X A B C D clock Figure 2.12: Vereinfachtes Blockdiagramm eines LUT. Das LUT hat zwei Modi, diese sind (1) der Programmier-Modus (links dargestellt) welcher priorisiert ist und (2) der Betriebsmodus (rechts dargestellt), welcher im Betrieb der Schaltung verwendet wird. Look Up Table (LUT) Configuration Logic (volatile) A B C D Y 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 1 0 1 1 0 1 1 0 1 0 1 1 0 1 0 1 0 1 0 1 1 1 1 1 1 1 1 1 0 1 1 0 0 TDI D Q D 0 TCK Q D 0 Q D 1 Q 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 0 0 1 0 0 1 1 0 0 1 0 0 1 1 1 0 1 1 0 0 0 1 1 0 1 0 1 0 1 1 1 0 TDO D Q D 1 D Q D Q D D D Q D Q 1 Q 1 D 1 Q 0 Q 0 1 Q 1 D 1 0 D Q Y D Q X Q 0 D Q A B 0 C D clock Figure 2.13: Im LUT wird die Wahrheitstabelle verwendet um Logikfunktionen zu mappen . Jeder Eintrag in der Wahrheitstabelle gehört zu einem Bit in der Konfigurierlogik. Frage: Wie kann eine logische Funktion mit fünf Eingängen realisiertwerden? 21