Strom sparen, aber wie? - All

Werbung

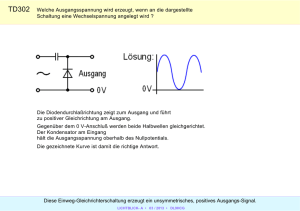

STROMVERSORGUNGEN Low-Dropout-Regler z. B. für Basisstationen Strom sparen, aber wie? Applikationen wie z. B. Mobilfunk-Basisstationen erfordern mehrere Stromversorgungen, die verschiedene Kombinationen von Spannungen und Ausgangsströmen liefern. Die Netzspannung wird oft in eine Gleichspannung von + 48 V bzw. – 48 V umgewandelt, die dann zur Erzeugung niedrigerer Versorgungsspannungen durch das System zu weiteren Gleichspannungswandlern geführt wird. Dabei heißt es, möglichst wenig Leistung in Wärme umzusetzen. Auf der Modulebene wird die Gleichspannung von (–)48 V üblicherweise an einen handelsüblichen Wandler (Brick) angeschlossen, der eine geregelte niedrigere Spannung erzeugt, aus der wiederum innerhalb des Moduls oder auf der Leiterplatte noch geringere geregelte Spannungen abgeleitet werden. Zum Beispiel wird typischerweise aus einer Eingangsspannung von 48 V eine Spannung von 8,5 V erzeugt und (oft) galvanisch von dieser getrennt. Andere Regler erzeugen aus diesen 8,5 V eine Spannung von 7,5 V für HF-Leistungsvertärker (z. B. in einer Basisstation), 5 V und 3,3 V/ 3 V für die Logik und 1,8 V oder niedrigere Spannungen für FPGAs, Prozessorkerne usw. Da beträchtliche Ströme erforderlich sind und darüber hinaus die Verlustleistungsabgabe auf ein Minimum beschränkt werden soll, werden die niedrigeren Spannungen üblicherweise direkt mittels Abwärtsschaltreglern erzeugt. Eine Ausnahme stellt die 7,5-V-Versorgung der HF-Stufen dar, die (zur Rauschunterdrückung) oft aus linearen Bauteilen wie beispielsweise einem Low-Drouput-Linearregler (LDO) erzeugt wird. Linearregler leiten den über der benötigten Ausgangsspannung liegenden Anteil der Versorgungsspannung ab, wodurch eine Leistungsdissipation (Verlustleistung, das Produkt des Ausgangsstroms und der Differenz zwischen Ein- und Ausgangsspannung) frei wird, die sich als Wärme im Durchgangselement darstellt. Um diese Abwärme minimal zu halten muß der Ingenieur ein Gleichgewicht zwischen einer zu hohen Versorgungsspannung, die ˘ AUTOR Keith Welsh ist Field Applications Engineer bei Maxim Integrated Products Inc. in Großbritannien 2 Bild 1: Typischer Kühlkörper für 6,8 ºC/Watt. eine erhöhte Leistungsdissipation bewirkt, und den Erfordernissen des Durchgangselements finden, so dass die lineare Regelstufe bei allen zu erwartenden Betriebsspannungen und Lastströmen arbeitsfähig bleibt (d. h. nicht in den Sättigungs- oder Dropout-Bereich regelt). In diesem Beispiel kann die Versorgungsspannung durch anderweitig im System auftretende Lasten um bis zu 100 mV schwanken, wobei der Spannungsabfall im LDO bis zu 900 mV betragen kann. Daher stellt eine mittlere Versorgungsspannung von 8,5 V einen guten Kompromiß dar. Eine nominale Differenzspannung von 1 V ist somit in diesem Fall gerade noch akzeptabel. Da die Dropout-Spannung vieler sogenannter LDOs in Wirklichkeit größer als 1 V ist, erfordern diese Bausteine eine noch höhere Überspannung (Headroom). Bei einem Headroom von 1 V beträgt die Leistungsdissipation im seriell geschalteten Durchgangselement 1 V x 10 A oder 10 W. Ein solcher Betrieb erfordert eine kontrollierte Wärmeabfuhr, wodurch ein zusätzlicher Kühlkörper mit entsprechenden Ma- terial- und Montagekosten notwendig wird. Der Temperaturanstieg in einem typischen, 6,8 °C/W abführenden Kühlkörper (von Aavid Thermalloy) mit montiertem TO-220 Gehäuse (Bild 1) beträgt 68 °C gegenüber der Umgebungstemperatur (zur Einfachheit ohne Berücksichtigung von RθJC oder anderen thermischen Impedanzen). Der Einsatz eines kleineren Kühlkörpers ist unwahrscheinlich, da die Wärmedissipation anderer Bauteile die Temperatur im Einschubkasten über die Außentemperatur treiben. Daher würde der dargestellte Kühlkörper wahrscheinlich mit einer Betriebstemperatur von weit mehr als 100 °C arbeiten. Um den Spannungsabfall über dem seriellen Durchgangselement niedrig zu halten, ist ein FET mit geringem RDS(on) erforderlich, und die gegebene Polarität schreibt einen p-Kanal-FET vor. Ein p-Kanal-FET kann mehr als den doppelten Betriebswiderstand aufweisen als ein n-Kanal-FET gleicher Bauweise, so dass der Regler immer noch mit einem gewissen Verlust arbeiten wird. P-Kanal-FETs sind desweiteren auch teurer. elektronik industrie 7 - 2007 STROMVERSORGUNGEN Im Beispiel vergleichen wir zwei FETs von International Rectifier: den p-Kanal IRF9Z34N und den n-Kanal IRFZ34. Beide erfordern eine Durchbruchspannung von 55 V. Bei 100 ºC, weist der p-Kanal-Baustein einen Betriebswiderstand von 100 mΩ auf und leitet einen Strom von 12 A, während der n-Kanal-Baustein nur einen Widerstand von 40 mΩ aufweist und 18 A leiten kann. Der p-Kanal-Baustein ist darüber hinaus ungefähr doppelt so teuer. Wenn der Strom einen Maximalwert von 10 A erreicht, weist der p-Kanal-FET einen Spannungsabfall von zirka 1 V auf, während über dem n-Kanal-FET mit seinem Betriebswiderstand von 40 mΩ immerhin noch 400 mV abfallen. Alternativ kann ein bipolarer pnp-Transistor verwendet werden, aber auch bei diesem fällt die KollektorEmitter-Sättigungs¬spannung um zirka 200 mV ab. Als weitere Alternative bietet ein n-Kanal-FET mit extrem niedrigem Betriebswiderstand bessere Leistungen als eine bipolare Lösung. Jedoch erfordert ein solcher Baustein eine Gate-Steuerspannung, die höher ist als die bereit stehende Versorgungsspannung. Wenn man für diese Applikation doch nur einen extrem niederohmigen n-Kanal-FET hätte … Dieses Problem wird mit Schaltreglern gelöst, in denen niederohmige n-Kanal-FETs erfolgreich in einem als Bootstrapping bekannten Verfahren eingesetzt werden, bei dem die dynamisch geschalteten und über eine Diode miteinander verbundenen Spannungsquellen einen Speicherkondensator aufladen, der wiederum eine Gate-Steuerspannung für den n-Kanal-FET liefert, die höher ist als die Ausgangsspannung. Falls Ihre Schaltung oder Ihr Modul einen Abwärtswandler beinhaltet, können Sie daher dessen Schaltsignal möglicherweise zur Erzeugung der für den Linearregler erforderlichen Gate-Steuerspannung verwenden. Dazu muss der Schaltausgang eines Abwärtswandlers an einen einfachen Spannungsmultiplikator angeschlossen werden. Ein beliebter Spannungsmultiplikator ist der in Reihe geschaltete Halbwellenmultiplikator: die Villard-Kaskadenschaltung (Bild 2). Eine an diese Schaltung angeschlossene Wechselspannung ± Us wird darin vervierfacht und liegt dann am Ausgang als 4 Us an. elektronik industrie 7 - 2007 Bild 2a: Ein kaskadierender Villard-Spannungsmultiplikator. Bild 2b: Das Eingangspotential dieses Spannungsverdopplers liegt zwischen +V und dem geschalteten +V, wodurch sich eine Ausgangsspannung von 2 (+V) ergibt. Somit würde die Schaltung eine Ausgangsspannung von 4 Us erzeugen, wenn die Schaltspannung um Us Volt um das Massepotential schwingen würde. Jedoch schwingt der Schaltausgang eines Abwärtswandlers nur ungefähr von Vin bis Masse. Bei einer Versorgunsspannung von 8,5 V schwingt die vom Abwärtswandler in die Spule abgegebene Schaltspannung somit von 0 V bis + 8,5 V, wodurch sich (in Bild 2) Us = 4,25 V ergibt. Die Berechnung wird weiter dadurch erschwert,dass das Mark-Space-Verhältnis des Wandlers vom Verhältnis der Eingangsspannung zur Ausgangsspannung sowie von der Last abhängt. In dieser Betrachtung gehen wir aber als Diskussionsgrundlage einmal davon aus, dass sich bei einem Mark-Space Verhältnis von 50 % am Ausgang eine ungefähre Gleichspannung von 17 V ergibt. Falls eine höhere Ausgangsspannung notwendig ist, kann diese durch Kaskadieren mehrerer Multiplikatoren erzeugt werden. In diesem Beispiel kann je- doch eine einfachere Lösung – ein Spannungsverdoppler – zum Einsatz kommen, die mit nur zwei Dioden und zwei Kondensatoren eine Schwachstrom-Ausgangsgleichspannung erzeugt (Bild 2a). Die zuvor erzeugte Gleichspannung von 17 V kann an einen einfachen Schwachstrom-Linearregler (wie z. B. den MAX1616) angelegt werden, dessen einzige Aufgabe darin besteht, die Gate-Steuerspannung für das Durchgangselement – den niederohmigen n-Kanal-FET – zu liefern. Der FET zieht seinen Strom aus der 8,5-V-Versorgung, und sein Ausgang dient als 7,5-V-Versorgung für den HF-Verstärker – und zwar mit einer Regelschleife über einen Spannungsteiler zum Steuereingang des Linearreglers. Dieses Konzept wurde mit einer Schaltung aus einem MAX5060-Evaluationskit (EVKIT), dem Linearregler MAX1616, n-Kanal Leistungs-MOSFET sowie entsprechend erforderlichen Bauteilen bewiesen. Bild 3 zeigt das vereinfachte Blockschaltbild, Bild 4 die tatsächliche Schaltung. 3 STROMVERSORGUNGEN Bild 3: Blockschaltbild einer Reglerschaltung mit Zero-Dropout. Bild 4: ZDO-Schaltbild (ZDO: Zero-Dropout). Schaltungsbeschreibung Der Abwärtswandler MAX5060EVKIT erzeugt 3,3 V mit einem Ausgangsstrom von bis zu 20 A. Seine Schaltfrequenz liegt bei zirka 270 kHz. Er erzeugt 3,3 V aus einer Eingangsspannung von 12 V, jedoch wurde die in Bild 4 dargestellte Schaltung zur Beweisführung nur mit 1 A belastet. Der Ar- 4 beitstakt des an die Spule angelegten Spannungssignals, das zwischen Masse und 12 V schwingt, beträgt ca. 25 %. Diese Schaltspannung treibt außerdem einen Spannungsmultiplikator, der am Eingang des Linearreglers (MAX1616) eine Gleichspannung von zirka 24 V erzeugt. Die tatsächliche Ausgangsspannung des Multi- plikators betrug ungefähr 22,7 V – genug um den Linearregler zu steuern. Der Ausgang des Linearreglers treibt das Gate des niederohmigen n-Kanal-FET (IRFZ24N). Eine variable Versorgung liefert den Strom für den FET, wodurch der Spannungsabfall für verschiedene Eingangs- und Ausgangsspannungen bestimmt und verifiziert werden kann. Das Gate des FET wird vom LDO MAX1616 mit bis zu 22 V angesteuert und seine Leitfähigkeit wird soweit getrieben bis der Spannungsteiler R1 1,24 V rückmeldet und der Regler daraufhin die Treiberleistung in den FET reduziert bis sich ein Gleichgewichtszustand einstellt. Widerstand R2 und Kondensator C2 regeln die Dynamik der Schleife durch Mäßigung des Ansprechverhaltens auf schnelle Störspitzen und Rauschsignale vom Linearregler. R2 zieht des Weiteren zum Ausschalten des FETs Strom vom Gate ab und dient als Last für den Linearregler. Über das Verhältnis des Spannungsteilers kann der FET-Ausgang auf eine beliebige Spannung zwischen 0 V und der Ausgangsspannung der variablen Stromversorgung eingestellt werden. Zu diesem Zweck wurde für R1 ein 250-kΩ-Potentiometer gewählt, mit dem der Ausgang des MAX1616 von 1,25 V bis auf über 22 V eingestellt werden kann. Der Spannungsabfall wird für alle Eingangsspannungen und Lastzustände durch Suche nach dem Abfallpunkt der Treiberspannung des FET-Gates ermittelt, der anzeigt wenn die Regelschleife die Steuerung der Schaltung übernimmt. Sobald die Treiberspannung des FET-Gate unter die vom LDO MAX1616 bereit gestellten 22 V absinkt, tritt die Schaltung in einen geregelten Zustand. Durch Messung der Differenz zwischen Ein- und Ausgangsspannung des Durchgangselements kann der Spannungsabfall für verschiedene Versorgungsspannungen und Lastzustände ermittelt werden. Dieses Verfahren hat sich als sehr effektiv bei der Ermittlung des Spannungsabfalls eines linearen Durchgangselements erwiesen, und es ist nicht überraschend, dass es den Betriebswiderstand des MOSFETs widerspiegelt. Das Verhalten der Schaltung ist in der Tabelle und der Kurve in Bild 5 dargestellt. elektronik industrie 7 - 2007 STROMVERSORGUNGEN Schlussfolgerung Diese Schaltung (Bild 4) beweist, dass ein Zero-Voltage-Dropout-Regler (ZDO) aus einem niederohmigen n-Kanal-FET gebildet werden kann, der von der Ausgangsspannung eines Spannungsmultiplikators getrieben wird. Mit abnehmender Ausgangslast schwindet die Differenz zwischen Ein- und Ausgangsspannung, und sie erreicht Null ohne Last. In der dargestellten Schaltung sowie bei Applikationen mit hohen Strömen kann die Verlustleistung im Durchgangselement unter Beibehaltung der Regelung minimal gehalten werden, wodurch wiederum der Bedarf nach Kühlkörpern oder anderen Hilfsmitteln Temperaturmanagement reduziert werden kann. Die Applikation für Basisstationen bietet 1 V Headroom für den LDO. Dem gegenüber kann die ZDO-Lösung den benötigten Headroom auf die Summe aus der Spannungswelligkeit der 8,5-V-Versorgung und des Spannungsabfalls reduzieren. Ein sehr niederohmiger FET wie z. B. der IRF1324 reicht aus, um den für die beschriebene Applikation erforderlichen Strom von 10 A zu liefern. Sein Betriebswiderstand von weniger als 1 mΩ erlaubt den Bau eines ZDOReglers mit einem theoretischen Abfall von nur 1 mV/A. Im hier besprochenen Beispiel würde ein solcher FET die höchste anzunehmende Gesamtleistungsdissipation des Durchgangselements reduzieren, da nur ein Headroom von 100 mV für die lastbedingten Schwankungen im System, sowie weitere 10 mV aufgrund des Betriebswiderstands des FETs erforderlich sind.Die zwischengeschaltete Versorgung kann daher von 8,5 V auf 7,61 V reduziert werden. elektronik industrie 7 - 2007 Bild 5: Ergebnisse der in Bild 4 dargestellten ZDO-Schaltung. Der gesamte Spannungsabfall würde nur 110 mV betragen und die daraus resultierende Leistungsdissipation bei 10 A nur etwas über 1 W, wodurch die Verlustleistung um 9 W reduziert wird. Der Einsatz des IRF1324 macht darüber hinaus einen Kühlkörper und die mit dessen Anschaffung und Montage verbundenen hohen Kosten überflüssig, da die geringere entstehende Wärme leicht von einem SMD-Baustein direkt in das Kupfer der Leiterplatte abgeleitet werden kann. Die um 9 W geringere Verlustleistung spart außerdem Strom. Des Weiteren kann dieser ZDO z. B. für batteriebetriebene Systeme verwendet werden, bei denen der Spannungsabfall einen beträchtlichen Teil der Betriebsspannung der Batterie darstellt. In solchen Systemen kann der ZDO die Betriebszeit zwischen Ladezyklen verlängern. Dennoch wurde diese Schaltung nur als Konzept verifiziert und nur mit niedrigen Gleichspannungen getestet. Die Entwickler können diese Schaltung für dynamische Lasten und geringere Differenzen zwischen Ein- und Ausgangsspannung weiter optimieren. (av) ˘ infoDIRECT 313ei0707 www.elektronik-industrie.de ˘ Link zu Maxim 5