Skript zur Vorlesung

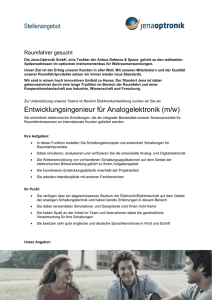

Werbung