Leistungsbauelemente in der Automobilindustrie - E

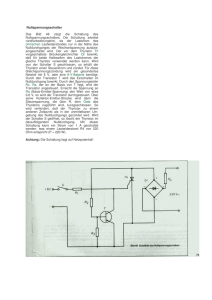

Werbung