Klausur20013

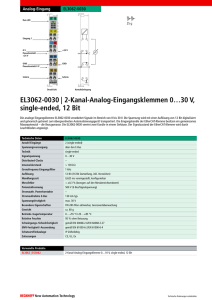

Werbung

F A C H H O C H S C H U L E

F Ü R

D I E

W I R T S C H A F T

F H D W ,

H A N N O V E R

EINGEBETTETE SYSTEME

K LAUSUR

Studiengang: Informatik

Studienquartal: II. Theoriequartal

Prüfungsumfang:

Skript „Hardware“ vom 7. 9. 01;

Skript „Grundlagen der Informatik“, Kapitel „Endliche Maschinen“

Dozent: Michael Löwe

Termin: 25. September 2001

Dauer: 90 Minuten

40 Punkte sind zu erreichen: davon Wissen 16 Punkte, Anwendung 16 Punkte, Transfer 8 Punkte.

Bestanden ab 20 Punkte.

TEIL I: WISSEN (30 MINUTEN)

Aufgabe 1 (2 Punkte): IT-Lösungen werden in zwei Bereichen benötigt, im Bereich der Betrieblichen Informationssystem und im Bereich der Eingebetteten Systeme. Geben Sie je zwei typische Beispiele für Systeme aus den

beiden Bereichen an, nennen Sie eine typische Anforderung jedes Bereichs an die IT-Lösungen!

Aufgabe 2 (2 Punkte): Entwickler eingebetteter Software-Systeme müssen sich intensiv mit der zugrunde liegenden

Hardware des Systems auskennen. Warum? Mit welcher Entwurfsphilosophie versucht der professionelle Entwickler

den Einfluss der Hardware auf sein Programm zu minimieren?

Aufgabe 3 (3 Punkte): Wie funktioniert die Eingabe und Ausgabe in Eingebetteten Systemen bei ausschließlicher

Nutzung von „Memory-mapped I/O (MMIO)“?

Aufgabe 4 (3 Punkte): Welcher entscheidende Nachteil des „MMIO“ wird durch „Interrupt-controlled Input (ICI)“ beseitigt? Wie funktioniert der Interrupt-Mechanismus?

Aufgabe 5 (3 Punkte): Welcher entscheidende Nachteil ausschließlicher Nutzung von MMIO und ICI wird durch

„Direct Memory Access (DMA) beseitigt? Wie funktioniert DMA? Was leistet ein DMA-Controller.

Aufgabe 6 (3 Punkte): Erläutern Sie den Unterschied zwischen Maschinenprogrammen und –Befehlen auf der

einen Seite und Mikroprogrammen bzw. –Instruktionen andererseits!

TEIL II: ANWENDUNG ( 40 MINUTEN)

Aufgabe 7 (3 Punkte): Wie ändert sich die Bedeutung der Signale in

einem S/R-Latch (siehe Abbildung), wenn man die beiden NOR-Gatter

durch zwei NAND-Gatter ersetzt? Kann man ein Gatter mit ähnlicher

Schaltlogik auch aus nur zwei Gattern aufbauen, wenn einem ausschließlich AND und OR-Gatter zur Verfügung stehen? Wie sieht dann

die Bedeutung der Signale im Vergleich zum Standard-S/R-Latch aus?

S

¬Q

R

Q

Eine Endliche Maschine M=(E, A, Z, T: E Z Z, F: E Z A*, z0)

besteht aus: (1) einem Eingabealphabet E, (2) einem Ausgabealphabet A, (3) einer endlichen Zustandsmenge Z, (4) einer totalen Abbildung zur Zustandstransformation T: E Z Z, (5) einer totalen Abbildung zur Erzeugung der Ausgaben F: E Z A* und

(6) einem Anfangszustand z0 Z.

Aufgabe 8 (4 Punkte): Entwickeln Sie eine Endliche Maschine mit E=A={0, 1, E}, die zwei Binärzahlen subtrahiert. Das Zeichen „E“ steht für sowohl „Ende der Eingabe“ als auch „Ende der Ausgabe“.

Die Eingabe der zwei Zahlen, die zu subtrahieren sind, erfolgt dabei Bit-weise abwechselnd vom niederwertigsten Bit

zum höchstwertigen. Das erste Eingabezeichen ist das niederwertigste Bit des Subtrahenden (Die Zahl, die abgezogen werden soll). Dann folgt als zweites Eingabezeichen das niederwertigste Bit des Minuenden (Die Zahl, von der

abgezogen werden soll). Usw. Die kürzere Zahl wird mit führenden „0“-en aufgefüllt. Soll z. B. von „1100“ die Binärzahl “101“ subtrahiert werden, sieht die Eingabe so aus „E10110001“. Sie wird von rechts nach links verarbeitet.

Die Ausgabe sollte dann „E0111“ (von rechts nach links erzeugt) sein.

Ist eine Eingabe vollständig bis zum „E“ verarbeitet, soll der Automat wieder im Anfangszustand sein! Underflow, i.

e. Subtrahend > Minuend, soll nicht besonders behandelt werden, z. B. 0101 – 1100 = 1001.

Aufgabe 9 (5 Punkte) Bauen Sie den Automaten aus der letzten Aufgabe in Hardware. (Es ist dabei unerheblich, ob

Ihre Lösung zu Aufgabe 8 richtig ist oder nicht. Sie sollen Ihre Lösung in Hardware bauen!)

Im Takt des Automaten sollen ihm die einzelnen Eingabezeichen zugeführt werden. Wenn es nichts zu tun gibt, soll

ständig das E-Zeichen an der Eingabe anliegen und auch als Ausgabe produziert werden.

Zeichnen Sie den Hardware-Automaten schematisch so, dass die Breite des Zustandsregisters, die Breite des Ausgaberegisters und die Menge der digitalen Eingabesignale erkennbar und alle Signale (jedes Eingabebit, jedes Zustandsbit und jedes Ausgabebit) eindeutig benannt sind!

Geben sie in drei Tabellen die binäre Darstellung für die Eingabezeichen E, Zustände Z und Ausgabezeichen A aus

Ihrer Lösung für Aufgabe 8 im Hardware-Automaten an!

Geben Sie die Wahrheitstafel an, die die Funktionen T und F aus der letzten Aufgabe in Hardware realisiert!

Aufgabe 10 (4 Punkte): Die Hardware für ein eingebettetes System soll

(1) einen Prozessor mit 16 Bit Adress- und 8 Bit Datenbus,

(2) einen 8192 8 Bit Programmspeicherbaustein (EPROM),

(3) einen 8192 8 Bit Datenspeicherbaustein (RAM),

(4) zwei 8255 Parallel-Ports mit je 4 8-Bit-Registern, die der Prozessor adressieren (entspricht 2 Adressleitungen),

beschreiben und auslesen kann, und

(5) einen Anzeigebaustein von 32 8 = 256 Zeichen (1 Zeichendargestellt durch 8 Bit), die der Prozessor adressieren (entspricht 8 Adressleitungen) und beschreiben kann, erhalten.

Entwickeln Sie eine „Memory Map“ für dieses System! (D. h., auf welche Leitungen des Adressbusses werden die

Adressleitungen der einzelnen Bausteine geschaltet und wie sieht die Adressdekodierung für die CS-Signale der fünf

Speicher- und I/O-Bausteine aus?) Begründen Sie die konkrete Wahl Ihrer „Memory Map“.

TEIL III: TRANSFER (20 MINUTEN)

Aufgabe 11 (4 Punkte): Neben Registern und Speicher kann man aus D-Latches eine weitere wichtige Art von

Bausteinen aufbauen, sogenannte „Counter“ (Englisch für Zähler). Entwickeln Sie die Schaltung für einen Counter,

der die steigenden Flanken des Eingabesignals IN zählt und die bisher gezählte Anzahl mit den Ausgabesignalen D 0

– D3 als Binärzahl darstellt. Natürlich zählt der Zähler „modulo 16“, d. h. nach 15 zeigt er als nächstes (nach der

nächsten steigenden Flanke von IN) wieder 0.

Benutzen Sie für Ihren Baustein 4 D-Latches

und einen Pulsgenerator, der die steigenden

Flanken von IN in kurze Pulse S(IN) umsetzt, vgl. Skizze! (Der Puls ist kürzer als die

Zeit, die das D-Latch für einen Zustandswechsel benötigt.)

IN

Erweitern Sie Ihre Schaltung um einen weiteren Eingang RESET, der beim nächsten INSignal den Zähler auf 0 stellt.

S(IN)

D

Q

Clk

Wie muss man Ein- und Ausgänge dieses

Zählers (mit Reset) verbinden, um einen

Dezimalzähler (Zählung modulo 10) zu erhalten?

Q

D0

D

Q

D

Q

Clk

D1

Q

Clk

Q

D2

D

Q

Clk

Q

D3

Aufgabe 12 (4 Punkte): Definieren Sie Endliche Maschinen mit

(a) zwei Eingabeströmen,

(b) zwei Ausgabeströmen und

(c) mit zwei Eingabe- und zwei Ausgabeströmen.

Ihre Definitionen sollten Modifikationen der Definition oben vor Aufgabe 8 sein.

(d) Verallgemeinern Sie jetzt Ihre Definition auf n Eingabeströme und m Ausgabeströme.

Nutzen Sie dazu die Familiennotationen: (Ai)iI eine Familie von Mengen Ai für jedes i I, XiI(Ai) das kartesische

Produkt über der Familie (Ai)iI und (Fi :Ai Bi) iI eine Familie von Abbildungen.