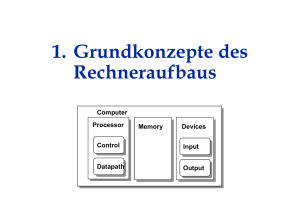

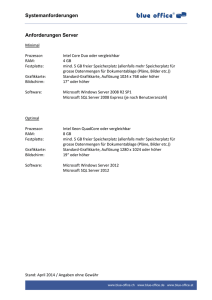

Technische Grundlage..

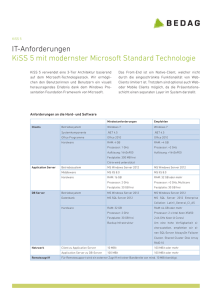

Werbung