Eigenschaften der HF-Schaltungen - All

Werbung

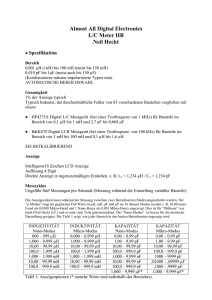

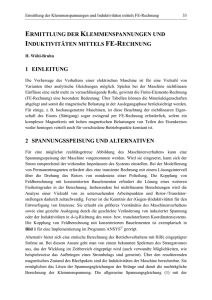

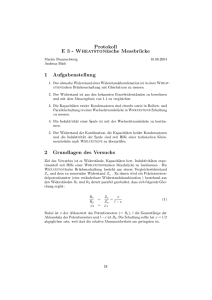

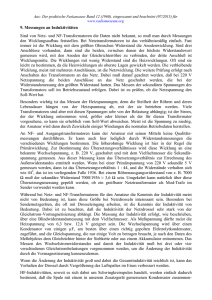

Potential einer kostengünstigen 90 nm-CMOS-Plattform hoher Leistung für HF-Anwendungen Nachweis der Eigenschaften an zwei HF-Schaltungen Als Basis für eine kostengünstige HF-CMOS-Plattform dient die in elektronik industrie Heft ½-2006 beschriebene 90 nm-CMOS-Technologie, auf die zusätzliche Lagen aufgebracht werden, um Induktivitäten hoher Güte und verlustarme Verbindungen zu integrieren. Damit weist diese Plattform verbesserte analoge und HF-Leistungsmerkmale für aktive und passive Komponenten auf. In diesem Beitrag werden die HF-Eigenschaften der 90 nm HF-CMOSPlattform in Verbindung mit Induktivitäten hoher Güte auf dem IC betrachtet und durch zwei rauscharme LNAs für 5,5 und 24 GHz nachgewiesen. Eigenschaften der HF-Schaltungen Die schlagenden Vorteile der „Above-IC“-Technologie (Bilder 1 und 2) sind durch die erfolgreiche Realisierung von zwei HF-Schaltungen nachgewiesen worden: Ein rauscharmer Verstärker LNA (Low Noise Amplifier) für 5,5 GHz mit ESD (Electrostatic Discharge)-Schutz und ein 24 GHz-LNA mit nachträglich aufgebrachten Induktivitäten. 5,5 GHz-LNA mit ESD-Schutz Die Ausstattung moderner HF-CMOS-Schaltungen mit ESD-Schutz hat sich zu einer anspruchsvollen Aufgabenstellung entwickelt: Bei Betriebsfrequenzen oberhalb 1 GHz verschlechtern sowohl herkömmliche ESD-Schutzstrategien (wie der Einsatz kleiner Dioden) als auch neuartige ESD-Ansätze (wie etwa Resonanzkreise) die HF-Eigenschaften. Darüber hinaus bieten sie nicht das erforderliche Maß an ESD-Sicherheit. Eine Lösungsmöglichkeit liegt im Einsatz von Parallel-Induktivitäten, die sich sehr robust gegenüber ESD verhalten. Wenn sie allerdings in gegenwärtig aktuellen CMOS-Prozessen implementiert werden, ist ihr Serienwiderstand zu hoch, um den Spannungsabfall über der Induktivität abzubauen. Dies kann zu einer gefährlichen Spannungsüberhöhung am extrem dünnen Gate-Oxyd führen. Eine attraktive und kostengünstige Lösung kann nun darin bestehen, die Induktivität mit Dünnfilm-WLP-Techniken aufzubauen. Deren Serienwiderstand ist sehr gering, so daß sich diese „Above-IC“-Induktivitäten sehr gut zum ESD-Schutz eignen. Um die ESD- und HF-Eigenschaften dieser nachträglich auf dem Chip integrierten Induktivitäten zu bestimmen, ist ein voll integrierter LNA für 5,5 GHz als Funktionsmuster ausgeführt worden. Die Induktivität liegt als „Plug and Play“-ESD-Schutz am HF-Eingang des LNA, der in 90 nm HF-CMOSTechnologie implementiert ist. Derart geschützt widersteht der LNA an seinem Eingang einer ESD-Belastung von über 8 kV gemäß dem HBM (Human Body Model). Darüber hinaus verbessert die hohe Güte der Induktivitäten für Anpaßnetzwerk und Lastankopplung ganz entscheidend die HF-Eigenschaften der Schaltung: Leistungsverstärkung von 16 dB und ein Rauschmaß von lediglich 2,5 dB bei einem extrem niedrigen Leistungsbedarf von nur 2,4 mW. Diese Leistungskennwerte wurden mit einem identischen LNA verglichen, dessen Induktivitäten aber als BEOL-Metallschichten realisiert wurden. Dieser Aufbau war in gleichem Maße robust gegen ESD-Belastung, aber die Vorteile der „Above-IC“-Induktivitäten zeigten sich deutlich in einer Verbesserung des Verstärkungsfaktors, Verringerung des Rauschfaktors und wesentlich kleinerer Leistungsaufnahme. Wenn die Verkleinerung der Strukturen anhält und die Durchbruchspannung des Gate-Oxyds weiter sinkt, dann kann es notwendig werden, zusätzlich kleine Klemmdioden zum ESD-Schutz einzuführen. Diese Dioden können die Spannung, die sich am Gate-Oxyd als Folge einer ESD-Belastung aufgebaut hat, auf einen MIM-Kondensator umleiten. Dieser verträgt eine wesentlich höhere Spannungsbelastung als das dünne Gate-Oxyd. Experimente haben gezeigt, daß sich die Klemmdioden zusätzlich zu den auf dem IC liegenden Induktivitäten realisieren lassen, wodurch sich die HF-Eigenschaften nur geringfügig verschlechtern. 24 GHz-LNA mit „Above-IC“-Induktivitäten hoher Güte In dem Maße, in dem die Betriebsfrequenzen der HF-Schaltungen steigen, sollte das Potential der 90 nm HF-CMOS-Technologie für höhere Frequenzbereiche untersucht werden. Unter Umständen wird ein Übergang zu Millimeterwellen notwendig, um die Nachfrage nach den immer weiter steigenden Datenraten in der Kommunikation zu befriedigen. In einem ersten Schritt ist das HF-Potential der Technologie im oberen K-Band ausgelotet worden. Dazu dient ein 24-GHz-LNA als einstufiger Verstärker in SourceBasisschaltung (Bild 4). Zur Stabilisierung ist die Source induktiv beschaltet; damit kann auch ein Kompromiß zwischen Rauschverhalten und Eingangsanpassung gefunden werden. Die Koppelkondensatoren an Ein- und Ausgang sind auf dem Chip als BEOL-MIM-Kapazitäten ausgeführt, während „Above-IC“-Induktivitäten und BEOL-MIM-Kondensatoren für die Impedanzanpassung an Ein- und Ausgang sorgen. Die Meßwerte, die dieser Verstärker bei einer Versorgungsspannung von 1 Volt liefert, ließen ihn im Vergleich mit modernen Lösungen in CMOSTechnologie bei 24 GHz in gutem Licht erscheinen: Ein Rauschmaß von 3,2 dB und eine Verstärkung von 7,5 dB konnten bei einem niedrigen Leistungsbedarf von 10,6 mW erreicht werden (Bilder 3a und b). Diese Ergebnisse verdeutlichen das Potential der 90 nm CMOS-Technologie, ergänzt um WLP-Technologie für Induktivitäten hoher Güte auf dem Chip, für einen Betrieb im höheren Frequenzbereich. Aussichten für eine Skalierung Die Beschäftigung von IMEC mit 90 nm HF-CMOS unterstreicht, daß sich HF-CMOS als Mitbewerber der Technologie der Wahl für die Massenproduktion (RFID, WLAN...) von Anwendungen im unteren bis mittleren Frequenzbereich von 0,9 bis 10 GHz entwickelt, mit gleichzeitig guten Aussichten für höhere Frequenzbereiche. Dieser Schluß wird sehr wahrscheinlich auch noch für die 65 nm-Technologie gelten. Anders dürfte es bei 45 nm-Strukturen aussehen: Wegen der Einführung fortschrittlicher Prozeß-Module und neuer Architekturen könnten sich damit realisierte CMOSBauteile signifikant von 90 nm- und 65 nm-CMOS unterscheiden. Derzeit gibt es allerdings noch keinen weltweiten Konsens über die Architektur und Prozeß-Module: Die große Vielfalt an möglichen Architekturen (Bulk, SOI (Silicon on Insulator) als Verarmungstyp und FinFETs), an Gate-Materialien (SiON, high-k) und Gate-Elektrodenmaterial (poly, voll siliziertes poly, Metall-Gate) erfordert umfangreiche Untersuchungen zur Abschätzung ihres Potentials für HF-Anwendungen. Vor kurzem hat sich der Multigate-MOSFET, insbesondere der FinFET, als eine der vielversprechendsten technologischen Lösungen zur Erfüllung der ITRS-Anforderungen an weitere Skalierung herausgestellt. In einem FinFETBauteil besteht der Kanal aus einer sehr dünnen Silizium-Finne, welche die Kontaktbereiche von Source und Drain verbindet. Dabei entscheidet die Finnen-Geomterie (Höhe, Abstand und Breite) mit über den Steuerstrom, den Serienwiderstand und analoge Leistungsmerkmale. Für HF-Schaltungen wird das niederfrequente Rauschen als zusätzlicher Parameter in die Gestaltung der optimalen Finnen-Geometrie eingehen. Wie allgemein für Full-Depleted-Technologien, gelten auch hier eine verbesserte Steuerung der Kurzkanal-Effekte und hohe immanente Verstärkung. Wegen der unterschiedlichen Architekturen und der grundsätzlich anderen Gleichungssysteme für die Beschreibung des Stromtransports sind aber noch viele Anstrengungen zur Entwicklung skalierbarer und kompakter Modelle für aktive Bauteile auf der Basis von FinFETs und Varaktoren nötig. Schlußfolgerungen Diese Untersuchung hat die Leistungsfähigkeit der 90 nm HF-CMOSTechnologie für Anwendungen im niedrigen, mittleren und sogar höheren Frequenzbereich demonstriert. Besondere Beachtung galt dabei der Güte integrierter passiver Komponenten. Zwei Versuchsschaltungen wiesen nach, daß die 90 nm CMOS-Technologie in Verbindung mit der „Above-IC“Integration von Dünnfilm-Induktivitäten kostengünstige HF-Schaltungen mit ausgezeichneten Kenndaten liefert: Eine auf dem IC aufgebrachte Induktivität diente als „Plug and Play“-Lösung für den ESD-Schutz des HF-Eingangs eines 5,5 GHz-LNAund ein LNA für 24 GHz wurde entwickelt und experimentell verifiziert. Als entscheidende Einflußgrößen einer weiteren Skalierung gelten neue Architekturen und Prozeß-Module. Über welches Potential künftige 45 nm- Bauteile in analogen und HF-Anwendungen verfügen, muß in eingehenden Untersuchungen geklärt werden. Autoren : M. van Bavel, O. Dupuis, A. Mercha, G. Carchon und D. Linten, IMEC, Belgien Bildunterschriften Bild 1: Prinzip der kombinierten BEOL- und WLP-Verbindungsstrukturen. Bild 2: FIB (Focused Ion Beam)-Querschnitt von fünf Metallisierungslagen in BEOL und „Above-IC“-Verbindungen. Bild 3a : Meßwerte für ein LNA mit „Above-IC“-Induktivität zum ESDSchutz, Leistungsverstärkung. Bild 3b : Meßwerte für ein LNA mit „Above-IC“-Induktivität zum ESDSchutz, Rauschmaß. Bild 4: Chip-Foto des 24-GHz-LNA.