CPU (Central Prozessor Unit)

Werbung

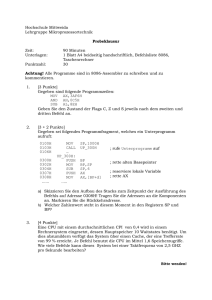

Berufl. Gymnasium GG CPU (Central Processor Unit) Referat von: Sebastian, Serhat und Eren Technische Wissenschaften Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Gliederung Geschichte der CPU – Miniaturisierung – CPU Hersteller und Rechner – µProcessor CPU – Zukünftige Entwicklung: Biologische CPU Aufbau der CPU – Allgemeiner Aufbau – Zusammenspiel CPU und Peripherie – CISC - RISC Funktionsweise der CPU – Zentraleinheit – Register – Befehlsausführung Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Geschichte der CPU – – – – Miniaturisierung CPU‘s und Rechner µProcessor CPU Biologische CPU Serhat Imrag Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Miniaturisierung SSI Small Scale Integration 1-10 Transitoren/Chip MSI Medium 10-500 LSI Large 500-10000 VLSI Very > 10000 SLSI Super > 50000 Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Entwicklung der LSI-Technik LSI Speicher, RAM, ROM UART UART und Schieberegister Tisch und Taschenrechner Universal Asynchronous Receivers Transistor Mikroprozessor Support Chips Mikrocontroller LSI-Interfaces Mikrocomputer Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG CPU-Hersteller und Rechner Hersteller Rechner IBM /370, Power HP HP-RISC Digital Eclipse, Alpha SUN Sparc Intel PC’s Apple PC’s Pocket … Motorola AMD Transmeta … Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Die ersten 20 Jahre der CPU: µProcessor 1971 Intel 4004: erster Mikroprozessor mit 4-Bit Datenbreite (2.300 Transistoren) 1974 Motorola 6800: erste vollwertige CPU mit 8-Bit Datenbreite; eigene Architektur (68x-) mit nicht-Intel-kompatiblem Befehlssatz (4.100 Transistoren) 1975 Intel 8080: erste vollwertige Intel-CPU mit 8-Bit Datenbreite; Einsatz im ersten "Home-Computer", dem Altair 8800 (6.000 Transistoren) 1977 Weiternetwicklung der Motorola 6800-CPU; gilt als bester 8- Bit Mikroprozessor überhaupt (6.809 Transistoren) 1985 Intel 80386: erste 32-Bit-CPU in Intel-Spezifikation; sie kann als erste CPU mehrere Programme gleichzeitig verarbeiten (Multitasking, 275.000 Transistoren) 1989 Intel 80486: integriert mathematischen Co-Prozessor; 4 mal so viele Transistoren wie beim 80386 (1.180.000 Transistoren) 1989 Motorola 68040: mit integrierter Fließ-Komma-Einheit und getrenntem Cache (Speicher) für Befehle und Daten (1.200.000 Transistoren) 1991 AMD 386 DX: erster AMD-Klon einer Intel-CPU; geringere Transistorenzahl und höhere Taktfrequenz; dem Original teilweise überlegen (200.000 Transistoren) Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG CPU-Leistungsentwicklung Mio.Transistoren/CPU-Die 300 250 200 Intel AMD 150 100 50 0 486/K5 Klasse 11 BG-D P II Itanium/Opteron 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Aufbau der CPU – Allgemeiner Aufbau – Zusammenspiel CPU und Peripherie – CISC – RISC CPUen Eren Metin Elci Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Definition µP-CPU Comptersystem: 5 Funktionseinheiten CPU Steuereinheit Eingabe ALU Ausgabe Speicher µProzessor: ist eine LSI-Baustein, der die meisten Funktionen eines traditionellen Prozessors auf einem einzigen Chip vereinigt Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Moderner Aufbau einer µP-CPU Klasse 11 BG-D Control Unit: a Processing Unit: b Cache Unit: c Chipset: d Interner Bus e Externer Bus f 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Erläuterung der CPU-Funktionsblöcke Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Internes Bussystem eines Rechners Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Rechnerbausteine CPU RAM ROM Peripherie DMA Taktgeber Chipset Steuerbus Adressbus Datenbus Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Datenflussdiagramm Arbeitsablauf der einzelnen RechnerKomponenten Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Heutige CPU Generationen POWER4 Floorplan Itenium Floorplan CPU Building Block >35GB/s Chip Interconnect Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Register-Bitbreite und Speicheradressen CPU Physikalische (bit) Adressbreite/ Virtueller/Adressierbarer Speicher (Byte) Register (bit) i80xx 8 8 i286 16 16 Pentium 32 32 2 GB Itanium 64 64 8 TB K5 16 16 Athlon, 64 32/64 32 2 GB,4 GB/1TB Opteron 64 48/40 256 TB / 1 TB Klasse 11 BG-D 64 kB 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Funktionsweise der CPU – – – – Zentraleinheit Register Steuereinheiten Befehlsausführung Sebastian Biewer Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Die CPU Komponenten CPU-Register Verwendung der CPU-Register Arithmetik- und Logik-Einheit (ALU) Kontrolleinheit (CU) Buffer-Register (BR) Zustands-Bits (Status Flag SF) Befehlsausführung Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Einfaches Modell der CPU Register Status-Flag A BR Komplement Addition und Daten-Bus ALU Verschiebung DZ PZ Steuerleitungen Steuereinheit Boolsche Algebra ALU-Operation: Bufferregister 1. Binäre Operation 2. Boolsche Algebra 3. Komplementbildung eines Datenwortes 4. Verschieben Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG CPU Komponenten ALU Bedeutung Register Interne CPU Steuereinheit Interner CPU-Datenbus Bufferregister Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Die Register der CPU Register Bitmuster Abkürzung Akkumulator 8-bit A Datenzähler 76543210 16-bit DZ - Adressen 15 . . . 876543210 Befehlsregister 8-bit BR - Befehle 76543210 Programmzähler 16-bit 15 . . . 876543210 Klasse 11 BG-D PZ – Adresszähler des Programms 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Register Die Register sind die direktesten Speicher-Elemente in der CPU Ein Register ist eine Speichereinheit in der CPU Ein einzelnes Datenwort kann darin abgelegt werden Ein Register ist die kleinste Speichereinheit auf dem Chip Der Zugriff auf den Registerinhalt erfolgt sehr schnell Die Anzahl der Register variiert von ca. 10 bis zu einigen 100 Die Größe der Register ist abhängig von der CPU-Architektur (8-, 16-, 32und 64-Bit-CPU). Die Bit-zahl gibt die Größe des Registers an, also wie groß das Datenwort sein kann Register dienen als kurzzeitiger Zwischenspeicher für Daten/Adressen Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Verwendung der Register der CPU Am Beispiel des Additionsprogramms Programmspeicher Adresse Speicher 0400 9C 0401 0A 0402 30 0403 40 0404 9C 0405 0406 0407 0408 Anfangszustand A DZ Befehl 1 0400 Befehl 3 Vor Addition 7A 0A 31 9C 0407 80 Befehl 4 Addition A9 60 Befehl 5 80 0A Befehl 2 31 Daten- 0A30 7A speicher 0A31 2F 0A 31 A DZ BR PZ DZ BR Nach Addition A9 0A 31 60 0409 23. Jan. 2004 PZ A 0408 0409 Klasse 11 BG-D BR PZ A DZ BR PZ © 2004 Sebi Berufl. Gymnasium GG Stack (Bufferregister) Der Stack dient als Zwischenspeicher Der Befehl, der als letztes einging, wird als erstes verarbeitet – „Last In, First Out“ Prinzip Im Stack kann nur ein weiterer Eintrag hinzugefügt werden, „push“, oder ein Eintrag entnommen werden, „pop“ Stacks finden Verwendung bei – – – Parameterübergaben dem kurzzeitigen sichern von Daten dem anlegen lokaler Variablen BP Basepointer – Verwendung bei z.B. Parameterübergaben SP Stackpointer – Der Stackpointer ist ein Zeiger oder Register, der auf die Speicheradresse des dem Stack zuletzt hinzugefügten Elements zeigt Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Interrupt In der Regel wird der Interrupt durch ein elektrisches Signal einer Hardware ausgelöst, dem Interruptcontroller. Der Prozessor unterbricht seine bisherige Arbeit und springt an eine vordefinierte Stelle, der Sprungadresse. Nach dem Abarbeiten der Anforderung setzt der Prozessor sein Arbeit wieder an der Stelle wo unterbrochen wurde wieder fort. Normalerweise werden in der Interruptverabeitung Informationen von der Hardware eingelesen und verarbeitet. Das Betriebssystem hat die Möglichkeit, die Annahme von InterruptRequests zu unterbinden. Außerdem kann auch der Prozessor die Annahme verweigern. Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Befehlssatz Umsetzung der Mnemonik-Befehle der Register in den Binärcode in der ALU Die Menge aller zur Verfügung stehenden Befehlsanweisungen. Der Befehlssatz bei AMD und Intel CPUs unterscheiden sich Es gibt bei den meisten Befehlen parallelen, aber jeder Hersteller stellt einige spezifische Befehle zur Verfügung, wie z.B. SSE, SSE2, MMX Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Befehlszyklus Der Befehlszyklus gibt die Reihenfolge an, mit der ein Befehl abgearbeitet wird 1. 2. 3. 4. Der Befehl wird geladen (IF = Instruction Fetch) Der Befehl wird decodiert und ein Register wird geladen (ID & RF= Instruction decode and register fetch) Als nächstes werden dann ALU-Operationen ausgeführt (EXE = execution of ALU operation) und in den Speicher geschrieben (MEM = memory access) anschließend wird das Ergebnis in ein entsprechendes Register zurück geschrieben (WB = write back to register file). Über so genanntes Pipelining können mehrere Zyklen gleichzeitig abgearbeitet werden Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Register von 64 bit CPU’s Itanium Opteron Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG HOLD-Anforderung Anhalten des Prozessors, damit z.B. direkte Speicherzugriffe DMA möglich sind Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Flags Vorzeichen und Überlauf Flag Carry-Bit und Hilfscarry Vorzeichen und Überlauf Flag Zero Flag (Neuzustands Bit) – Das Zero Flag wird auf “1” gesetzt, sobald eine Rechenoperation das Ergebnis “0” hat – Das Zero Flag wird auf “0” gesetzt, sobald eine Rechenoperation ein Ergebnis ungleich “0” hat Status Flag (Zustands Bits) – Status Flags sind eine Einheit der ALU – Können von der CPU gesetzt “Set” und rückgesetzt “Reset” werden: Flip-Flop – Wird benutzt, um die Ergebnisse der ALU-Operation wiedergeben zu können – Jeder binäre Logikteil, der nur 2 Zusände hat, wird als Status Flag bezeichnet Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Referenzen Einführung in die Mikrocomputer-Technik, Adam Osborne Computerpartner SPEC CPU2000 Internet: AMD, IBM, Intel Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG Appendix CPU Tabellen AMD/Intel Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG CPU-Leistungsentwicklung (bei Intel) Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi Berufl. Gymnasium GG CPU-Leistungsentwicklung (bei AMD) Klasse 11 BG-D 23. Jan. 2004 © 2004 Sebi