Dokument_11.

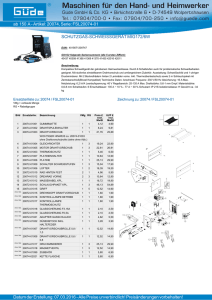

Werbung