Hardware / Software Codesign

Werbung

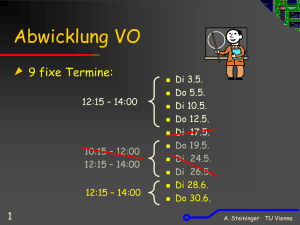

Trost & Rat Homepage: http://ti.tuwien.ac.at/ecs/teaching/courses LVA Leiter: Jakob Lechner Andreas Steininger Peter Tummeltshammer email: [email protected] Bitte LVA im TUWIS abonnieren 1 A. Steininger TU Vienna Voraussetzungen Inhaltlich: gute Kenntnisse in VHDL günstig: HW-Modellierung Kenntnis des ASIC-Design Flow günstig: DiDeVO & DiDeLU Formal: VO, LU und Vorauss. formal unabhängig im Magister-Studienplan Techn. Informatik 2 A. Steininger TU Vienna Abwicklung VO 9 fixe Termine: 3 Mo 20.4. Mi 22.4. Mo 27.4. Mi 29.4. Mo 4.5. Mi 6.5. Mi 13.5. Mo 22.6. Mi 24.6. jeweils 10:15 bis 12:00 im Sem TI A. Steininger TU Vienna Benotung Vorlesung: Teilnahme an der Diskussion Besprechung der Lösung aus der LU Laborübung: 4 praktisches Ergebnis Besprechung der Lösung aus der LU A. Steininger TU Vienna Vorlesung Ziel: theoretischer Hintergrund Ausbildung eines Problembewusstseins prinzipielles Verständnis Weg: 5 Impulsvorträge / Gastvorträge (Diskussionen in Kleingruppen) Diskussionen im Plenum A. Steininger TU Vienna Was ist HW/SW Codesign? paralleler Entwurf HW/SW schneller Bugs früher sichtbar höherer Abstraktionsgrad Partitionierung HW/SW übergreifende Optimierung Integration v. Systemen aus/mittels HW/SW 6 systematische Schnittstellendefinition Komplexitätsbewältigung A. Steininger TU Vienna Embedded Systems: Challenges „An exploding number of embedded reactive heterogeneous components in mass-market products“ „Massive seamless integration of heterogeneous components in a real-world environment“ „Building systems of guaranteed functionality and quality at an acceptable cost is a major technological and scientific challenge“ [Joseph Sifakis, Workshop on Strategies for Embedded Systems 2005] 7 A. Steininger TU Vienna The Constraints Dependability safety, security, availability [Joseph Sifakis, Workshop on Strategies for Embedded Systems 2005] Autonomy no humans in the loop Low resource consumption memory, power, energy Physical constraints weight size, heat dissipation, … Market positioning 8 optimal cost/quality, time to market A. Steininger TU Vienna The System-Centric Approach Joint Design (HW, SW, Environment) to determine cost / quality tradeoffs Requires a combination of competencies in SW, automation, networks, electronics, man-machine interfaces => training, education [Joseph Sifakis, Workshop on Strategies for Embedded Systems 2005] 9 A. Steininger TU Vienna The Current State no unified theory to predict the dynamic properties of a SW running on a given execution platform complex systems are built through a succession of incremental developments exploding validation costs 10 [Joseph Sifakis, Workshop on Strategies for Embedded Systems 2005] A. Steininger TU Vienna Anwendungsbeispiele Consumer-Products unglaubliche Features kleiner Preis, kleine Größe, lange Akku-Lebensdauer Mobiltelefonie zusätzlich Mixed-Signal Design Automotive extreme Anforderungen bezügl. Sicherheit & Preis 11 A. Steininger TU Vienna Die Herausforderungen Miniaturisierung mixed signal, dynamische Rekonfiguration, Energiebudget Rekonfiguration, power management,… Komplexität Interfaces, formale Verifikation Produktivität / Time to market Abstraktionsebenen, Automatisierung Fehlertoleranz 12 A. Steininger TU Vienna Ziel der VO + LU Bewusst-Machen der Problematik Analysieren der Trade-offs Verständnis für den Optimierungsprozess, dessen Kriterien und Randbedingungen Vermitteln erster eigener Erfahrungen Non-Target: Kennenlernen bestehender Tools 14 A. Steininger TU Vienna Diskussion Vor-Auswahl Wählen Sie für die folgende Diskussion einen der Anwendungsbereiche (jede Gruppe eines) 15 Automotive Telekom Industrie-Automation Raumfahrt Multimedia (MP3, Camcorder,…) Telebanking A. Steininger TU Vienna Diskussion Fragen Welche Anforderungen an das Produkt (= Embedded System, nicht Gesamtprodukt) bestehen? Was fällt in die Klasse „Kosten“ ? Was fällt in die Klasse „Nutzen“ ? Was ist speziell an Ihrem Anwendungsbereich? Wie kann man sie zum Zeitpunkt des Partitioning quantitativ erfassen? 16 A. Steininger TU Vienna Wh. The Constraints Dependability safety, security, availability [Joseph Sifakis, Workshop on Strategies for Embedded Systems 2005] Autonomy no humans in the loop Low resource consumption memory, power, energy Physical constraints weight size, heat dissipation, … Market positioning 17 optimal cost/quality, time to market A. Steininger TU Vienna Haben wir schon alles… Verifikation/Test Wartbarkeit/Debug Zuverlässigkeit Zertifizierbarkeit Durchsatz Reaktionszeit, Jitter Kopierschutz, Security Lagerhaltung 18 Fehlertoleranz eigenes Know-How second source Entwicklungstools Entwicklungszeit Time to market Verfügbarkeit IPs Erweiterbarkeit Entsorgung größe A. Steininger TU Vienna Prinzip einer Optimierung Mittels eines Algorithmus soll eine Kostenfunktion minimiert oder eine Nutzenfunktion maximiert werden und zwar unter Einhaltung von Randbedingungen Als Voraussetzung müssen daher Kosten / Nutzen meßbar und alle Randbedingungen bekannt sein 19 A. Steininger TU Vienna Erfassen der Eigenschaften die relevante Eigenschaften müssen erfasst werden quantitativ, hinreichend genau schon früh im Design Flow Ist das realistisch möglich? Tools erstellen Schätzungen auf Basis von 20 vereinfachten Modellen Heuristiken A. Steininger TU Vienna Optimaler Tradeoff Wie vergleicht man quantitativ 21 Speicherverbrauch physikalische Größe Performance Preis A. Steininger TU Vienna Gegebene Plattform Typisches Szenario gegeben ist Prozessor FPGA für Spezialfunktionen => SW => HW Reales Problem 22 optimale Nutzung des vorh. Prozessors („Einsparen“ bringt keinen Gewinn!) optimale Nutzung des FPGA Es geht um ein „optimales“ Verschieben von Tasks zwischen FPGA und Prozessor A. Steininger TU Vienna Termine Vorlesung 23 20.4. 27.4. 29.4. 4.5. 6.5. 13.5. VB + allg. Einführung Kostenfaktoren & Constraints, Trends Erklärung der Übungsaufgabe Gastvortrag Prof. Rupp Gastvortrag DI. Scheurer Gastvortrag Dr. Armengaud 22.6. 24.6. Präsentation Übungsergebnisse Präsentation Übungsergebnisse A. Steininger TU Vienna Gastvortrag Prof. Markus Rupp Institut für Nachrichtentechnik und HF-Technik Leiter des CD Labors „Design Methodology of Signal Processing Algorithms“ „The Chip Design Crisis“ 4. Mai 2009, Seminarraum TI 24 A. Steininger TU Vienna Gastvortrag Dipl.-Ing. Dieter Scheurer Managing Director Gleichmann Electronics Research Austria „Debugging mittels Semulator“ 6. Mai 2009, Seminarraum TI 25 A. Steininger TU Vienna Gastvortrag Dr. Eric Armengaud Projektleiter Das Virtuelle Fahrzeug (Graz) „Detailed simulation on application level“ 13. Mai 2009, Seminarraum TI 26 A. Steininger TU Vienna