hwr_kap04_vers23

Werbung

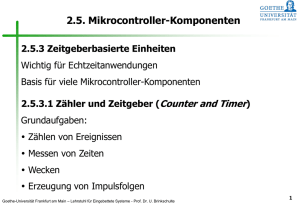

Lehrstuhl für Eingebettete Systeme Hardwarearchitekturen und Rechensysteme 4. Schaltnetze Folien zur Vorlesung Hardwarearchitekturen und Rechensysteme von Prof. Dr. rer. nat. U. Brinkschulte Prof. Dr.-Ing. L. Hedrich (basierend auf Materialien von Prof. Dr.-Ing. K. Waldschmidt) Motivation Schaltnetze sind kombinatorische digitale Schaltungen. Rechnerwerkzeuge für den Entwurf und die Simulation dieser Schaltungen basieren auf der Booleschen Algebra. In diesem Kapitel wird das Verhalten und die Struktur einiger ausgewählter Schaltnetze behandelt. Es sind Schaltnetze, die für den Aufbau von Operationswerken in Prozessoren benötigt werden. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:2 Gliederung 4.1 Spezielle Schaltnetze 4.1.1 Multiplexer/Demultiplexer 4.1.2 Datenbuszugang 4.1.3 Permutationsschaltnetz 4.1.4 Vergleicher (Komparator) 4.1.5 Addierer 4.1.6 Multiplizierer 4.2 PLA (programmable logic arrays) 4.3 Elektrotechnische Grundlagen 4.4 Zeitliches Verhalten von Schaltnetzen 4.5 Hazards (Gefahr) in Schaltnetzen Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:3 4.1 Spezielle Schaltnetze 4.1.1 Multiplexer/Demultiplexer 4.1.2 Datenbuszugang 4.1.3 Permutationsschaltnetz 4.1.4 Vergleicher (Komparator) 4.1.5 Addierer 4.1.6 Multiplizierer Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:4 4.1.1 Multiplexer/Demultiplexer Ein Multiplexer/Demultiplexer ist ein Schaltnetz, welches eine Datenweiche darstellt. Multiplexer: Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:5 Multiplexer Definition: Ein Multiplexer ist eine Boolesche Funktion f , für die gilt: Für die Abbildung g gilt: Für das Dekodiersignal dk gilt: Beispiel: Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:6 Demultiplexer Demultiplexer arbeiten invers zu den Multiplexern. Sie verteilen einen Datenstrom auf mehrere auswählbare Kanäle. Demultiplexer finden oftmals in integrierten Schaltkreisen Anwendung, um die Zahl der Anschlußpins zu begrenzen. In DRAMs beispielsweise wird der höherwertige und der niederwertige Teil der Adresse nacheinander auf den Adreßbus gelegt. Der Baustein muß dann die Signale intern demultiplexen und dem Spalten- bzw. Zeilendekoder zuführen. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:7 Datenwegschaltung Multiplexer: 0 Eingangsdatenwege n-1 Steuereingänge Datenwegschaltung Decoder Demultiplexer: Eingangsdatenweg Steuereingänge Ausgangsdatenweg Datenwegschaltung 0 Ausgangsn-1 datenwege Decoder Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:8 Anwendung – Busbasiert Datenbus AkkuRegister ALU Hilfsregister Multiplizierer Pufferregister Ansteuerung Ergebnisbus Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:9 Anwendung – Multiplexerbasiert Ansteuerung AkkuRegister Register 1 Register 2 ALU Register 3 Multiplexer Ansteuerung Ergebnisregister 1 Demultiplexer Ergebnisregister 2 Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:10 2:1 Multiplexer Funktionstafel: KV-Diagramm: e 0 0 0 1 1 sel 0 1 1 0 e 1 Schaltplan: Funktion: Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:11 4:1 Multiplexer Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:12 4:1 Multiplexer sel0 1 sel1 2 Decoder Enable Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik e0 0 e1 1 e2 2 e3 3 f HWR · K4 Nr.:13 8:1 Multiplexer sel0 1 sel1 2 sel2 1 Decoder Enable e0 0 e1 1 e2 2 e3 3 1 f 1 2 Decoder Enable e4 0 e5 1 e6 2 e7 3 Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:14 2:1 4-Bit Multiplexer Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:15 Multiplexer – Standardbaustein Steuerung C0 C1 C2 Eingänge Multiplexer sind als integrierte Bauelemente erhältlich. Typischerweise handelt es sich dabei um 8:1 bzw. 16:1 Multiplexer (mit 3 bzw. 4 Steuereingängen). SN74151 (TTL-Baureihe): I0 I1 I2 I3 I4 I5 I6 I7 Y Y Enable Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:16 Implementierung Boolescher Funktionen Jede Boolesche Funktion f(x0, … ,xn-1) kann unter ausschließlicher Verwendung von Multiplexern realisiert werden. Für f: Bn! B ist hierzu ein 2n:1 Multiplexer mit n Steuereingängen notwendig. Die n Eingangsvariablen werden an die Steuereingänge gelegt. Die Belegung der 2n Dateneingänge erfolgt gemäß der Wahrheitstabelle der Funktion f. Anstelle eines 2n:1 Multiplexers kann auch ein 2n-1:1 Multiplexer mit n-1 Steuereingängen verwendet werden. Die Steuereingänge werden mit den Variablen x1, … ,xn-1 beschaltet. Die Dateneingänge werden mit den konstanten Werten 0 und 1 und der freien Variablen belegt. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:17 Implementierung Boolescher Funktionen Beispiel: 2 von 3 Mehrheitsfunktion 0 0 0 0 1 1 1 1 0 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 x2 x1 x0 8:1 Multiplexer 0 0 1 1 f 0 1 0 1 f x2 x1 x 0x 00 1 4:1 Multiplexer Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:18 Beispiel Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:19 Implementierung Boolescher Funktionen Die Beschaltung der Dateneingänge eines 2n-1:1 Multiplexers erhält man durch n-1-malige Anwendung des Shannon'schen Entwicklungssatzes. Beispiel: Boolesche Funktion mit 3 Variablen Die Steuereingänge werden mit den für die Entwicklung gewählten Variablen und die Dateneingänge mit den entsprechenden Co-Faktoren belegt. f(0,0,c) f(0,1,c) f(1,0,c) f(1,1,c) 0 0 1 1 0 1 0 1 a b Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik f HWR · K4 Nr.:20 1:2 Demultiplexer Funktionstafel: KV-Diagramm: e e 0 1 1 1 sel 1 1 sel 0 1 f0 f1 Schaltplan: Funktion: Der nicht beschaltete Ausgang wird mit dem Wert 1 belegt! Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:21 1:4 2-Bit Demultiplexer Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:22 4.1.2 Datenbuszugang Tri-State-Gatter: Ein Tri-State-Gatter besitzt die drei definierten Ausgangszustände 0,1 (abhängig vom Eingangssignal e) und einen hochohmigen Zustand z. Der Zustand z wird durch Aktivierung des Sperreingangs i (inhibit) erreicht. Funktionstafel: Schaltplan: e i 1 a Tri-State-Gatter werden immer dann verwendet, wenn mehrere Ausgänge, von denen nur einer aktiv sein darf, an eine Leitung angeschlossen werden sollen (z.B. Busleitungen). Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:23 Unidirektionaler Datenbuszugang i i 1 Datensender 1 Datenempfänger 1 1 i i 1 1 Datenempfänger 1 1 Datensender Bus Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:24 Bidirektionaler Datenbuszugang Funktionstafel: Schaltplan: Tri-State-Gatter e d a 1 & i r a e 1 i r d & Schaltsymbol 1 1 Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:25 Bidirektionaler Datenbuszugang Einheit 1 Einheit 3 i r i r bidirektionaler Datenbus i r Einheit 2 Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:26 4.1.3 Permutationsschaltnetz Permutationsschaltnetze vertauschen die Reihenfolge von Variablen. Die Vertauschung wird über einen Steuereingang sel aktiviert. Schaltplan: Permutationsschaltnetze werden in Verbindungsnetzwerken verwendet, um verschiedene Kommunikationswege schalten zu können. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:27 4.1.4 Vergleicher (Komparator) Vergleicher sind Schaltungen, die insbesondere in Mikroprozessoren Verwendung finden um beispielsweise den notwendigen Vergleich für bedingte Sprunganweisungen durchzuführen. Vergleicher werden aber auch integriert in Schaltungen eingesetzt, z.B. zur Speicherauswahl oder für die Selektion von Ein-/Ausgabe-Geräten. Vergleich der 2 Booleschen Tupel X und Y: Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:28 n-Bit Vergleicher Vergleicher für n-Bit Zahlen lassen sich hierarchisch konstruieren. (x ≥ y)-Vergleicher: xn & 1 yn fn & x y n-1 n-1 x1 y1 Vergleicher für (n-1)-stellige Dualzahlen f n-1 Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:29 n-Bit Vergleicher n-Bit Vergleicher lassen sich zu Vergleichern von Dualzahlen mit größeren Längen kaskadieren. 7-Bit Vergleicher aus zwei 4-Bit Vergleichern: y1 y2 y3 y4 x1 x2 x3 x4 > Komparator 0 y5 y6 y7 x5 x6 x7 > Komparator Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:30 1-Bit Vergleicher für Dualzahlen Der größer als bzw. kleiner als Vergleicher ist schaltungstechnisch aufwendiger als der Vergleich auf Identität. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:31 4.1.5 Addierer Ein Halbaddierer berechnet aus zwei 1-Bit Zahlen die Summen Si und den Übertrag Ci+1. Funktionstafel: Schaltplan: Funktionen: Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:32 Volladdierer Ein Volladdierer berechnet aus drei 1-Bit Zahlen die Summe Si und den Übertrag Ci+1. Funktionstafel: Schaltplan: Funktionen: Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:33 n-Bit Ripple-Carry-Addierer Ein n-Bit Ripple-Carry-Addierer entsteht durch die Kaskadierung von n-1 Volladdierern und einem Halbaddierer. Im schlimmsten Fall müssen für die Addition zweier n-Bit Zahlen alle Addierer nacheinander durchlaufen werden, bis der Übertrag Sn vorliegt. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:34 Carry-Select-Addierer an-1 bn-1 Ziel: Beschleunigung der Durchlaufzeit an/2 bn/2 0 n/2-Bit-Addierer an/2-1 bn/2-1 cn s‘n-1 an-1 bn-1 a0 b0 0 s‘n/2 n/2-Bit-Addierer an/2 bn/2 1 n/2-Bit-Addierer cn s“n-1 sn/2-1 s0 s“n/2 cn/2 sn-1 sn/2 Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:35 Subtraktionsschaltung aus Volladdierern Die Differenz A-B (A,B ¸ 0) wird durch die Addition des 2-er Komplements :B von B erreicht (A+(: B)), welches auf die bitweise Negation von B zurückgeführt wird: Auftretende Überträge werden nicht berücksichtigt. Beispiel: 4-Bit (Vorzeichen und 3-Bit für die Zahlendarstellung) Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:36 Subtraktionsschaltung auf Volladdierern Addierer/Subtrahierer: Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:37 Allgemeine Vergleicher für Dualzahlen Der größer als bzw. kleiner als Vergleicher basiert auf einem Subtrahierer. Integrierter Vergleicher (Komparator) SN7485: … b0 an-1 bn-1 s0 ≥1 & A<B … a0 n-Bit-Subtrahierer 0 a0 a1 a2 a3 < = > A=B sn-1 & cn A>B b0 b1 b2 b3 Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik coutn/2-1 COMP A<B A=B A>B HWR · K4 Nr.:38 4.1.6 Multiplizierer Schnelle Multiplizierer werden durch parallele Berechnung sämtlicher (dualer) Produktterme und anschließender Addition der Terme mit den richtigen Wertigkeiten implementiert. Es werden m2 viele AND-Gatter für die Bildung der Produktterme und m Addierer benötigt. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:39 Beispiel – 3-Bit Multiplizierer (1) Eingaben: Faktoren a und b Ausgabe: Produkt p = a ¢ b Anschauliche Darstellung: Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:40 Beispiel – 3-Bit Multiplizierer (1) a a 2 1 a 0 b & & 0 & HA Addierer b & & VA 1 & VA HA Addierer b & & VA p 5 p 4 & VA p 3 2 HA p 2 Addierer p 1 Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik p 0 HWR · K4 Nr.:41 Beispiel – 3-Bit Multiplizierer (2) Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:42 Standardbausteine für Multiplikation Für die Multiplikation zweier 4-Bit Dualzahlen existieren die beiden Standardbausteine SN74284 und SN74285. Der Baustein SN74285 berechnet den niederwertigen 4-stelligen Teil des Produktes, der SN74284 den höherwertigen Teil. Multiplikand Multiplikator 23 22 21 20 23 22 21 20 2D 2C 2B 2A 1D 1C 1B 1A 2D 2C 2B 2A 1D 1C 1B 1A SN74284 SN74285 z7 z6 z5 z4 z3 z2 z1 z0 27 26 25 24 23 22 21 20 Produkt Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:43 4.2 PLA (programmable logic arrays) PLAs sind integrierte Schaltungen zur Realisierung von DNFs. Sie sind durch sogenannte Programmiergeräte vom Kunden (Anwender) selbst personalisierbar. PLAs besitzen eine regelmäßige Struktur und sind daher besonders für eine VLSI-Realisierung geeignet. X UND Matrix 1 Z ODER Matrix Y X Literale: Ausgangsvektor: Jede Komponente yi aus Y = y1, y2, …, ym stellt eine DNF dar. Produkttermvektor: Jede Komponente zk aus Z = z1, z2, …, zl stellt einen Konjunktionsterm der negierten oder nicht negierten Literale dar. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:44 PLA (programmable logic arrays) x1 UND-Ebene (UND-Matrix): 1 x2 1 mit den Indexmengen Ik,n und Ik,p der negierten bzw. nicht negierten Variablen UND xn ODER-Ebene (ODER-Matrix): 1 z1 z2 zl y1 y2 ODER ym Die Personalisierung der Matrizen erfolgt durch Aktivierung der Leitungsverzweigungen, meist durch aktive Bauelemente (Transistoren). Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:45 PLA UND/ODER-PLA: NAND-PLA: x1 x1 1 1 x2 x2 1 1 UND UND xn xn 1 1 & & & 1 & y1 ODER & y1 & y ODER 1 y m Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik m HWR · K4 Nr.:46 Beispiel – Volladdierer Boolesche Funktionen: PLA: a i b i a iC i b iC i ai 1 bi 1 Ci 1 C i+1 Si Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:47 PLA, PAL und ROM Der Aufwand der Personalisierung wird geringer, wenn nur eine der beiden Matrizen programmierbar (personalisierbar) ist. Für die Realisierung Boolescher Funktionen stehen 3 personalisierbare Strukturen zur Verfügung: PLA Personalisierung: UND-/ODER-Matrix PAL Personalisierung: UND-Matrix Festwertspeicher (ROM) Personalisierung: ODER-Matrix Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:48 PAL (Programable Logic Array) Bei einem PAL ist die UND-Matrix personalisierbar und die ODERMatrix festgelegt. x1 1 x2 1 xn 1 y1 y2 ym Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:49 ROM Bei einem Festwertspeicher wird die UND-Matrix fest als Adressdecoder personalisiert. 0 1 x1 x2 x3 2 Decoder X/Y 3 4 5 6 7 y1 y2 y3 Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:50 RAM 0 1 2 3 m-4 m-3 Adresse m-2 m-1 Ein Schreib-/Lesespeicher (RAM) hat eine ähnliche Struktur, bei der die personalisierten Leitungsverzweigungen der ODER-Matrix durch Speicherzellen (Flipflops) ersetzt werden. Dadurch kann die Information in der ODER-Matrix jederzeit und schnell geändert werden. Die UND-Matrix ist wie beim ROM fest als Adressdecoder personalisiert. Aufbau eines n£m-Bit Arbeitspeichers: Bit Speicherzellen 0 1 n-2 n-1 Adreßdecoder Daten Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:51 4.3 Elektrotechnische Grundlagen Allgemein: In einem digitalen Datenverarbeitungssystem werden auf der physikalischen Ebene binäre Schaltvariablen mit elektronischen Schaltern nach den Gesetzen der Schaltalgebra verknüpft. Elektronische Verknüpfungsglieder werden aus Halbleiterbauelementen aufgebaut. Verknüpfungsglieder werden zu Schaltnetzen und Schaltwerken zusammengefügt. Schaltkreisfamilien (integrierte Schaltungen) bestehen aus standardisierten Verknüpfungsgliedern, Speichergliedern, Schaltnetzen und Schaltwerken, die aus gleichen Bauelementen und nach dem gleichen elektronischen Konzept hergestellt sind. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:52 Modell des idealen Schalters In der Schaltalgebra werden die binären Variablen mit Verknüpfungsgliedern aus idealen Schaltern verknüpft. UB UB I I R R I I= S ein UQ = 0 S aus UQ = UB UB ein R R aus UB UQ • Im Schalterzustand ’ein’ ist der Innenwiderstandswert des Schalters S Ri=0. • Im Schalterzustand ’aus’ ist der Sperrwiderstand des Schalters S Ri=∞. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:53 Modell des idealen Schalters Die Schaltwirkung folgt unmittelbar der Schaltursache, d.h. es gibt keine Zeitverzögerung. Die vom Schalter aufgenommene Leistung P = U ¢ I ist immer Null, da entweder der Strom I (’aus’) oder die Spannung U (’ein’) gleich Null ist. Kein realer Schalter kann diese Anforderungen erfüllen. Mit elektronischen Schaltern kommt man dem Ziel heute am nächsten. Je nach Bauelementetyp (bipolar oder unipolar) werden mehr die einen oder die anderen Eigenschaften optimal erreicht. Deshalb haben sich verschiedene Schaltkreisfamilien entwickelt. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:54 Modell des realen Schalters UB IE UB IA R R I S S ein UE Ri Rs aus UA UB R IE Ri ein R aus IA UE Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik UA UB Rs UQ HWR · K4 Nr.:55 In der Schalterstellung ’ein’ liegen R und Ri in Reihe und ihre Widerstandsgeraden schneiden sich im Arbeitspunkt ein. Für Strom und Spannung gilt: Am Schalter fällt also eine Spannung UE ab. In der Schalterstellung ’aus’ liegen R und Rs in Reihe und ihre Widerstandsgeraden schneiden sich im Arbeitspunkt aus. Für Strom und Spannung gilt: Trotz Schalterstellung ’aus’ fließt ein Strom IA. In beiden Betriebszuständen wird vom Schalter Leistung aufgenommen, weil der Strom IA bzw. die Spannung UE verschieden von Null sind. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:56 MOS-FET als Schalter UB ID ID U th = threshold voltage U p = pinch off voltage Up R U GS> U th ein Drain R Gate U GS Source U DS aus UE UA U GS< U th U DS Die Schalterzustände ’ein’/’aus’ werden durch die Zustände Transistor aus (UGS < Uth) und Transistor ein (UGS > Uth) mit dem Schnitt der Widerstandsgeraden realisiert. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:57 MOS-FET als Schalter Für UGS < Uth ist die Drain-Source-Strecke gesperrt. Mit dieser Spannung wird der Transistorschalter ausgeschaltet. Der Schnittpunkt der Kennlinie für UGS < Uth mit der Widerstandsgeraden für R ist der Arbeitspunkt des Schalterzustandes ’aus’. Mit einer Spannung UGS > Uth wird die DrainSource-Strecke leitend, der Transistor eingeschaltet. Die Gate-Source-Spannung wird wie beim bipolaren Transistor so gewählt, daß die zugehörige Kennlinie von der Widerstandsgeraden für R im linearen Bereich geschnitten wird. Dieser Schnittpunkt ist der Arbeitspunkt des Schalterzustandes ’ein’. Wechselt die Gate-Source-Spannung zwischen UGS < Uth und UGS > Uth, dann schaltet der Transistor zwischen gesperrt und leitend bzw. UDS zwischen UA und UE. Der Vorteil von MOS-FETs als Schalter gegenüber bipolaren Transistoren besteht darin, dass sie leistungslos am Gate angesteuert werden können. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:58 Kenngrößen Signalpegel: Es werden Pegelbereiche eingeführt, die die Werte der binären Schaltvariablen darstellen. Dadurch werden die Einflüsse der Störspannung berücksichtigt. Für die Zuordnung der Pegelbereiche zu den Werten der binären Schaltvariablen gibt es zwei Möglichkeiten: • Positive Zuordnung: • Negative Zuordnung: Der typische statische Störabstand USS ergibt sich aus der Differenz der Ausgangsspannung des steuernden Schaltgliedes zur Eingangsschwellspannung UES des angesteuerten Schaltgliedes. • bei H-Pegel: USSH = UAH - UES • bei L-Pegel: USSL = UES - UAL Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:59 Kenngrößen Pegelbereiche: Ausgang A U H-Pegel U U H-Pegel AH min AH U U AH min U AS U U U ES EL max AL max AL max L-Pegel AL EH min AS U U U Eingang E L-Pegel U U U EL EL maxU ES U EH min U EH Meist werden ’worst-case’ Störspannungsabstände definiert: bei H-Pegel: bei L-Pegel: Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:60 Kenngrößen Signalübertragungszeit: Elektronische Schalter benötigen Zeit, um von einem Schaltzustand in den anderen zu gelangen. Hauptursache für diese Zeitverzögerung ist die kapazitive Eigenschaft der Bauelemente; beim bipolaren Transistor hauptsächlich der Basis-Emitter pn-Übergang, beim unipolaren Transistor die Gate-Oxid-Substrat Schichtfolge (MOS-Kondensator). Die eigentlichen Signalübergangszeiten (Transition time) der Impulsflanken liegen zwischen 90% und 10% der Amplitude. idealer Rechteckimpuls am Eingang U H L t t p T p t p T p Pulsdauer Pulsperiode linearisierter Ausgangsimpuls U H 90% 10% t L t t THL Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik t t TLH THL TLH Transition Time H->L Transition Time L->H HWR · K4 Nr.:61 Kenngrößen Signallaufzeit: Die Signallaufzeit (Propagation delay time) gibt die Impulsverzögerung zwischen Eingangs- und Ausgangspegel an (tPHL bzw. tPLH). Die Messung der Signallaufzeiten wird auf die 50% Marke der Amplitude bezogen, die zwischen dem H- und dem L-Pegel liegt. Als mittlere Signallaufzeit eines Schaltgliedes wird definiert: Eingang U H 50% t L Ausgang U H 50% t L t PHL Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik t PLH HWR · K4 Nr.:62 Verknüpfungsglieder: unipolare MOS-FETs Complementary MOS (CMOS) Technik: Verknüpfungsglieder werden in dieser Technologie aus (selbstsperrenden) NMOS- und PMOS-Transistoren aufgebaut. Inverter U U B U B B p-Kanal MOS-FET gesperrt T T 1 E E T 1 1 0 1 0 1=U B gesperrt T T 2 2 T 2 n-Kanal MOS-FET Es ist stets ein Transistor gesperrt und der andere leitend. Daher ist der Betriebsstrom und die statische Verlustleistung nahezu Null. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:63 Verknüpfungsglieder: MOS-FETs NAND U NOR B U B A A B B A A B B Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:64 4.4 Zeitliches Verhalten von Schaltnetzen Bei den bisherigen Betrachtungen wurde die Funktion eines Schaltnetzes ständig, d.h. ohne Verzögerung, ausgeführt. Jedes Signal, welches ein Gatter durchläuft, hat jedoch eine kurze, nicht vernachlässigbare Laufzeit. Diese wird durch die technologische Realisierung der Gatter hervorgerufen. Trägheitseffekte: Insbesondere weisen Gatter auch Trägheitseffekte auf. Diese führen dazu, dass Signaländerungen am Eingang nur dann am Ausgang wirksam werden, wenn sie eine gewisse Dauer überschreiten. Kurze Signaländerungen werden verschluckt. Modellierung zeitlichen Verhaltens: Viele Fehler in Schaltnetzen sind mit formalen Methoden nicht oder nur schwer zu erkennen und resultieren vor allem aus dem oben beschriebenen zeitlichen Verhalten (Verzögerung, Absorbtion) der Gatter. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:65 Zeitliches Verhalten von Schaltnetzen Schaltungen (z.B. in eingebetteten Systemen) funktionieren nur dann richtig, wenn das Schaltnetz das Ergebnis innerhalb eines bestimmten Zeitintervalls berechnet hat. Die Verzögerungszeit von Schaltnetzen lässt sich anhand von Modellen vorhersagen und optimieren. Mit diesen Modellen kann die Schaltung auch simuliert werden. Für eine Messung wird ein Prototyp benötigt (Herstellung ist jedoch teuer und zeitaufwendig). Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:66 Modellierung des zeitlichen Verhaltens I a b c d e Gatter T f ideal, Laufzeitglied verzögerungsfrei Die Verzögerungszeit ist abhängig von: Typ des Übergangs Gattertyp (intrinsic delay) Last (load) am Ausgang (extrinsic delay) Die Last kann entweder durch andere Gatter (Cload) oder auch durch längere Leitungen (Wload) hervorgerufen sein. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:67 Modellierung des zeitlichen Verhaltens II Die Verzögerungszeit ist abhängig vom Umladewiderstand (Innenwiderstand des geschlossenen Transistors Ri) und der Belastung durch die Wire-Kapazität und Gate-Kapazität des nächsten Gatters. Eine gute Näherung für die Dauer des Umladevorgang ist die Zeitkonstante des RC-Gliedes. UB IE Ri S CWire UA CLoad Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:68 Modellierung des zeitlichen Verhaltens III Weiter abstrahiert ist die Verzögerungszeit abhängig von: Bei einer Konstruktion (Schematic) ist zunächst nur die Anzahl der Gatter am Ausgang (Cload) bekannt. Wload wird geschätzt. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:69 Standardzellenbibliothek ECPD15 NAND4-Gatter: Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:70 Kritischer Pfad Eine obere Abschätzung für die Verzögerungszeit einer kombinatorischen Schaltung liefert die Bewertung der Laufzeit über den kritischen Pfad: Annahme: Jedes Gatter hat eine einheitliche Verzögerung, die Verzögerung auf den Leitungen werde vernachlässigt. Dann ist der kritische Pfad der längste Pfad, der von den Eingängen bis zum Ausgang der Schaltung durchlaufen werden kann. & & & & = & & = =1 Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:71 n-Bit Ripple-Carry-Addierer Der kritische Pfad hat eine Länge von n*tk(VA) Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:72 Carry-Select-Addierer an-1 bn-1 an/2 bn/2 0 Ziel: Beschleunigung der Durchlaufzeit Der kritische Pfad hat eine Länge von n/2*tk(VA)+tk(MUX) n/2-Bit-Addierer an/2-1 bn/2-1 s‘n-1 an-1 bn-1 a0 b0 0 s‘n/2 n/2-Bit-Addierer an/2 bn/2 1 n/2-Bit-Addierer s“n sn/2-1 s0 s“n/2 coutn/2-1 sn-1 sn/2 Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:73 Träges Laufzeitglied Bei den bisherigen Betrachtungen wurde der Verzögerungseffekt T durch ein ideales Laufzeitglied ausgedrückt. Ein träges Laufzeitglied ist ein nichtideales Laufzeitglied, bei dem die Trägheitseffekte berücksichtigt werden. Sei x(t) ein ereignisdiskretes Signal der Form: Ein träges Laufzeitglied läßt sich wie folgt beschreiben: Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:74 Träges Laufzeitglied T LH x(t) T HL T HL <T ideales Laufzeitglied träges Laufzeitglied t Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:75 4.5 Hazards (Gefahr) in Schaltnetzen Hazards stellen eine weitere wichtige Fehlerquelle dar. Beispiel: Für b = 1 und c = 1 ist unabhängig von a die Funktion f = 1. Bei einem Wechsel von a (0 → 1 oder 1 → 0) und unterschiedlichen Gatterlaufzeiten T2 und T3 springt der Funktionswert kurzzeitig auf 0 und im Anschluss wieder auf 1. Dieses Verhalten wird Hazard (Risiko, Gefahr) genannt. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:76 Hazards Statische Hazards: Ein statischer Hazard liegt vor, wenn der Ausgang konstant bleiben sollte, aber kurzzeitig einen anderen Wert annimmt. Ein statischer 0-Hazard liegt vor, wenn der Ausgang eigentlich konstant 0 sein sollte; ein statischer 1-Hazard liegt vor, wenn der Ausgang konstant 1 sein sollte. Statischer 1-Hazard Statischer 0-Hazard Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:77 Hazards Dynamische Hazards: Ein dynamischer Hazard liegt vor, wenn der Ausgang bei einem Übergang vor dem Einstellen auf den endgültigen Wert noch einige Male andere Werte annimmt. Ein dynamischer 0-1-Hazard liegt vor, wenn dies beim Wechsel von 0 nach 1 geschieht; ein dynamischer 1-0-Hazard liegt vor, wenn dies beim Wechsel von 1 nach 0 geschieht. Dynamischer 0-1-Hazard Dynamischer 1-0-Hazard Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:78 Beispiel Dynamischer 0-1-Hazard Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:79 Hazards Funktionshazards: Funktionshazards sind schaltungsunabhängige Eigenschaften einer Booleschen Funktion. Sie treten auf, wenn sich mehrere Eingänge nicht gleichzeitig, sondern nacheinander ändern. Eine Boolesche Funktion f (x1, …, xn) hat einen statischen Funktionshazard für den Übergang von X1 = (x11 ; : : : ; x1n) nach X2 = (x21, …, x2n ), wenn: Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:80 Funktionshazards Erkennen von Funktionshazards im KV-Diagramm: x1 1 0 0 1 x2 x4 x3 Funktionshazards lassen sich nur durch Änderung der Booleschen Funktion vermeiden. Man kann jedoch auch dafür sorgen, dass die Änderung der Eingangsvariablen in einer bestimmten Reihenfolge geschieht. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:81 Schaltungshazards Schaltungshazards (auch: logische Hazards) entstehen durch die Signallaufzeiten in einzelnen Gattern einer Implementierung. Definition: Ein Schaltungshazard in einem Schaltnetz S, welches die Boolesche Funktion f realisiert, liegt vor, wenn: 1. f keinen Funktionshazard für den Übergang a → b besitzt 2. während des Wechsels von a nach b am Ausgang von S ein Hazard beobachtbar ist. Uwe Brinkschulte Eingebettete Systeme Lars Hedrich Entwurfsmethodik HWR · K4 Nr.:82