Hardwarearchitekturen und Rechensysteme

Werbung

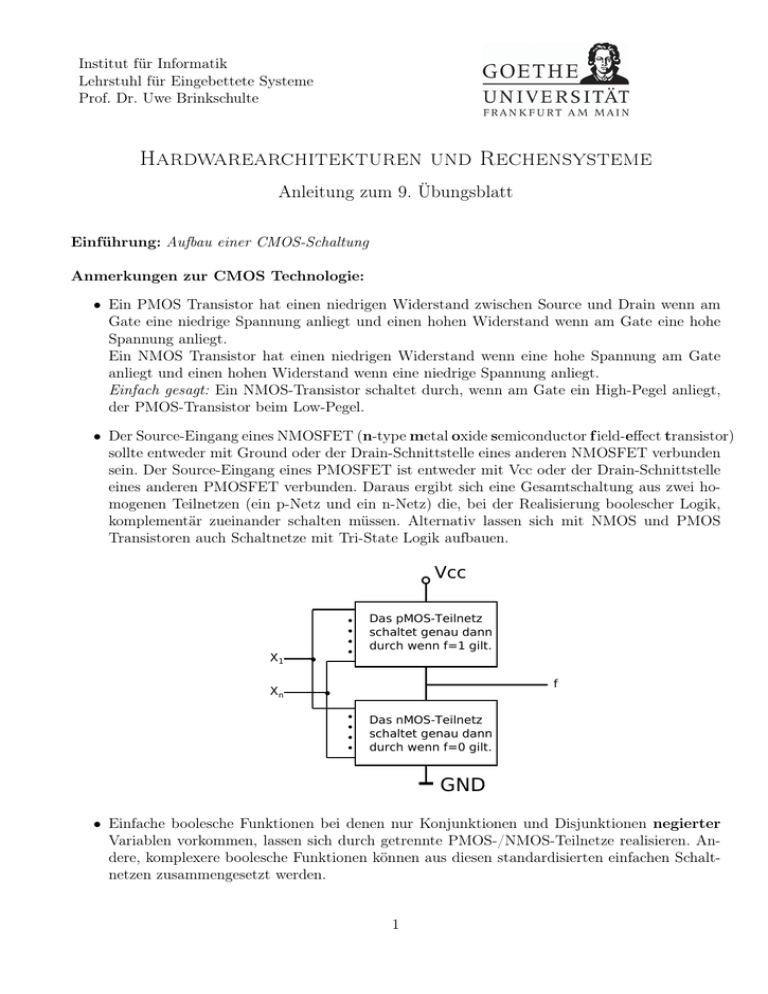

Institut für Informatik Lehrstuhl für Eingebettete Systeme Prof. Dr. Uwe Brinkschulte Hardwarearchitekturen und Rechensysteme Anleitung zum 9. Übungsblatt Einführung: Aufbau einer CMOS-Schaltung Anmerkungen zur CMOS Technologie: • Ein PMOS Transistor hat einen niedrigen Widerstand zwischen Source und Drain wenn am Gate eine niedrige Spannung anliegt und einen hohen Widerstand wenn am Gate eine hohe Spannung anliegt. Ein NMOS Transistor hat einen niedrigen Widerstand wenn eine hohe Spannung am Gate anliegt und einen hohen Widerstand wenn eine niedrige Spannung anliegt. Einfach gesagt: Ein NMOS-Transistor schaltet durch, wenn am Gate ein High-Pegel anliegt, der PMOS-Transistor beim Low-Pegel. • Der Source-Eingang eines NMOSFET (n-type metal oxide semiconductor f ield-effect transistor) sollte entweder mit Ground oder der Drain-Schnittstelle eines anderen NMOSFET verbunden sein. Der Source-Eingang eines PMOSFET ist entweder mit Vcc oder der Drain-Schnittstelle eines anderen PMOSFET verbunden. Daraus ergibt sich eine Gesamtschaltung aus zwei homogenen Teilnetzen (ein p-Netz und ein n-Netz) die, bei der Realisierung boolescher Logik, komplementär zueinander schalten müssen. Alternativ lassen sich mit NMOS und PMOS Transistoren auch Schaltnetze mit Tri-State Logik aufbauen. Vcc X1 Das pMOS-Teilnetz schaltet genau dann durch wenn f=1 gilt. f Xn Das nMOS-Teilnetz schaltet genau dann durch wenn f=0 gilt. GND • Einfache boolesche Funktionen bei denen nur Konjunktionen und Disjunktionen negierter Variablen vorkommen, lassen sich durch getrennte PMOS-/NMOS-Teilnetze realisieren. Andere, komplexere boolesche Funktionen können aus diesen standardisierten einfachen Schaltnetzen zusammengesetzt werden. 1 Schaltungsanalyse: Die Schaltung für die Funktion h hat 6 verschiedene Eingänge für Variablen: • Wenn der PMOS- und der NMOS-Teil komplementär zueinander schalten ist die Funktion h durch ein Teilnetz bereits vollständig spezifiziert. • Jeder Pfad von Vcc zum Ausgang der Schaltung h stellt einen Term dar, der die Funktion in positiver Logik1 auf 1 setzt. • Von Vcc beginnend spalten sich drei Pfade ab, von denen sich der erste in zwei weitere Pfade spaltet. Insgesamt gibt es also vier Terme. • Da ein PMOSFET bei einer anliegenden Null am Gate durchschaltet ergeben sich von rechts beginnend folgende Terme: – g – Damit der mittlere Pfad durchschaltet müssen beide Gatter durchschalten. Dies entspricht der Konjunktion e ∧ f – Der linken Pfad beginnt mit einem Gatter an dem a anliegt und spaltet sich in zwei Pfade auf. Um einen leitenden Pfad von Vcc über a nach h zu erhalten, muss nur eines der beiden nachfolgenden Gatter b oder c durchschalten. Diese parallele Anordnung entspricht der Disjunktion von b und c. Der linke Abschnitt des PMOS-Teilnetz hat also folgende Funktion: a ∧ (b ∨ c) = ab ∨ a c – Insgesamt ergibt sich für h also folgende Funktion: h(a, b, c, e, f, g) = ab ∨ a c ∨ ef ∨ g 1 In positiver Logik wird die boolesche 1 durch einen hohen Spannungspegel dargestellt. 2 Schaltungsaufbau: Es gibt eine algorithmische Herangehensweise um ein fehlendes Teilnetz in komplementärer Logik aufzubauen. Bei der obigen Beispielschaltung fehlt das NMOS-Teilnetz. Dieses Teilnetz soll genau dann durchschalten wenn h = 0 gilt. Daher wird als erstes eine boolesche Umformung benötigt um die Schaltfunktion h aufzustellen. Aus h(a, b, c, e, f, g) = ab ∨ a c ∨ ef ∨ g folgt h = g ∧ (e ∨ f ) ∧ (a ∨ (c ∧ b)). Jetzt gelten ähnliche Regeln wie beim PMOS-Teilnetz: da der Term g mit den restlichen Termen durch ein ∧ verbunden ist wird er "in Reihe" geschaltet. Wenn die Schaltfunktion des NMOSTeilnetz h durchschalten soll, muss der NMOS Transistor mit g am Gate leiten. Dies gilt auch für den nächsten Term (e ∨ f ). Intern steht hier eine Disjunktion. Also muss nur einer der beiden inneren Teilterme (e oder f ) leitend sein, damit ein Pfad entsteht. Die NMOS Transistoren der Variablen e und f werden also parallel angeordnet. Beim letzten Teilterm a∨(c∧b) muss diese Regel rekursiv angewendet werden. Der Teilterm selbst ist konjunktiv mit dem Restlichen Ausdruck verbunden, steht also in Reihe. Intern ist a disjunktiv mit (b∧c) verbunden, wird also parallel angeordnet. Der Ausdruck (b∧c) ist wiederum eine Konjunktion und wird hintereinander geschaltet. 3 Zusammenfassend lässt sich sagen: • Das PMOS Teilnetz soll für genau die Variablenbelegungen von Vcc zum Schaltungsausgang durchschalten, bei denen die Schaltfunktion 1 ist. • Ein PMOSFET schaltet durch, wenn am Gate eine 0 anliegt und sperrt bei einer 1. • Ein NMOSFET schaltet durch, wenn am Gate eine 1 anliegt und sperrt bei einer 0. • Das NMOS Teilnetz soll für genau die Variablenbelegungen von GND zum Schaltungsausgang durchschalten, bei denen die Schaltfunktion 0 ist. Diese Variablenbelegungen sind identisch zu den 1 Stellen der Negation der Schaltfunktion. 4