Aufbau eines Taschenrechners siehe Skizze Aufbau einer Waage

Werbung

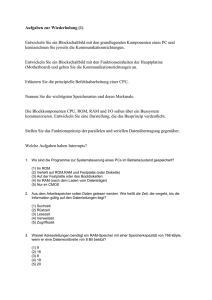

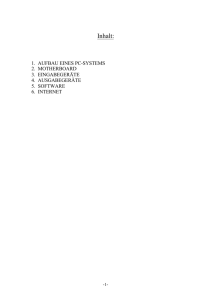

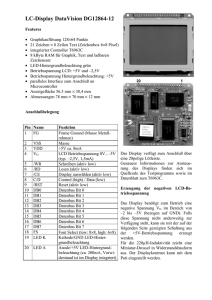

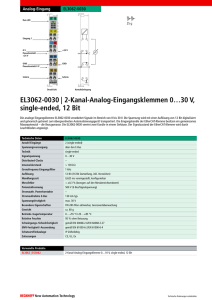

Aufbau eines Taschenrechners siehe Skizze Aufbau einer Waage siehe Skizze Speichermöglichkeit Speichermöglichkeit Adressbus 65536 (216) (2 wegen der Zustände 0=aus und 1=an) => 65536 Möglichkeiten => 65536 x 1Byte (8 Bit) (sprich 1 Byte entspricht 8 Bit) => : 1024 entspricht 210 => = 64 kiByte Bsp.: 24 => 16 mögliche Zustände 1 2 3 4 0 0 . . . 0 1 . . . 1 1 . . . 0 0 . . . Begriffe: ROM (Read Only Memory) RAM (Random Access Memory) Mikrocomputer Baugruppen: CPU-Mikroprozessor ➔ Steuerwerk (regelt die Abläufe) ➔ Rechenwerk (eigentliche Berechnung) ➔ Register (interner Speicher mit eigener Verwaltung) Speicheradresse ➔ ROM (Lesespeicher) ➔ RAM (Schreib- & Lesespeicher) Eingabegruppe ➔ Eingabe von Daten, wenn IN-R und Adresse dieser Baugruppe gesetzt ist. Ausgabegruppe ➔ Ausgabe von Daten auf den Datenbus, wenn OUT-W und die Adresse dieser Baugruppe gesetzt ist. BUS-System Beim Computer nutzen viele Baugruppen zum Datentransport das selbe Leitungsbündel. Nach ihrer Ausgabe unterscheidet man verschiedene Busse, die zusammengefasst als Systembus bezeichnet werden. 1. Adressbusses 2. Datenbus 3. Steuerbus 4. Spannungsversorgung Hinweis: Das Steuerwerk regelt die zeitliche Reihenfolge des Datenverkehrs auf dem Bus und ordnet die Daten auch der richtigen Baugruppe zu. Adressbus ➔ Steuerbus Verbindung Steuerwerk des Prozessors zu den Steueranschlüssen der Baugruppen. Steuersignale: ● MEM R memory read (Speicher lesen) ● MEM W memory write (Speicher schreiben) ● IN R Input read (Eingabeport lesen) ● OUT W Output write (Ausgabeport schreiben) Wenn die CPU kein Steuersignal ausgibt, sind die acht Datenanschlüsse aller Baugruppen elektronisch vom Bus getrennt (hochohmig). In jedem Fall muss der Prozessor die gültige Adresse und gleichzeitig das betreffende Steuersignal senden, um eine bestimmte Funktion zu erfüllen. Der Steuerbus besitzt einen Treiber (Bustreiber) mit Tristate-Ausgang. alle Steuerbefehle sind 0-aktiv z.B. ( INR ) 1/0/hochohmig IN R bei 1 = +5V ist Spannung am Widerstand 0V; kein Strom ●bei 0 = 0V ist Spannung am Widerstand 5V; geringer Strom fließt (da R sehr groß) ●bei Trennung von IN R (hochohmig) bewirkt Wdst. dass an Leitung 1 = +5V anliegt => kein Steuerbefehl bzw. Schaltung abgeschalten! ●Die pull-up Widerstände sorgen dafür, dass auf allen Steuerleitungen ein 1 – Signal anliegt (...inaktiv!...), wenn die Ausgänge hochohmig sind. ● Für den Fall, das die Ausgänge hochohmig sind, sorgen pull up – Widerstände dafür, dass auf allen Steuerleitungen ein 1-Signal anliegt -> also inaktiv sind. Zeitmultiplex Verfahren Daten-/Adressbus CPU (Ausschnitt) CPU Ausschnitt Befehlszähler Programmzähler Adressregister A0 A15 A15 interner Datenbus Adres sbust reibe r A8 Daten- u. Adressentreiber D0 - D4 A0 - A7 Prinzipschaltbild D0 D0 =>Daten/Adr. A0 A0 =>Daten/Adr. Multiplexer Demultiplexer Das Zeitmultiplex-Verfahren hilft hier, Anschlüsse des SIP-Gehäuses der CPU zu sparen. Es werden an den Anschlüssen AD0-AD7 (8 Anschlüsse) zu einem Zeitpunkt die acht Datenleitungen des Datenbusses geschalten und zu einem anderen Zeitpunkt die ersten acht Adressleitungen der 16 Leitungen breiten Adressbusses. Ohne das Multiplex-Verfahren wären 16 Adressleitungsanschlüsse plus acht Datenleitungsanschlüsse notwendig. ∑ 24 Anschlüsse Halbleiterspeicher Statischer RAM (Flipp-Flopp) Dynamischer RAM (Kondensatoren) Allen Halbleitern ist gemeinsam, dass durch Anlegen einer bestimmten Adresse der gewünschte Speicherplatz zum Lesen oder Schreiben ausgewählt werden kann (wahlfreier Zugriff) Kapazität des Speichers Speicherkapazität = Adressanzahl x Datenwortlänge ➔ Erweiterung des Speichers (wortorganisierter Speicher) A0 A0 A9 RAM 1k*8 1C2 1EN G1 A15 A11 RAM 1k*8 RAM 1k*8 1C2 1EN G1 1C2 1EN G1 RAM 1k*8 1C2 1EN G1 A10 1C2 ... Write 1EN ... Read G1 ... Baussteinauswahl WE ... Schreib-/Lese-Eingang & 0 bei A10=0, A11=0 & WE Freigabe 0 bei A10=0, A11=1 & 0 bei A10=1, A11=0 & 0 bei A10=1, A11=1 A B C Ausgang 0001 0011 0101 0111 1001 1011 1101 1110! A B & C da Ausgabe 0, muß G1 negiert werden A11 A10 Der Mikroprozessor – Innere Funktionen und Befehle - Befehle setzen sich aus mindestens einem höchstens drei Worten (je 8 Bit) zusammen ➔ Der Prozessor 8085 kennt über 90 verschiedene Befehle -> siehe Befehlsliste ➔ Befehle lassen sich in folgende Gruppen unterteilen 1) Transportbefehle 2) Verarbeitungsbefehle 3) Programmsteuerbefehle Befehle: z.B.: NOP Hexa: 00 --> no operation 84 Hexa bedeutet binär 1000 0100 Schreibweise ADD H --> addiert Transportbefehle ➔ Daten aus externen Speicher in ein Register (Speicherzeile innerhalb der CPU) des Prozessors lesen ➔ Daten aus der Eingabebaugruppe in den Akku (wichtiger Register) laden ➔ Daten aus dem Akku (z.B. Ergebnisse einer Bearbeitung) in eine Ausgabegruppe leiten ➔ siehe Blockschaltbild Verarbeitungsbefehle ➔ Veranlassen die ALU (Arithmetic Logic Unit) Rechenoperationen der logischen Verknüpfungen auszuführen ➔ z.B. Rechenoperationen: ➔ Addieren Subtrahieren Inkrementieren(+1) Dekrementieren(-1) Komplement bilden Dezimalkorrektur vornehmen (--> keine Multiplikation) ➔ Logische Verknüpfungen: UND, ODER, Exklusiv ODER Vergleichsoperationen ➔ UND => beide Leitungen 1 dann Ausgang 1 ➔ ODER => eine von beiden Leitungen mindestens 1 dann Ausgang 1 ➔ Exklusiv ODER => eine Leitung 0 eine 1 dann Ausgang 1 sind beide gleich sprich 0 oder 1 dann Ausgang 0 ➔ Die ALU kann stets nur mit maximal zwei Operanden verknüpft werden (Akku, Zwischenregister) ➔ Das Ergebnis gelangt immer in den Akku Programmsteuerbefehle ➔ Nach dem Einschalten des Rechners nimmt dieser seine Arbeit mit dem aussenden der Adresse 000016 auf. ➔ Dann wird das Ablaufsteuersignal ➔ Im Ergebnis liegt auf dem Datenbus der Inhalt der Speicherzelle 0000 16 ➔ Befehlsregister empfängt die Daten und das Datenwort wird dem Befehlsdecoder zum Entschlüsseln zugeleitet. ➔ Weiterer Ablauf ist nun von den gelesenen Befehl abhängig ➔ MEMR (Speicher lesen) gesendet. Das Zustandsregister (Flag-Register) 5 Flags existieren -> Carry Flag: -> Parity Flag: -> Hilfscarry Flag: -> Zero Flag: -> Vorzeichen Flag: (Hochwertigstes meldet Rechenübertrag Anzahl der „1“ Signale im Akku gerade Übertrag vom Bit3 nach Bit4 fand im Akku statt Es liefert 1-Signal, wenn nach dem Befehl der Akkuinhalt 000000002 ist. Bit7 ist „1“ Bit) Stapelspeicher (Stack) oder Stapelzeiger ➔ verwaltet den Speicherbereich im RAM (außerhalb der CPU) -> Anwendung hauptsächlich bei Unterprogrammen ➔ Im Stack liegen Stapelweise die Rückkehradressen ins Hauptprogramm -> Reihenfolge last in – first out Der Stapelzeiger ist ein 16 Bit – Register, das die aktuelle RAM-Adresse des Stapelspeichers enthält. Assembler Programmierung Bsp (Taschenrechner).: ADDITION einer eingegebenen Zahl mit 17810 => B216 Entwicklung Programm: Speicheradresse 000016 000116 000216 000316 000416 000516 000616 000716 000816 Mnemonik/Operant Maschinencode In/01 DB16 (1101 10112) 0116 (0000 00012) ADI/B2 C616 (1100 01102) B216 (1011 00102) OUT/01 D316 (1101 00112) 0116 (0000 00012) JMP/0000(Speicheradresse) C316 (1100 00112) 0016 (0000 00002) 0016 (0000 00002) ersten vier bin Zahlen=erster Maschinencodewert zweiten vier bin Zahlen=zweiter Maschinencodewert Bei einem JumpBefehl JMP wird auf eine Speicheradresse verwiesen. besteht aus insgesamt drei Befehlen, da Speicheradresse aus zwei mal 00 besteht benötigt sie 2x 8 Bit da 2 Hexa-Zahlen als Adresse für die Speicheradressierung benötigt werden brauch man 16 Bit in binärer Form. Da nur 8 Bit zu Verfügung stehen, wird diese über zwei 8 Bit Befehle adressiert.=> 1. Jump-Befehl 2. Adressierung 00 (erster Adressteil der Speicherzelle) 3. Adressierung 00 (zweiter Adressteil der Speicherzelle) Ausbildungsmitschrift bereitgestellt von Michael Bergler: http://michas-blog.diewebservisten.de