schaltungen intel

Werbung

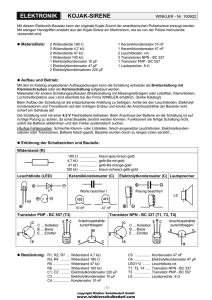

x TEAM GENESYS Aufgabe 4 Intel Leibnitz Challenge ù08 Digitale Schaltungen Elektronik entscheidet logisch ò A und B oder nicht C? |1 Inhalt INHALT 2 Intel Leibnitz Challenge '08 Aufgabe TEAM GENESYS AUFGABE A: GRUNDLAGEN DIGITALER SCHALTUNGEN ...................................... 3 A1) Grundlegende Informationen zu verschiedenen Logikgattern ......................................... 3 A2) ODER-Verknüpfung aus UND-Gattern und Invertern..................................................... 4 A2a) Schaltplan .................................................................................................................... 4 A2b) Logiktabelle................................................................................................................. 4 A3) Beschreibung der Funktion eines zweifach Multiplexers................................................. 4 AUFGABE B: SCHALTUNGSANALYSE UND OPTIMIERUNG .................................... 5 B1) Schaltung 4B1................................................................................................................... 5 B2) Schaltung 4B2................................................................................................................... 5 B2a) Logiktabelle................................................................................................................. 5 B2b) Funktion der Schaltung ............................................................................................... 5 B2c) Vereinfachung der Schaltung ...................................................................................... 6 AUFGABE C: ENTWICKLUNG EINER EINFACHEN DIGITALSCHALTUNG .............. 7 C1) 1-Bit Zähler....................................................................................................................... 7 C1a) Schaltplan .................................................................................................................... 7 C1b) Beschreibung der Funktion ......................................................................................... 7 C1c) Aufbau und Dokumentation ........................................................................................ 7 C2) 4-Bit Zähler....................................................................................................................... 8 C2a) Schaltplan .................................................................................................................... 8 C2b) Beschreibung der Funktion ......................................................................................... 8 C2c) Aufbau und Dokumentation ...................................................................................... 10 |2 Aufgabe A: Grundlagen digitaler Schaltungen A1) Grundlegende Informationen zu verschiedenen Logikgattern Intel Leibnitz Challenge '08 Aufgabe TEAM GENESYS Anzahl der Eingänge Anzahl der Ausgänge Funktion als Gleichung Wahrheitstabelle Schaltsymbol gemäß Europäischer Norm AND-Gatter 2 OR-Gatter 2 XOR-Gatter 2 NOT-Gatter 1 1 1 1 1 Y = A ⋅B Y = A +B Y = A⊕B Y = −A A 0 0 1 1 A B B 0 1 0 1 & Y 0 0 0 1 Y A 0 0 1 1 A B B 0 1 0 1 Y 0 1 1 1 >=1 A 0 0 1 1 B 0 1 0 1 A B Y =1 Y 0 1 1 0 A 0 1 Y Y 1 0 1 A Y Neben diesen gibt es noch weitere zusammengesetzte Logikgatter z.B. die Zusammensetzung der verschiedenen Gatter mit einem NOT Gatter. Beim Schaltsymbol wird dabei lediglich ein Kreis hinter das Gatter gesetzt (vergleiche NOT Gatter). NAND-Gatter Anzahl der Eingänge 2 Anzahl der 1 Ausgänge Funktion als Y = − (A ⋅ B ) Gleichung Wahrheitstabelle A B Y 0 0 1 0 1 1 1 0 1 1 1 0 Schaltsymbol gemäß A & Y Europäischer Norm B NOR-Gatter 2 1 NXOR-Gatter 2 1 Y = − (A + B ) Y = − (A ⊕ B ) A 0 0 1 1 A B B 0 1 0 1 >=1 Y 1 0 0 0 A 0 0 1 1 Y A B B 0 1 0 1 =1 Y 1 0 0 1 Y |3 A2) ODER-Verknüpfung aus UND-Gattern und Invertern A2a) Schaltplan A 1 B 1 C E & 1 Y D Intel Leibnitz Challenge '08 Aufgabe TEAM GENESYS A2b) Logiktabelle A 0 0 1 1 B 0 1 0 1 C 1 1 0 0 D 1 0 1 0 E 1 0 0 0 Y 0 1 1 1 A3) Beschreibung der Funktion eines zweifach Multiplexers Ein Multiplexer (MUX) ist Gatter mit dem aus einer Anzahl von Eingangssignalen mithilfe eines Steuerstromsanschluss eines ausgewählt werden kann. Das Gegenstück zu einem Multiplexer ist ein Demultiplexer. Damit können die gebündelten Datenkanäle wieder aufgetrennt werden können. Ein n-Multiplexer hat 2n Eingänge, n Steuerstromanschlusse und einen Ausgang. Somit besitzt ein Zweifachmultiplexer 22 = 4 Eingänge, 2 Steuerstromanschlüsse und natürlich auch einen Ausgang. s0 e0 e1 e2 e3 s1 _ MUX 1 G1 V1 1 _ MUX 1 G1 V1 1 a _ MUX 1 G1 V1 1 2-MUX aufgebaut aus 1-MUX (zum besseren Verständnis) Schalttafel eines 2-MUX s1 s0 a 0 0 e0 0 1 e2 1 0 e1 1 1 e3 Wenn der Steuerstrom fließt wird der Wert des Eingang 1 verwendet, sonst der Wert des Eingangs „1 negiert“ Schaltfunktion als Gleichung: a = (e 0 ⋅ (− s 1 ) ⋅ (− s 0 )) + (e 1 ⋅ (− s 1 ) ⋅ s 0 ) + (e 2 ⋅ s 1 ⋅ (− s 0 )) + (e 3 ⋅ s 1 ⋅ s 0 ) |4 Aufgabe B: Schaltungsanalyse und Optimierung B1) Schaltung 4B1 Logiktabelle A 0 0 1 1 B 0 1 0 1 C 1 1 1 0 D 0 0 1 0 E 0 1 0 0 Y 0 1 1 0 Die Schaltung erfüllt die logische Funktion eines XOR-Gatters. Intel Leibnitz Challenge '08 Aufgabe TEAM GENESYS B2) Schaltung 4B2 B2a) Logiktabelle A 0 0 0 1 0 1 1 1 B 0 0 1 0 1 0 1 1 C 0 1 0 0 1 1 0 1 X 0 0 0 0 0 0 0 1 Y 0 1 1 1 0 0 0 1 Z 0 0 0 0 1 1 1 0 B2b) Funktion der Schaltung Die Schaltung gibt für eine bestimmte Anzahl von Eingängen, die Strom führen, jeweils eine bestimmte Kombination an den Ausgängen ab. Bei null Anschlüssen die Strom führen: 000 Bei einem Anschluss der Strom führt: 010 Bei zwei Anschlüssen die Strom führen: 001 Bei drei Anschlüssen die Strom führen: 110 |5 B2c) Vereinfachung der Schaltung 1. X gibt nur 1 aus, wenn an allen drei Eingängen 1 anliegt. Somit muss man nur ein AND Gatter einbauen. 2. Y gibt 1 aus, wenn an allen(AND) drei Eingängen 1 anliegt oder(OR) an genau einem(XOR) Eingang 1 anliegt. Dies kann man auch so ausdrücken: Y = OR (AND(A; B; C ); XOR (XOR (B; C ); A )) . Wenn man in die Kombination der zwei XOR Gatter die Kombination A = 1; B = 1; C = 1 ein gibt kommt auch 1 heraus. Somit kann man sich das AND Gatter (und das OR Gatter) sparen. ⇒ Y = XOR (XOR (B; C); A ) 3. Z gibt 1 aus, wenn zwei der drei Eingänge 1 führen. Hierzu haben wir keine Vereinfachung gefunden Intel Leibnitz Challenge '08 Aufgabe TEAM GENESYS So entsteht folgender Schaltplan: =1 Z |6 Aufgabe C: Entwicklung einer einfachen Digitalschaltung C1) 1-Bit Zähler Intel Leibnitz Challenge '08 Aufgabe TEAM GENESYS C1a) Schaltplan C1b) Beschreibung der Funktion Am XOR Gatter liegt am 1. Eingang 1 an und am 2. 0. Deshalb führt der Ausgang 1. Durch drücken des Tasters erhält der D-Flip-Flop einen Impuls und speichert daraufhin den Wert des Eingangs ab und gibt ihn am Ausgang aus. ⇒ LED leuchtet! Durch die Verbindung des Ausgangs des D-Flip-Flops mit dem 2. Eingang des XOR Gatters sendet der XOR Gatter 0 aus, da an beiden Eingängen 1 anliegt. Wenn der Taster nun wieder gedrückt wird, gibt der D-Flip-Flop den Wert 0 aus. ⇒ LED leuchtet nicht! C1c) Aufbau und Dokumentation 0 1 |7 C2) 4-Bit Zähler C2a) Schaltplan 4 4 Intel Leibnitz Challenge '08 Aufgabe TEAM GENESYS 2 4 2 3 3 & 08 4 4 4 & 4 & 08 08 C2b) Beschreibung der Funktion Die Schaltung muss in folgender Reihenfolge zählen: 1 10 11 100 101 110 111 1000 1001 1010 1011 1100 1101 1110 1111 Wie die Schaltung grundlegend funktioniert ist beim 1-Bit Zähler schon beschrieben. Hier beschreiben wir nur noch was neu ist. Insgesamt kann man sagen, dass man für jedes LED ein XOR Gatter benötigt an dessen 1. Anschluss der Wert des dazugehörigen D-Flip-Flop Ausgangs und am 2. ein AND Gatter an dessen Eingängen der Wert der vorherigen D-Flip-Flop Ausgänge angeschlossen ist. Dies ist darauf zurückzuführen, dass eine LED entweder nur leuchten soll, wenn alle vorherigen LED’s leuchten, da mit diesen vorherigen LED’s keine größere Zahl zustandegebracht werden kann, oder die LED im letzten Zählschritt leuchtete. Doch, wenn beides zutrifft muss die LED wieder ausgeschaltet werden, da nun alle bisherigen LED’s leuchten und somit die nächst höhere LED zu leuchten beginnt. LED 1: Wenn man die letzte Ziffer der Zählreihenfolge betrachtet stellt man fest, dass sie bei jedem Schritt umschaltet. In der Schaltung wird dies durch den das XOR Gatter U2/2 erreicht. Da 1 direkt mit dem Strom verbunden ist und bei 2 noch kein Strom anliegt, gibt das Gatter bei 3 das erste Mal 1 aus. Und bei Drücken des Tasters leuchtet die LED1 Beim zweiten Mal liegt an beiden Eingängen 1 an, da der D-Flip-Flop bei 2 nun Strom ausgibt, der am XOR Gatter bei 2 dann anliegt. Weil an beiden Eingängen Strom anliegt gibt das XOR Gatter 0 aus, wodurch die LED1 nach dem Drücken des Tasters nicht leuchtet. |8 Intel Leibnitz Challenge '08 Aufgabe TEAM GENESYS LED 2: Hier reicht es nicht es genauso zu machen wie bei LED1 d.h. einen Eingang direkt mit dem Strom und den anderen mit dem Ausgang des D-Flip-Flops zu verbinden, da sich die Ziffer nicht bei jedem Schritt ändert z.B. zwischen 10 und 11. Also ist bei dieser LED vor dem D-Flip-Flop ein XOR Gatter dessen Eingang 4 mit dem Ausgang 12 des D-FlipFlops (vgl. LED1) und dessen Eingang 5 mit dem Ausgang 2 des D-Flip-Flops verbunden ist. Daraus folgt, dass der D-Flip-Flop nur 1 ausgibt, wenn im vorherigen Zählschritt entweder LED2 (Ausgang 12 führt Strom) oder LED1 (Ausgang 2 führt Strom) geleuchtet hat (wenn beide leuchten natürlich nicht). Wenn man nun die Zählreihenfolge betrachtet erkennt man, dass dies stimmt. Zum Beispiel von 10 nach 11: Bei 10 leuchtet LED1 nicht dafür aber LED2. Somit leuchtet LED2 bei 11. LED 3: Hier reicht nicht einmal eine Schaltung wie bei LED2. Deshalb ist hier vor den Eingang 10 des XOR Gatters U2/3 ein AND Gatter U4/1 geschaltet. Dessen Eingänge 1 und 2 sind mit Ausgängen 2 und 12 des D-Flip-Flops verbunden. Der Eingang 9 des XOR Gatters ist mit dem Ausgang 15 des Flip-Flops verbunden. Daraus ergibt sich, dass die LED3 nur leuchtet (beziehungsweise der D-Flip-Flop bei 15 Strom aussendet) wenn im vorherigen Schritt entweder LED1 (Ausgang 2 führt Strom) und LED2 (Ausgang 12 führt Strom) oder LED3 (Ausgang 15 führt Strom) leuchten. Oder als Formel aus gedrückt XOR (AND(LED1 = 1; LED2 = 1); LED3 = 1) . An der Zahlenreihe kann man nun erkennen, dass die LED3 das erste mal leuchtet, nachdem die Zahl 11 leuchtete. Diese Situation entspricht dem AND Gatter und lässt sich noch mal nach 1011 erkennen. Nach dem ersten Mal (sowie nach 1011) leuchtet sie die nächsten Male weiter, da nun immer im vorhergehenden Schritt die LED3 leuchtet. Erst, wenn LED1 und LED2 auch leuchten schaltet sie wieder ab, da ein XOR Gatter und kein OR Gatter verbaut wurde. LED 4: Bei dieser LED kann man die beiden AND Gatter zusammennehmen und man erhält ein AND Gatter mit 3 Eingängen. Die drei Eingänge sind mit den Ausgängen der vorherigen D-Flip-Flops (von LED1 bis LED3) verbunden. Der Ausgang dieses AND Gatters wird mit einem Eingang des XOR Gatters verbunden. Am den Zweiten Eingang des XOR Gatters wird der Wert des D-Flip-Flop Ausgangs 16 angeschlossen. Die Formel lautet hier XOR (AND(LED1 = 1; LED2 = 1; LED3 = 1); LED4 = 1) . Somit schaltet sich die LED4 erst ein wenn alle anderen leuchten (AND Gatter/Eingang 12 in das XOR Gatter) und leuchtet danach weiter, da sie nun immer im vorherigen Schritt leuchtet (Eingang 13 in das XOR Gatter). |9 Intel Leibnitz Challenge '08 Aufgabe TEAM GENESYS C2c) Aufbau und Dokumentation 0000 0001 0010 0011 0100 0101 0110 0111 |10 Intel Leibnitz Challenge '08 Aufgabe TEAM GENESYS 1000 1001 1010 1011 1100 1101 1110 1111 |11