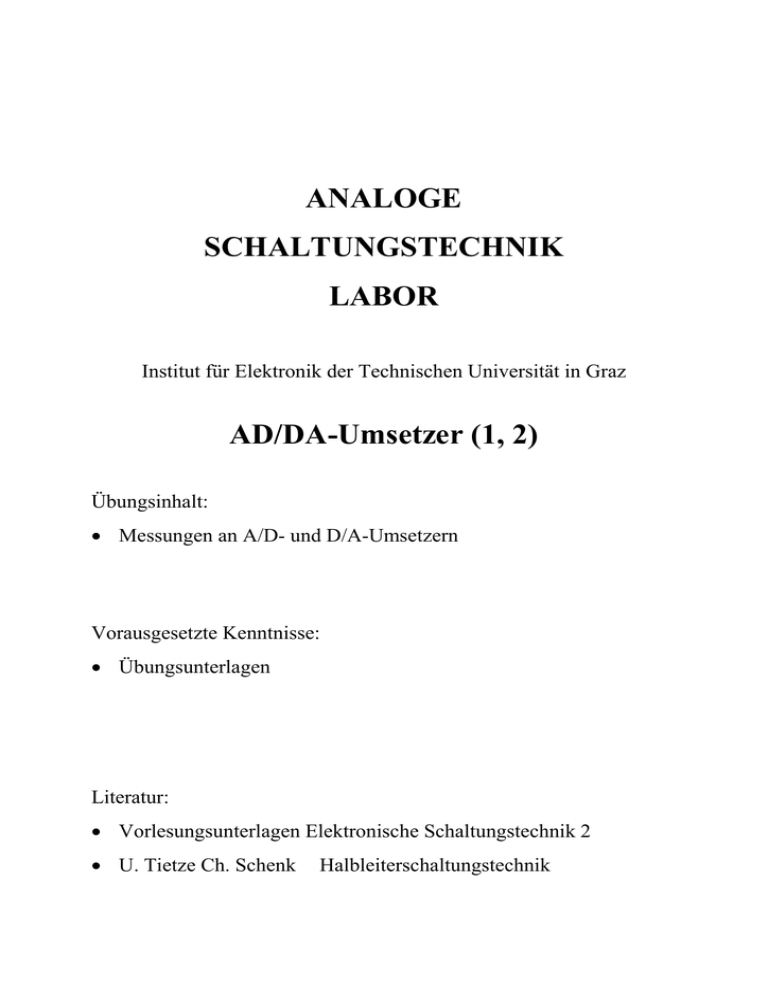

Analoge Schaltungstechnik Labor

Werbung

ANALOGE

SCHALTUNGSTECHNIK

LABOR

Institut für Elektronik der Technischen Universität in Graz

AD/DA-Umsetzer (1, 2)

Übungsinhalt:

• Messungen an A/D- und D/A-Umsetzern

Vorausgesetzte Kenntnisse:

• Übungsunterlagen

Literatur:

• Vorlesungsunterlagen Elektronische Schaltungstechnik 2

• U. Tietze Ch. Schenk

Halbleiterschaltungstechnik

AD1/AD2 – 1 / 22

1

1.1

Analog/Digital-Umsetzer

Aufgabe eines A/D-Umsetzers

Ein A/D-Umsetzer misst das Verhältnis einer analogen Eingangsgröße zu einer Referenzgröße

und gibt dieses in Form eines digitalen Wortes an. Dazu wird der mögliche Bereich der

Eingangsgröße in n gleich große Intervalle zerlegt und festgestellt, welchem Intervall die

Eingangsgröße zuzuordnen ist (Abbildung 1).

a

d

binär dezimal

a1

∆a

{

111

7

110

6

101

5

Der analoge Eingang

100

4

a0 < a < a1

011

3

010

2

wird auf eines der 8 möglichen

Kodewörter abgebildet. Die

Auflösung N ist 3 bit (N = 3 = ld 8)

001

1

000

0

a0

Quantisierung

Inkrement des Umsetzers:

∆a = a1/n = a1/2N

a1 ist häufig die

Referenzgröße

Kodierung

Abbildung 1: Umsetzerkennlinie

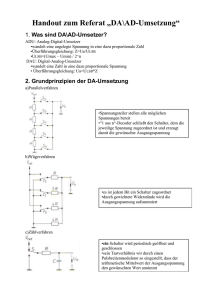

Die Umsetzung besteht somit grundsätzlich aus zwei Schritten:

Quantisieren und Kodieren. Man beachte, dass durch die Quantisierung ein Informationsverlust

entsteht, der nicht mehr rückgängig gemacht werden kann (Quantisierungsfehler).

Bei einem A/D-Umsetzer mit z.B. n = 8 Quantisierungsintervallen wird die Eingangsgröße durch

eines von 8 möglichen Codewörtern abgebildet. In diesem Fall hat der Umsetzer eine Auflösung

von:

N = ld n = 3 bit.

Oder: Bei N Bit Auflösung ergeben sich 2N Quantisierungsintervalle. Die analoge Größe des

LSB (Least Significant Bit, niederwertigstes Bit) errechnet sich aus der Auflösung und dem

vollen Eingangsbereich (FSR = Full Scale Range), d.i. die Differenz zwischen dem maximalen

und dem minimalen Eingangswert, nach der Formel:

1 LSB =

FSR

.

2N

Eine ebenfalls gebräuchliche Definition bezeichnet die Auflösung als die kleinste Änderung des

Eingangswertes, die der A/D-Umsetzer noch unterscheiden kann (kleinstmöglicher

Quantisierungsschritt, 1 LSB analog).

Der Ausgangscode eines A/D-Umsetzers ändert sich erst dann, wenn sich die Eingangsgröße um

den Betrag ±1/2 LSB, gerechnet von der Mitte des Quantisierungsintervalls, geändert hat. Die

Ausgabe 2002

AD1/AD2 – 2 / 22

Umsetzerkennlinie (Abbildung 2) ist also eine Treppenfunktion, die angenähert als eine durch

Null und den positiven Endwert (plus full scale) des Umsetzers verlaufende Gerade dargestellt

werden kann (ideale Kennlinie).

Zusammenhänge bei einem idealen A/D-Umsetzer

1

DIGITALER AUSGANG

(Kode und Bruchteil)

Idealer Übergang

7/8

111

6/8

110

5/8

101

4/8

100

3/8

011

2/8

010

1/8

001

Nominell quantisierter Wert

(+- 1/2 LSB)

1 LSB

Ideal umgesetzter

analoger Eingang

0

0

1/8

2/8

3/8

4/8

5/8

6/8

7/8

1/8

2/8

3/8

4/8

5/8

6/8

7/8

000

0

FSR

ANALOGER EINGANG

Abbildung 2: Ideale A/D-Umsetzerkennlinie

Bei bipolarem Betrieb verläuft die Gerade durch den positiven und den negativen Endwert

(minus full scale). Null bzw. der negative Endwert ist der analoge Eingangswert, der 1/2 LSB

unter dem Wert liegt, der die erste Änderung des Codes am Ausgang (von 000...00 auf 000...01)

bewirkt. Der positive Endwert liegt 3/2 LSB über dem Eingangswert, der den letzten

Codewechsel (von 111...10 zu 111...11) hervorruft. Abbildung 3 zeigt die Kennlinie eines

idealen bipolaren A/D-Umsetzers mit COB-Code (Complementary Offset Binary Code)

Ausgang.

Ausgabe 2002

AD1/AD2 – 3 / 22

Alle Bit gesetzt

000...000

DIGITAL AUSGANG - COB Code

COB:

Complementary

Offset Binary

Verstärkungsfehler

- 1/2 LSB

011...111

+ 1/2 LSB

Offsetfehler

111...111

Alle Bit gelöscht

- FSR/2

ANALOG EINGANG

0

+ FSR/2 - 1 LSB

Abbildung 3: Übertragungskennlinie eines idealen bipolaren A/D-Umsetzters

1.2

Genauigkeit von A/D-Umsetzern

Unter diesem Oberbegriff lassen sich die typischen Umsetzerfehler zusammenfassen.

Nachfolgend werden die grundlegenden Fehler von A/D-Umsetzern näher betrachtet.

1.2.1 Offsetfehler (Nullpunktfehler)

Der Offsetfehler ist als die Abweichung der tatsächlichen Übertragungsfunktion von der idealen

Kennlinie im Nullpunkt der analogen Eingangsgröße definiert. Er tritt als konstanter absoluter

Genauigkeitsfehler für jeden Punkt der Übertragungsfunktion auf (Abbildung 4) und kann daher

abgeglichen werden.

Eine andere Definition lautet:

Bezeichnet man als Offset die Eingangsgröße, die den ersten Codewechsel am Ausgang eines

A/D-Umsetzers verursacht , dann ist der Offsetfehler die Differenz zwischen dem realen und

dem idealen Übergangswert.

Liegt der Eingangsbereich zwischen Null und einem positiven Endwert (unipolarer Betrieb),

sollte bei einem idealen Umsetzer ein analoger Eingangswert von 1/2 LSB über Null den ersten

Codewechsel bewirken. Bei bipolarem Betrieb, bei dem sich der Umsetzerbereich von einem

negativen bis zu einem positiven Endwert erstreckt, sollte der erste Wechsel bei einem

Eingangswert erfolgen, der 1/2 LSB über dem negativen Endwert liegt.

Zur Unterscheidung der beiden Betriebsfälle werden auch die Begriffe unipolarer bzw. bipolarer

Offsetfehler verwendet.

1.2.2 Verstärkungsfehler

Die Kennlinie eines idealen A/D-Umsetzers weist bei einer sinnvollen Darstellung eine Steigung

von 45° auf. Ein Verstärkungsfehler (Skalierungsfehler) bewirkt eine von 45° abweichende

Steigung der realen Übertragungsfunktion (Abbildung 4). Seine Größe wird als Differenz

Ausgabe 2002

AD1/AD2 – 4 / 22

zwischen dem realen und dem idealen analogen Eingangswert ermittelt, der jeweils den letzten

Wechsel des Ausgangscodes (in Abbildung 4 auf 111) verursacht. Der ideale Wert liegt 3/2 LSB

unter dem nominalen positiven Skalenendwert (FSR). Ein eventuell vorhandener Offsetfehler ist

vorher abzugleichen. Der Verstärkungsfehler beeinflusst die Werte um denselben prozentualen

Betrag und kann, wie der Offsetfehler, abgeglichen werden.

Verstärkungsfehler

in %

Idealer

Umsetzter

Umsetzer mit Offsetund

Verstärkungsfehler

111

DIGITALER AUSGANG

110

101

Umsetzer

mit

Offsetfehler

100

011

010

001

000

0

1/8

Offsetfehler

2/8

3/8

4/8

5/8

6/8

7/8

FSR

ANALOGER EINGANG

Abbildung 4: A/D-Umsetzer Genauigkeit

1.2.3 Linearitätsfehler

Der (integrale) Linearitätsfehler eines A/D-Umsetzers ist die Abweichung seiner realen

Übertragungsfunktion von der idealen Kennlinie. Er wird im allgemeinen in LSB (analoger

Wert) angegeben.

Es bestehen grundsätzlich zwei Möglichkeiten, die Größe des Linearitätsfehlers zu bestimmen.

Bei der 1. wird davon ausgegangen, dass der Offset- und der Verstärkungsfehler so abgeglichen

sind, dass die Endpunkte der realen und der idealen Kennlinie übereinstimmen (EndpunktDefinition).

Bei der zweiten, seltener benutzten Möglichkeit erhält man durch Manipulation des Steigungsund/oder des Offsetfehlers eine im Hinblick auf den maximalen Linearitätsfehler optimale

Bezugsgerade (best straight line) oder eine möglichst gute Annäherung der realen an die ideale

Übertragungsfunktion (,,best-fit“-Form).

Der integrale Linearitätsfehler kann nicht abgeglichen werden.

1.2.4 Differenzielle Nichtlinearität (DNL)

Unter diesem Begriff erfasst man den Betrag der Abweichung jedes Quantisierungsergebnisses

von seinem theoretischen idealen Wert.

Ausgabe 2002

AD1/AD2 – 5 / 22

Anders ausgedrückt, die differenzielle Nichtlinearität ist die analoge Differenz zwischen zwei

benachbarten Codes von ihrem idealen Wert (1 LSB; weitere Bezeichnungen: Codebreite oder

,,quantum“). In Abbildung 5 zeigen die beiden ersten Quantisierungsschritte ein ideales

Verhalten. Der nächste Schritt beträgt statt 1 LSB (DNL = 0) nur 1/2 LSB, d.h. er ist um 1/2 LSB

zu klein (DNL = - 1/2 LSB). Der darauffolgende 3/2 LSB-Schritt ist dagegen um 1/2 LSB zu

groß (DNL = + 1/2 LSB).

Diese beiden Schritte kennzeichnen den Bereich, der für eine spezifizierte differenzielle

Nichtlinearität von ± 1/2 LSB gerade noch zulässig ist.

Man beachte, dass integrierende A/D-Umsetzer funktionsbedingt gleichförmige Codebreiten

haben, die sich nur langfristig merklich ändern können.

Die differenzielle Nichtlinearität kann nicht abgeglichen werden.

111

Digital-Ausgang

110

101

100

011

Q

2

010

3Q

+ 1/2 DNL

2

- 1/2 DNL

Q

001

0

Q = FSR/2N

1/8

3/8

5/8

Analog-Eingang

7/8 FSR

FS = FSR - 1 LSB

Abbildung 5: Differenzielle Nichtlinearität

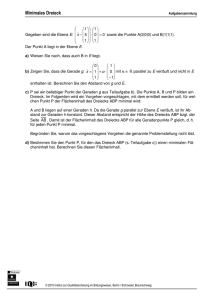

1.2.5 Monotonie, fehlendes Codewort (missing code)

Der Definition nach ist ein A/D-Umsetzer dann monoton, wenn die Wertigkeit seines

Ausgangscodes mit stetig steigender Eingangsgröße ebenfalls stetig steigt.

Ist die differenzielle Nichtlinearität eines A/D-Umsetzers größer als ± 1 LSB, so ist ein

monotoner Betrieb dieses Umsetzers nicht gewährleistet. Mit Sicherheit arbeiten die Umsetzer

monoton, die über eine differenzielle Nichtlinearität verfügen, die kleiner oder gleich 1 LSB ist

(Abbildung 6).

(b)

nichtmonotone Umsetzung

111

111

110

110

Digital-Ausgang

Digital-Ausgang

(a)

monotone Umsetzung

101

100

011

101

100

011

010

010

001

001

0

1/8

3/8

Analog-Eingang

5/8

7/8 FSR

FS = FSR - 1 LSB

0

1/8

3/8

Analog-Eingang

5/8

7/8 FSR

FS = FSR - 1 LSB

Abbildung 6: Monotonie der A/D-Umsetzung

Ausgabe 2002

AD1/AD2 – 6 / 22

Die Bedingung, dass kein möglicher Code übersprungen wird, verlangt eine differenzielle

Nichtlinearität von kleiner 1 LSB. Ist der Fehler größer oder gleich 1 LSB, so ist zu erwarten,

dass bei der Umsetzung fehlende Codes (missing codes) auftreten (Abbildung 7).

(b)

fehlender Code

111

111

110

110

Digital-Ausgang

Digital-Ausgang

(a)

kein fehlender Code

101

100

011

101

100

011

010

010

001

001

0

1/8

3/8

Analog-Eingang

5/8

0

7/8 FSR

FS = FSR - 1 LSB

Code fehlt

1/8

3/8

Analog-Eingang

5/8

7/8 FSR

FS = FSR - 1 LSB

Abbildung 7: Fehlender Code bei der A/D-Umsetzung

1.2.6 Quantisierungsfehler

Wie in Kapitel 1.1 bereits erwähnt wurde, haftet A/D-Umsetzern ein Quantisierungsfehler von

± 1/2 LSB an. Dieser Fehler ist eine grundsätzliche Eigenschaft des Quantisierungsprozesses und

kann nicht beseitigt werden. Seine Auswirkungen werden oft als Quantisierungsrauschen

bezeichnet.

1.2.7 Umsetzfehler

Jeder A/D-Umsetzer benötigt eine endliche, von der Schaltungsart und dem Umsetzverfahren

bestimmte Umsetzzeit (Öffnungszeit). Ändert sich während dieser Zeit das Eingangssignal,

entsteht bei der A/D-Umsetzung ein Fehler, der entweder als Amplituden- oder als Zeitfehler

aufgefasst werden kann (Abbildung 8).

V

V(t)

∆V = tA dV

dt

∆V = Umsetzfehler

tA

tA = Umsetzzeit

t

Abbildung 8: Umsetzfehler

Anmerkung:

Die in den Übungsunterlagen gemachten Angaben über digitale Codes beziehen sich, soweit

nicht besonders darauf hingewiesen wird, auf den natürlichen Binärcode.

Ausgabe 2002

AD1/AD2 – 7 / 22

2 Digital/Analog-Umsetzer

2.1

Aufgabe eines D/A-Umsetzers

Ein D/A-Umsetzer erzeugt eine analoge Abbildung einer digital dargestellten Zahl in der Art,

dass eine Referenzgröße mit einem entsprechenden Faktor gewichtet wird.

So liefert z.B. ein n-bit D/A-Umsetzer an dessen Eingang ein binär kodierter Spannungswert m

(0 <= m < 2n) liegt mit Hilfe einer Referenzspannung Vref eine analoge Ausgangsspannung

V = Vref

Der Faktor

m

2n

(1)

m

lässt sich in die folgende Form bringen:

2n

m

1

= n (B1 2 n −1 + B2 2 n −2 + ... + Bn 2 0 )

n

2

2

d.h.

B

B B

V = Vref 11 + 22 + ... + nn

2

2

2

(2)

Der Wert B kann dabei nur 1 oder 0 sein, je nachdem, ob das betreffende Bit gesetzt ist oder

nicht.

Eine Referenzspannung, die dem nominellen Endwert (nomineller voller Ausgangsspannungsbereich) VFSR (FSR = Full Scale Range) des Umsetzers entspricht, ermöglicht eine maximale

Ausgangsspannung UFS, die durch die Beziehung beschrieben wird:

1

V( B1 ... Bn =1) = VFS = VFSR 1 − n

2

(3)

Das bedeutet, dass der ideale maximale Skalenendwert (FS = Full Scale) immer um den

Bruchteil kleiner als der nominelle Endwert (FSR) ist (d.h.:FS=FSR-1 LSB).

Wie aus Gleichung (2) hervorgeht, setzt sich die Ausgangsspannung eines D/A-Umsetzers aus

einer Serie von diskreten Spannungen zusammen, wobei zwischen jedem Spannungswert und

dem digitalen Eingangscode ein direkter Zusammenhang besteht. Die korrespondierenden

Spannungswerte liegen auf einer Geraden, die der idealen Übertragungsfunktion des D/AUmsetzers entspricht.

2.1.1 Auflösung

Als Auflösung bezeichnet man einerseits die kleinste Änderung, die sich nach dem Setzen des

niederwertigsten Bits (Least Significant Bit = LSB) am Ausgang eines D/A-Umsetzers unter

idealen Bedingungen einstellt. Um für die Auflösung eine dimensionslose Größe zu erhalten,

lässt sich andererseits die Beziehung

1

Auflösung = n

2

aufstellen. Damit kann der analoge Wert des LSB berechnet werden:

1 LSB =

FSR

2n

Ausgabe 2002

AD1/AD2 – 8 / 22

In den meisten Fällen wird die Auflösung eines D/A-Umsetzers durch die Anzahl n der Bits

seines Eingangscodes ausgedrückt (n-bit D/A-Umsetzer).

2.2

Statische Genauigkeit von D/A-Umsetzern

Die statische Genauigkeit eines D/A-Umsetzers kann durch die Angabe der folgenden vier

Umsetzer-Fehler vollständig beschrieben werden.

2.2.1 Offsetfehler, Nullpunktsfehler

Ergibt sich bei einem digitalen Eingangscode, der den analogen Wert Null verlangt, ein anderer

Ausgangswert, bezeichnet man seine Abweichung von Null als Nullpunktsfehler (unipolarer

Betrieb). Er ist an jedem möglichen Punkt der Übertragungsfunktion dieser additiv mit gleichem

Betrag und gleichem Vorzeichen überlagert und kann abgeglichen werden. Bei einem bipolaren

D/A-Umsetzer tritt ein Offsetfehler am negativen Skalenendwert auf, während der

Nullpunktsfehler normalerweise mit dem Code 100…00 (MSB = Most Significant Bit gesetzt)

bestimmt wird.

In vielen Fällen wird allerdings, vor allem bei unipolaren Umsetzern, nicht zwischen dem Offsetund dem Nullpunktsfehler unterschieden (Abbildung 9).

7/8

Analog-Ausgang

6/8

5/8

4/8

3/8

2/8

1/8

Offsetfehler

0

001 010 011 100 101 110 111

Digital-Eingang

Abbildung 9: D/A-Umsetzer Offsetfehler

2.2.2 Verstärkungsfehler

Der Verstärkungsfehler (gain error) ist die Abweichung der realen von der idealen

Übertragungsfunktion im Skalenendwert (FS), hervorgerufen durch eine unterschiedliche

Steigung der beiden Kurven. Der Offsetfehler bleibt dabei unberücksichtigt.

Bei sinnvoller Darstellung beträgt die Steigung der idealen Transferfunktion k = 1. Ist die

Steigung der realen Übertragungsfunktion flacher, wird der Verstärkungsfehler negativ, ist sie

steiler, wird er positiv. Um die Größe des Verstärkungsfehlers zu bestimmen, muss bei

unipolaren D/A-Umsetzern die reale Übertragungsfunktion im Nullpunkt, bei bipolaren

Umsetzern exakt am negativen Skalenendwert beginnen (d.h. Offsetfehler abgleichen!). Bei

bipolaren D/A- Umsetzern erzeugt der Verstärkungsfehler einen zusätzlichen Nullpunktsfehler.

Der Verstärkungsfehler beeinflusst alle Ausgangswerte mit demselben prozentuellen Wert und

ist, ebenso wie der Offsetfehler, abgleichbar (Abbildung 10).

Ausgabe 2002

AD1/AD2 – 9 / 22

7/8

Verstärkungsfehler

Analog-Ausgang

6/8

5/8

4/8

3/8

2/8

1/8

0

001 010 011 100 101 110 111

Digital-Eingang

Abbildung 10: D/A-Umsetzer Verstärkungsfehler

2.2.3 Linearitätsfehler

Der (integrale) Linearitätsfehler (integrale Nichtlinearität, INL) ist ein Maß für die Abweichung

der analogen Werte von einer Geraden. Diese Gerade kann entweder eine Ausgleichsgerade sein,

die empirisch durch Manipulation des Verstärkungs- und/oder des Offsetfehlers so bestimmt

wird, dass die maximalen positiven und negativen Abstände der Messpunkte der realen

Transferkurve zu ihr gleich groß sind (best straight line, Ausgleichsgerade) oder eine Gerade

durch die beiden Endpunkte der realen Kurve (Endpunktabgleich), nachdem Offset- und

Verstärkungsfehler abgeglichen wurden (ideale Kennlinie). Die integrale Nichtlinearität wird

(überwiegend) in Vielfachen bzw. in Bruchteilen von 1 LSB angegeben.

In Abbildung 11 sind die Übertragungsfunktionen von nichtidealen D/A-Umsetzern mit

entsprechenden integralen Linearitätsfehlern aufgezeichnet. Abbildung 12 zeigt die beiden Arten,

Linearitätsfehler zu bestimmen.

7/8

Analog-Ausgang

6/8

Bit 2

1/2 LSB zu hoch

5/8

4/8

3/8

2/8

1/8

0

001 010 011 100 101 110 111

Digital-Eingang

Abbildung 11: D/A-Umsetzer Linearitätsfehler

Ausgabe 2002

AD1/AD2 – 10 / 22

(a)

INL-Bestimmung mit Ausgleichsgerade

(b)

INL-Bestimmung mit Endpunktabgleich

Endpunktabgleich

Verstärkungsfehler

7/8

7/8

6/8

5/8

5/8

4/8

Analog-Ausgang

Analog-Ausgang

Ausgleichsgerade

6/8

Nichtlinearität

< 1/2 LSB

3/8

2/8

1/8

0

4/8

Nichtlinearität

> 1/2 LSB

3/8

2/8

1/8

Offsetfehler

0

001 010 011 100 101 110 111

kein Offsetfehler

001 010 011 100 101 110 111

Digital-Eingang

Digital-Eingang

Abbildung 12: Vergleich der Kriterien zur INL-Bestimmung bei D/A-Umsetzern

Die Spezifikation des integralen Linearitätsfehlers nach der Endpunkt-Definition liefert

realistischere Werte und ist daher vorzuziehen.

Zu beachten ist, dass der integrale Linearitätsfehler nicht abgeglichen werden kann.

2.2.4 Differenzieller Linearitätsfehler

Im Gegensatz zur integralen Nichtlinearität, bei der die Fehler aller möglichen Ausgangspunkte

auf die ideale Übertragungsfunktion bezogen werden, wird mit der differenziellen Nichtlinearität

die Abweichung eines einzelnen Ausgangswertes von seinem idealen, theoretisch erwarteten

Wert erfasst. Die differenzielle Nichtlinearität beschreibt den Unterschied der analogen Schritte

zwischen benachbarten digitalen Codes. Sie ist Null, wenn ein Schritt zwischen zwei

benachbarten Codes genau 1 LSB ist. Andernfalls hat dieser Schritt einen differenziellen

Linearitätsfehler, der nicht abgeglichen werden kann (Abbildung 13).

LE

+- 1/2 LSB

LE = 0 LSB

LE

+- 1 LSB

LE = -1 LSB

DLE =

+1 LSB

LE = 0 LSB

DLE =

-1 LSB

LE = +1 LSB

DLE =

+1 LSB

LE = 0 LSB

DLE =

-2 LSB

LE = +1 LSB

DLE =

+1 LSB

DLE =

+1 LSB

LE = -1 LSB

DLE =

-1 LSB

LE ... Linearity Error (Linearitätsfehler)

DLE ... Differential Linearity Error (Differenzielle Nichtlinearität)

000

001

010

011

100

Digital-Eingang

101

110

111

Abbildung 13: Linearitätsfehler und differenzielle Nichtlinearität

Ausgabe 2002

AD1/AD2 – 11 / 22

2.2.5 Monotoniefehler

Die Monotonie ist, obwohl im eigentlichen Sinn keine Umsetzer-Spezifikation, eine wichtige

Übertragungseigenschaft eines D/A-Umsetzers. Die Monotoniebedingung fordert, dass ein

Umsetzer bei Erhöhung der Wertigkeit des digitalen Eingangscodes einen steigenden Wert der

analogen Ausgangsgröße liefert oder, mathematisch ausgedrückt: Die Ableitung der

Übertragungsfunktion muss immer größer/gleich Null sein.

Ein monotoner Umsetzbetrieb ist nur bei einer differenziellen Nichtlinearität von kleiner/gleich

1 LSB gewährleistet (Abbildung 14).

(b)

Nicht monotone Umsetzung auf Grund von

zu hoher DNL

7/8

7/8

6/8

6/8

5/8

5/8

Analog-Ausgang

Analog-Ausgang

(a)

Monotone Umsetzung mit großem

Linearitätsfehler

4/8

3/8

2/8

1/8

0

4/8

3/8

2/8

1/8

001 010 011 100 101 110 111

0

001 010 011 100 101 110 111

Digital-Eingang

Digital-Eingang

Abbildung 14: Monotonie bei D/A-Umsetzern

Als Beispiel für die Auswirkung einer nichtmonotonen D/A-Umsetzung soll ein A/D-Umsetzer,

der nach dem Prinzip der sukzessiven Approximation arbeitet und der einen internen DAC (D/AConverter) benötigt, betrachtet werden.

Da der analoge Ausgangswert des verwendeten DACs (Abbildung 15) bei gesetztem MSB

(korrekte Umsetzung: Die Bitkombination 100 ergibt VFSR/2) kleiner ist als der Wert für die

Bitkombination 011, ist die D/A-Umsetzung nicht monoton. Weil stets zuerst geprüft wird, ob

das MSB größer oder kleiner ist als der Eingangswert, mit dem es verglichen wird, ist die

Möglichkeit einer späteren Änderung ausgeschlossen. D.h., wenn das MSB einem kleineren

Wert als dem analogen Wert des Codes 011 entspricht, ist es unmöglich, dass der Code 011

erscheint (missing code).

Tabelle 1 zeigt die Resultate der Versuche bei verschiedenen Pegeln in der Umgebung des

nichtmonotonen DAC-Bereichs (Der Code wird akzeptiert wenn er unter dem Eingangspegel

liegt!).

Ausgabe 2002

AD1/AD2 – 12 / 22

7/8

Ausgangssignal

des internen D/AUmsetzers

Analog-Ausgang

6/8

5/8

4

4/8

3

2

1

3/8

2/8

Eingangspegel

1/8

0

001 010 011 100 101 110 111

Digital-Eingang

Abbildung 15: Ursachen für Missing Code

Eingangspegel (Abbildung 15)

Code

1

2

3

4

100

nein

ja

ja

ja

010

ja

-

-

-

011

nein

-

-

-

110

-

nein

nein

nein

101

-

nein

nein

nein

Digitales Ausgangswort

010

100

100

100

Richtiges digitales

Ausgangswort

010

010

011

100

Fehler

keiner

2 Bit

1 Bit

keiner

Tabelle 1:Umsetzergebnisse bei sukzessiver Approximation

2.3

Dynamische Parameter

Die maximale Umsetzgeschwindigkeit, die ein D/A-Umsetzer (z.B. mit Spannungsausgang)

erreichen kann, wird von einer Reihe dynamischer Faktoren begrenzt, von denen die Einstellzeit

von größter Bedeutung ist. Weiters verursachen transiente Spannungsspitzen (,,glitches“) am

Ausgang des Umsetzers nicht nur störende Fehler, sondern beeinflussen auch die Einstellzeit

ungünstig.

2.3.1 Einstellzeit

Die Einstell-, Einschwing- oder Beruhigungszeit eines D/A-Umsetzers umfasst die Zeitspanne,

die der Umsetzer benötigt, bis sich die Ausgangsspannung nach einem Codewechsel am Eingang

innerhalb eines definierten Fehlerbandes eingestellt hat (Abbildung 16).

Ausgabe 2002

AD1/AD2 – 13 / 22

V

Erholungszeit

Fehlerband

+- 1/2 LSB

+ FS

Einstellzeit

Anstiegsgeschwindigkeit

- FS

Digital-Eingang

alle '0'

alle '1'

t

Abbildung 16: Charakteristische Zeiten bei D/A-Umsetzern

2.3.2 Transiente Spannungsspitzen am Ausgang des D/A-Umsetzers

Als ,,glitch“ wird eine transiente Spannungsspitze bezeichnet, die bei jeder Umschaltung des

Eingangscodes am Ausgang eines D/A-Umsetzers auftreten kann. Dieser Effekt wird durch zwei

Fehlerquellen ausgelöst:

1. Nichtsynchrone Schaltzeiten der Analogschalter sowie Einstreuungen der Logikpegel

über parasitäre Kapazitäten auf die Signalwege. Um die Glitch-Fehler in tolerierbaren

Grenzen zu halten, müssen die Schaltzeiten der Analogschalter soweit wie möglich

synchronisiert werden, d.h. Schaltverzögerungen sollten bei allen Schaltern des

Umsetzer-Moduls gleich, und die Unterschiede zwischen der Einschalt- und der

Ausschaltverzögerung möglichst klein sein.

2. Unterschiedliche Schaltgeschwindigkeit der Logikelemente in Abhängigkeit von der

Flankenrichtung (Abbildung 17).

Bit 1

Digital-Eingang

Bit 2...n

Zeitlicher Versatz

Kein zeitlicher

Versatz

Abbildung 17: Unterschiedliche Signalverzögerungen als Ursache für „Glitches“

Ein maximaler Fehler tritt dort auf, wo eine Umschaltung des MSB auch eine Umschaltung aller

anderen Bits auslöst (z.B. 100…00 ! 011…11), d.h. der maximale Glitch-Fehler liegt genau in

der Skalenmitte eines D/A-Umsetzers. In Abbildung 18 ist als Beispiel die Erzeugung einer

Rampenfunktion mit Hilfe eines 3-bit D/A-Umsetzers aufgezeichnet.

Ausgabe 2002

AD1/AD2 – 14 / 22

Dezimal

Bit3

Bit2

Bit1

0

0

0

0

0

0

0

1

0

0

1

0

0

0

2

0

1

0

0

1

0

3

1

1

0

1

0

0

4

1

0

0

1

0

0

5

1

0

1

1

0

0

6

1

1

0

1

1

0

7

1

1

1

0

0

0

8

0

0

0

Abbildung 18: 3-Bit Rampenfunktion mit „Glitches"

Ausgabe 2002

AD1/AD2 – 15 / 22

3 Aus den Unterlagen zu „Elektronische Schaltungstechnik 2, VO“

3.1

D/A-Umsetzer

In der einfachsten Form kann eine D/A-Umsetzung durch eine Reihe von dual (binär) gestuften

Widerständen durchgeführt werden (Abbildung 19). In Abhängigkeit von der Ansteuerung durch

den Eingangscode werden die Analogschalter umgeschaltet, so dass Teilströme in den

Summenpunkt fließen. Ein Nachteil dieses Verfahrens ist es, dass pro Bit mehr Auflösung der

Betrag des Reihenwiderstandes verdoppelt werden muss. Mit der Zunahme der Auflösung muss

aber ebenso die Genauigkeit des Widerstands-Abgleichs zunehmen, um die Umsetzfehler in den

Grenzen zu halten, die der erhöhten Auflösung angepasst sind.

R

R

2R

Vaus

4R

Vref

2N-1R

Abbildung 19: D/A-Umsetzer mit dual gestuften Widerständen

Vorteilhafter ist die Verwendung eines R-2R-Widerstands-Netzwerkes, das den Eingangsstrom

in binär gewichtete Ströme aufteilt.

Seit es elektronische Schalter ohne Spannungsfehler (FET, MOS, CMOS) gibt, kann dieses

Leiternetzwerk direkt mit den Bitschaltern verbunden werden. Es kann dann als Spannungs- oder

Stromteiler fungieren.

MSB

Vref

2R

R

Vaus

2R

R

R

LSB

2R

2R

Abbildung 20: D/A-Umsetzer mit Leiternetzwerk als Spannungsteiler

Der Ausgang eines 2R/R Leiternetzes als Spannungsteiler kann formal als eine Spannungsquelle

mit der Klemmenspannung V = Vref m/2n und dem Innenwiderstand R betrachtet werden. 4 bit

Leiternetzgruppen können zu dekadischen BCD-Leiternetzen verbunden werden. (m = digital

dargestellte Zahl).

Ausgabe 2002

AD1/AD2 – 16 / 22

Bei der Verwendung des Leiternetzes als Stromteiler liegen alle Schalter auf Massepotential.

Auch die Spannung über den geöffneten Schaltern ist null (Umschalten zwischen Kontakten mit

gleichem Potential). Wenn die Schalter in beiden Stromrichtungen leiten, kann ein derartiger

Umsetzer auch eine Wechselspannung (am Referenzeingang) mit dem digitalen Wort bewerten.

Man erhält eine Multiplizierschaltung (multiplying DAC), die das analoge Produkt aus einem

analogen und einem digitalen Faktor bildet. Man erhält also z.B. ein digital einstellbares

Potentiometer.

R

Vref

2R

R

R

2R

2R

2R

R

MSB

LSB

Vaus

Abbildung 21: D/A-Umsetzer mit Leiternetzwerk als Stromteiler

3.2

A/D-Umsetzer

Man unterscheidet drei grundsätzlich verschiedene Umsetzungsprinzipien:

1. Parallelverfahren (flash converter):

Die Umsetzung wird in einem einzigen Arbeitsschritt durchgeführt; es werden n innere

Referenzgrößen benötigt. Das Verfahren ist sehr schnell (Videofrequenzen).

2. Wägeverfahren (successive approximation converter):

Es werden N = ld n Arbeitsschritte und N innere Referenzgrößen benötigt. Es ergibt sich

ein günstiger Kompromiss zwischen Umsetzzeit und Aufwand.

3. Zählverfahren (incremental converter).

Die Umsetzung dauert n Arbeitsschritte; es ist nur eine innere Referenzgröße notwendig.

Dieses Verfahren ist langsam, es weist aber eine sehr gute Linearität auf.

ar

R/2

K

D

Q

Q

R

a

K

D

Q

Q

n

Komparatoren

d

n

FFs

R

K

D

Q

Q Prioritätskodierer

R/2

clk

Abbildung 22: Parallel A/D-Umsetzer

Ausgabe 2002

AD1/AD2 – 17 / 22

Beim Parallel A/D-Umsetzer stellen n Komparatoren fest, welchem Intervall die Eingangsgröße

zuzuordnen ist. Der oberste Komparator in Abbildung 22 dient zur Anzeige einer

Bereichsüberschreitung. Die den einzelnen Intervallgrenzen entsprechenden Spannungen werden

in einem Spannungsteiler aus n Widerständen erzeugt. n D-Flip-Flops synchronisieren den

Zustand der Komparatoren damit sichergestellt wird, dass ein bestimmter Zeitpunkt für den

Umsetzvorgang repräsentativ ist. Ein Prioritätskodierer reduziert die Zahl der Datenleitungen

von n auf N. Derartige Umsetzer erreichen Auflösungen bis zu 8 bit (256 Komparatoren!) bei

Umsetzzeiten von 10 ns. Ein großes Problem stellen die vielen parallelgeschalteten

Komparatoreingänge dar, die einen hohen Eingangsstrom und eine hohe Eingangskapazität

verursachen. Die Genauigkeit derartiger Umsetzer hängt vom Spannungsteiler und den

Eingangsfehlspannungen der Komparatoren ab.

Start Status

Analogspeicher

a

N Takte

S&H

C

ar

A

D

N bit

DAC

Steuerlogik

T

}

SAR

N bit

Speicher

d

Abbildung 23: A/D-Umsetzer nach dem Wägeverfahren

Der A/D-Umsetzer nach dem Wägeverfahren ermittelt das Resultat der Umsetzung in gleicher

Weise, wie mit Hilfe einer Balkenwaage und einem duadischen Gewichtssatz eine unbestimmte

Masse bestimmt würde. Der Umsetzer besteht aus einem Komparator, einem N bit

Digital/Analog-Umsetzer mit Referenzspannung und einer logischen Schaltung, die häufig mit

SAR (successive approximation register) bezeichnet wird. Da sich während der N Taktschläge

dauernden Umsetzungs-Operation die Eingangsgröße nicht ändern darf, muss ein derartiger

Umsetzer mit einer analogen Speicherschaltung (sample and hold) betrieben werden. Diese sorgt

dafür, dass der Augenblickswert der Eingangsspannung zum Zeitpunkt des Beginns der

Umsetzung bis zum Ende zur Verfügung steht. Nach Eintreffen des Startsignals vergleicht der

Komparator das probeweise auf die logische Eins geschaltete höchstwertige Bit aus dem D/AUmsetzer mit der Eingangsgröße. Ist diese größer, wird diese Eins in die höchstwertige Stelle des

Registers eingeschrieben, der Beitrag der höchstwertigen Stelle bleibt während der weiteren

Umsetzung erhalten. War nach dem ersten Vergleich der Beitrag des höchstwertigen Bit größer

als die Eingangsspannung, wird die logische Null eingeschrieben. Im zweiten Arbeitsschritt wird

nun das nächst niederwertigere Bit probeweise auf Eins gesetzt und das Ergebnis des Vergleichs

beobachtet. Ergibt sich wieder eine größere Eingangsspannung, verbleibt die Eins an dieser

Stelle, andernfalls wird. eine Null in die zweite Stelle eingetragen. Nach N Taktschlägen ist die

Eingangsgröße a auf N bit genau durch die Stellung des Registers angenähert. Umsetzer nach

diesem Verfahren sind weit verbreitet, sowohl in Mikrocontrollersystemen als auch für die

digitale Signalverarbeitung. Zurzeit sind Umsetzer mit 16 bit Auflösung und Konversionszeiten

von ca. 1 µs verfügbar (z.B. AD7677, Analog Devices). Die Genauigkeit des Umsetzers hängt

wesentlich von jener des internen D/A-Umsetzers ab. Formal kann das System wie eine

Gegenkopplungsschleife betrachtet werden, in der sich ein D/A-Umsetzer befindet. Der

Umsetzvorgang entspricht dem Einschwingen der Schleife.

Alle inkrementalen Umsetzer benötigen eine nicht unerhebliche Zeit zur Ausführung der

Umsetzung. Diese Zeit kann nützlich zur Bildung des arithmetischen Mittelwertes der zu

messenden Spannung und damit zur Unterdrückung von der Messspannung überlagerten

Ausgabe 2002

AD1/AD2 – 18 / 22

Störspannungen herangezogen werden. A/D-Umsetzer, die den Zeitmittelwert der Eingangsgröße

bewerten, heißen integrierende A/D-Umsetzer. Diese bilden den zeitlichen Mittelwert der

analogen Größe a während der festen Zeitspanne T

1

a=

T

T

∫ a dt

0

Eine periodische Störspannung as der Frequenz f

a s = aˆ s cos 2πft

erzeugt in Abhängigkeit von der zeitlichen Lage des Integrationsintervalls einen Mittelwert a s ,

für den gilt

a s ≤ aˆ s

1

T

sin πfT

, weil

πfT

T

2

∫

−

T

2

cos( 2πft ) dt =

sin πfT

πfT

Dies bedeutet, dass Störsignale, deren Perioden in der Integrationszeit ganzzahlig enthalten sind,

vollkommen unterdrückt werden.

Abbildung 24: Unterdrückung der Störspannung durch die Bildung des zeitlichen Mittelwertes

Ausgabe 2002

AD1/AD2 – 19 / 22

Für Störfrequenzen, die der Messspannung überlagert sind, verhält sich ein integrierender

A/D-Umsetzer wie ein Tiefpass erster Ordnung, dem zusätzliche Nullstellen unterlagert sind. In

der Praxis wird daher die Integrationsdauer als ganzzahliges Vielfaches der Netzperiode gewählt.

Tektfrequenz f 0

C

f

R1

Q

a

Frequenz

(Rate)

OP

C

D

Q

R2

k

ar

a

R1

ar

k

R2

0,

k

f

f0

Tastverhältnis

a R2

ar R1

Abbildung 25: Ladungsausgleichsintegrator (charge balance)

Am Ausgang k kann ein zeit- und wertdiskretes, binäres Signal abgenommen werden. Der

zeitliche Mittelwert dieses Signals ist streng proportional der Eingangsgröße des Umsetzers a.

Um eine der Frequenz ähnliche Größe (Rate) zur Verfügung zu stellen, muss das Signal k mit der

Taktfrequenz des D-FFs UND-verknüpft werden. Es ergibt sich ein Impuls für jede Taktzeit, in

der der Schalter geschlossen ist.

Eine Fehlerquelle in diesem Verfahren sind die unterschiedlichen Laufzeiten des FFs und des

Schalters für die steigende und fallende Flanke. Wenn durch geeignete Schaltungsmaßnahmen

verhindert wird, dass das Tastverhältnis > 0,5 wird, ergibt sich für jedes rückgekoppelte

Ladungspaket der gleiche relative Fehler. Somit führen die ungleichen Laufzeiten nur zu einem

Steigungs- und keinem Linearitätsfehler.

a

f

k

Int.

Abbildung 26: Spannungsverlauf im Ladungsausgleichsintegrator

Anmerkung: Wegen der Aperiodizität ist es äußerst schwierig, von den Signalverläufen f, k und

Int. ein stehendes Oszillogramm zu erzeugen.

Das gezeigte Beispiel des Ladungsausgleichsintegrators benötigt eine Referenzspannung mit

einem der Messspannung umgekehrten Vorzeichen. Es kann nur Eingangsgrößen einer Polarität

verarbeiten. Bipolare Signale werden verarbeitet, wenn eine positive und negative

Referenzspannung gleichen Betrages verwendet wird und der Widerstand R2 entsprechend der

Stellung des FFs an die positive oder die negative Referenzspannung gelegt wird. Der das

Ausgabe 2002

AD1/AD2 – 20 / 22

Resultat speichernde Zähler zählt in dem einen Fall rückwärts, im anderen Fall vorwärts. Die

Eingangsspannung 0 Volt entspricht somit dem Tastverhältnis 0,5: Es wird gleich häufig

vorwärts und rückwärts gezählt, das Resultat ist Null.

Die Größe des Integrationskondensators bestimmt den dem Komparator zur Verfügung

stehenden Hub. In die Genauigkeit des Umsetzers geht der Betrag der Kapazität nicht ein. Zur

Messung sehr hoher Spannungen kann der Widerstand R1 beliebig groß gemacht werden, weil

vor R1 kein Schalter liegt. Am virtuellen Nullpunkt des Integrators sind leicht Schutzdioden

anzubringen. Aus diesem Grund kann dieser Umsetzer auch im Bereich der

Hochspannungsmesstechnik gut verwendet werden. Sein Ausgangssignal kann über Lichtleiter

abgeführt werden.

Das Zwei-Rampenverfahren (dual slope, dual ramp) ist das älteste integrierende A/D-Umsetzerverfahren. Es ist im Messgerätebau weit verbreitet.

S1

S1

C

S2

S2

a

R

Takt

u

S3

OP

ar

S3

τ

Steuerlogik

C

d

Zähler

u

Null

S1

Mess

S2

mτ

Ref

S1

nτ

Null

S1

t

Abbildung 27: Zwei-Rampen-Verfahren (dual slope, dual ramp)

Das Verfahren läuft in drei Arbeitsschritten (siehe Abbildung 27). Während der Phase Null (S1

geschlossen) wird der Integrationskondensator entladen. In der Phase Mess (S2 geschlossen) wird

das Zeitintegral der Messgröße a während einer festen Zahl m von Taktschlägen der Dauer T

gebildet. Danach wird in der Phase Ref (S3 geschlossen) zu dem gebildeten Integral das

Zeitintegral der Referenzgröße hinzugezählt. Da die Referenzgröße umgekehrtes Vorzeichen

trägt, wird zu einem bestimmten Zeitpunkt der Betrag des Integrals Null sein. Zu diesem

Zeitpunkt unterbricht der Komparator die Referenzintegration, der Zähler in der Steuerlogik

zeigt die Dauer der Referenzintegration als Ergebnis an. Wie man sieht, kürzt sich aus dem

Resultat sowohl die Periode des Taktgenerators τ als auch das RC-Produkt des Integrators. Diese

beiden Tatsachen sind der Grund für die große Beliebtheit des Verfahrens.

Nachteile des Verfahrens sind

1. die Tatsache, dass die ,,Beobachtung“ des Eingangssignals durch die Phasen Null und

Ref unterbrochen wird,

2. dass beim zeitlichen Übergang von Mess auf Ref die gesamte Information im

Integrationskondensator steckt und dessen dielektrische Absorption den

Genauigkeitsengpass darstellt und

Ausgabe 2002

AD1/AD2 – 21 / 22

3. dass im Eingang a ein elektronischer Schalter S2 notwendig ist, der es verbietet, höhere

Spannung direkt zu verarbeiten.

Da die Schalter S1 und S3 nur einmal pro Konversion betätigt werden, sind ihre Zeitfehler wenig

kritisch.

Wird die Referenzspannung während der Referenzintegration von der Stellung des Zählers

abhängig gemacht, kann der Umsetzer Sensorfunktionen implizit lösen. Die Abhängigkeit der

Referenzspannung wird erzeugt, indem diese aus einem D/A-Umsetzer entnommen wird, dessen

Eingangssignale aus einem ROM stammen, welches vom Zähler adressiert wird. Einfache

nichtlineare Funktionen können auch implementiert werden, wenn während der Referenzphase

der Widerstand R z.B. mit Hilfe eines parallelgeschalteten Leiternetzes verändert wird.

Die eben gezeigte Schaltung hat nur prinzipielle Bedeutung, weil einerseits der

Eingangswiderstand klein ist und die Eingangsfehlspannung des Operationsverstärkers stört.

C

a

S2

R2

S1

-ar

S3

R

R1

OP1

OP2

OP3

K

D

S1

Q

Q

R3

τ

CAZ

Abbildung 28: Praktische Ausführung des Zwei-Rampen A/D-Umsetzers

Tatsächlich eingesetzte Umsetzer (siehe Abbildung 28) verwenden einen Folger im Eingang,

einen Nachverstärker zur schnelleren Ansteuerung des Komparators und automatischen

Nullabgleich (Autozero). In der Phase Null sind jetzt die Schalter S1 und /S1 geschlossen. Am

nichtinvertierenden Eingang von OP2 wird sich jene Spannung einstellen, die notwendig ist, dass

in den Integrationskondensator kein Strom fließt. Da gleichzeitig der Eingang von OP1 auf

Masse liegt, ist somit jene Spannung in CAZ gespeichert, die die Fehlspannungen der ersten drei

Operationsverstärker ausgleicht. Wenn S1 danach geöffnet wird, hält der Kondensator CAZ diese

Spannung während der beiden anderen Phasen konstant. Durch diese Maßnahme wird sowohl

die Offsetspannung der Operationsverstärker als auch deren zeitliche Veränderung (Alterung)

vollkommen ausgeglichen. Der Widerstand R3 verhindert die kapazitive Belastung von 0P3

durch den großen (ca. 1 µF) Kondensator CAZ. Durch den begrenzenden Nachverstärker wird die

Steigung der Rampe in der Nähe des Nulldurchganges vergrößert und somit die zeitliche

Unsicherheit des Komparators reduziert. Wenn dieses analoge System mit kritischen

Spannungen < 1 mV in unmittelbarer Nähe des digitalen Steuerwerks arbeiten soll (auch auf dem

gleichen Halbleiterchip), dann ist es vorteilhaft, mit Hilfe eines Synchronisations-Flip-Flops die

Stellung des Komparatorausganges zu einem Zeitpunkt abzufragen, zu dem das Digitalsystem in

Ruhe ist.

Mit derartigen Maßnahmen ist es möglich, Umsetzer mit Auflösungen bis zu 20 bit und

Empfindlichkeiten von 1 µV zu konstruieren. Bei den hohen Auflösungen stört oft die dabei

entstehende lange Messzeit. Sie kann dadurch verkürzt werden, dass während der Messphase in

Anlehnung an das charge balance Verfahren der Integrationskondensator immer wieder entladen

wird und auf diese Weise die höherwertigen Stellen des Messresultates ermittelt werden. Nach

Ausgabe 2002

AD1/AD2 – 22 / 22

Ende der Messphase wird dann entsprechend kürzer zur Ermittlung der fehlenden Stellen

referenzintegriert. Auch in der Referenzintegration kann zur Verkürzung der Zeit mit

dezimalgewichteten Strömen gearbeitet werden (multiple slope). Alle diese verkürzenden

Maßnahmen machen den Vorteil, dass der Betrag des Integratorwiderstandes nicht eingeht,

zunichte.

Nachstehend ist ein Vergleich des Ladungsausgleichs- mit dem Zwei-Rampen-A/D-Umsetzverfahren durchgeführt.

Ladungsausgleich

Zwei-Rampen

C

C

R1

R

a

K

a

K

R2

-ar

-ar

kontinuierlich

diskontinuierlich

ar, R1, R2 genau

nur ar genau!

a beliebig groß

a begrenzt

C klein

mittlere Ladung ! 0

OP kritisch

Komparator unkritisch

C groß, DA = 0

mittlere Ladung prop. A

OP unkritisch

Komparator kritisch

Störladung und Zeitfehler des Schalters sehr

kritisch

Störladung und Zeitfehler der Schalter

unkritisch

Ausgabe 2002