ReCoNets – Hardware/Software-Partitionierung zur Steigerung der

Werbung

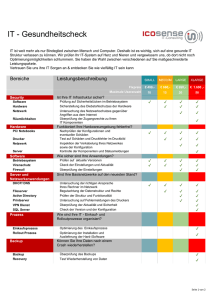

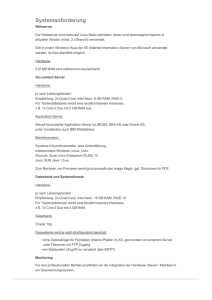

ReCoNets – Hardware/Software-Partitionierung zur Steigerung der Fehlertoleranz und Flexibilität Ch. Haubelt, D. Koch, T. Streichert, Prof. Dr.-Ing. J. Teich, Prof. Dr. rer. nat. R. Wanka Lehrstuhl für Hardware-Software-Co-Design Universität Erlangen-Nürnberg Motivation Verhalten Struktur S1 Sen1 BH Ctrl1 Ctrl’1 S3 Akt1 Akt2 = Software-Task = Hardware-Task S2 Wer Werentscheidet, entscheidet,wo wound undwie wieein einTask Task ausgeführt ausgeführtwird? wird? SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 2 ReCoNets ¾ Vernetztes eingebettetes System: Knoten bestehen aus - CPU zur Ausführung von Software Rekonfigurierbarer Logik für dedizierte Hardware Kommunikations-Interface Knoten kommunizieren über Punkt-zu-Punkt Verbindungen < 100 Knoten ¾ Anforderungen: Flexibilität für dynamisch variierende Nutzungsszenarien Fehlertoleranz gegenüber Link- und Knotenausfällen Online Hardware/Software-Partitionierung basierend auf Hardware/Software-rekonfigurierbaren Netzwerken SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 3 Gliederung ¾ Einleitung ¾ Online Hardware/Software-Partitionierung Optimierung der Task-Bindung Hardware/Software-Migration Hardware/Software-Morphing ¾ Implementierung ¾ Kooperationen ¾ Events SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 4 Online HW/SW-Partitionierung Schnelle Reparatur Defekt? Link Knoten Replikaaktivierung Wiederherstellung d. Kommunikation ¾ Bisherige Optimierung der TaskBindung basiert auf: Online HW/SW-Partitionierung Optimierung der Task-Bindung Lastbalanzierung zur Verteilung der Tasks zwischen Knoten Bipartitionierung zur Verteilung der Last zwischen Hard- und SoftwareRessourcen auf jedem Knoten ¾ Theoretische Grenzen und experimentelle Ergebnisse vorgestellt Task-Replizierung ¾ T. Streichert, Ch. Haubelt, and J. Teich: Distributed HW/SW-Partitioning for Embedded Reconfigurable Systems. In Proc. of DATE’ 05, Munich, Germany, March 7-11, 2005. ¾ T. Streichert, Ch. Haubelt, and J. Teich: Verteilte HW/SW-Partitionierung für fehlertolerante rekonfigurierbare Netzwerke. In Proc. of 17. Workshop für Testmethoden und Zuverlässigkeit von Schaltungen und Systemen, Innsbruck, Austria, Feb. 27-Mar. 1, 2005. ¾ T. Streichert, Ch. Haubelt, and J. Teich: Online Hardware/Software Partitioning in Networked Embedded Systems. In Proc. of ASP-DAC’05, Shanghai, China, January 18-21, 2005. SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 5 Optimierung ¾ Eigenschaften der Optimierung der Task-Bindung: 9 Dezentrale Ausführung 9 Nur lokales Wissen notwendig 9 Reduzierung der Latenz und Antwortzeiten von Tasks 9 Reduzierung von Overhead durch Context-Switches Mehrere Lastgrößen für Software- und Hardware-Tasks Berücksichtigung von Datenabhängigkeiten Verhalten SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt Struktur 6 Optimierung mit Datenabhängigkeiten 1. Berechnung der Bindungsverbesserung in Abhängigkeit von: • • • Implementierungsart (Hardware/Software) Benötigte Bandbreite der Datenabhängigkeit Größe der Binaries/Bitstreams 2. Anfrage an Nachbarknoten, ob Scheduler/Placer Ressourcen zur Verfügung stellen kann 3. Wenn ja, dann Task-Migration / Task-Morphing Port 1 T3 T1 10 Port 2 80 20 100 T2 SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt Port 3 7 Optimierung mit Datenabhängigkeiten 1. Berechnung der Bindungsverbesserung in Abhängigkeit von: • • • Implementierungsart (Hardware/Software) Benötigte Bandbreite der Datenabhängigkeit Größe der Binaries/Bitstreams 2. Anfrage an Nachbarknoten, ob Scheduler/Placer Ressourcen zur Verfügung stellen kann 3. Wenn ja, dann Task-Migration / Task-Morphing Port 1 T3 Port 2 10 80 20 T2 SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 100 Port 3 T1 8 Optimierung: Evaluierung ¾ ¾ Vergleich von Online-Optimierung mit Offline-Optimierung Reduktion der Netzlast um ca. 20% 9 Dezentrale Ausführung 9 Nur lokales Wissen notwendig 9 Reduzierung der Latenz und Antwortzeiten von Tasks 9 Reduzierung von Overhead durch Context-Switches 9 Mehrere Lastgrößen für Software- und Hardware-Tasks 9 Berücksichtigung von Datenabhängigkeiten ¾ T. Streichert, Ch. Strengert, Ch. Haubelt, and J. Teich: Dynamic Task Binding for Hardware/Software Reconfigurable Networks. To appear in Proc. of SBCCI 2006, Ouro Preto, Brasil, August 28-September 1, 2006. ¾ T. Streichert, Ch. Haubelt, and J. Teich: Multi-Objective Topology Optimization for Networked Embedded Systems. To appear in Proc. of SAMOS VI, Samos, Greece, July 17-20, 2006. SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 9 Gliederung ¾ Einleitung ¾ Online Hardware/Software-Partitionierung Optimierung der Task-Bindung Hardware/Software-Migration Hardware/Software-Morphing ¾ Implementierung ¾ Kooperationen ¾ Events SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 10 Software-Migration ¾ Transfer des Programms und des Zustands ¾ Zustand einer Software-Task Prozessorregister (incl. PC) Stack (Aufrufhierarchien) Variablen Prozesskontrollblock - ¾ TSW T’ TCP SW SW Prozesskennung (PID) Ausführungszustand (Running, Blocked, Idle) Betriebsmittel (Geräte, Kommunikation, Speicher) Zugriff auf Zustand Betriebssystem (Taskwechsel) Durch den Programmierer Zustandsextraktion und –übertragung durch explizite Funktionsaufrufe SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 11 Hardware-Migration ¾ Transfer der Konfigurationsdaten und des Zustandes ¾ Zustand einer Hardware-Task Datenpfad- und Kontrollpfadregister Fifo-Füllstände Prozesskontrollblock - ¾ THW T’ TCP HW HW Prozesskennung (PID) Ausführungszustand (Running, Blocked, Idle) Betriebsmittel (Geräte, Kommunikation, Speicher) Eigene Ressourcen (CLB-Fläche, Adressraum, IRQs) Zugriff auf Zustand Architekturebene (Zurücklesen der Konfigurationsdaten) Modulebene (Modifikation der Hardware-Module) Zustandsextraktion auf Modulebene und Übertragung durch explizite Funktionsaufrufe SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 12 Synthese – HW-Zustandsextraktion Scan Chain Hardware-Overhead SC H LUT ≤N N⎤ ⎡ SC H FF ≈ W + ⎡log 2 N ⎤ + ⎢log 2 ⎥ W⎥ ⎢ Shadow Scan Chain N⎤ ⎡ SHC H LUT ≈ 2W + ⎢log 2 ⎥ + 2 N W⎥ ⎢ N⎤ ⎡ SHC H FF ≈ W + ⎢log 2 ⎥ + N W⎥ ⎢ Memory Mapped H MM LUT ⎡ N ⎡log8 N /W ⎤−1 n N ⎛N ≈ + ∑ 8 + + W ⎢log 4 ⎜ W 2 ⎝W n=0 ⎢ ⎞⎤ ⎟⎥ + N ⎠⎥ MM H FF ≈W N: Anzahl der Flipflops, W: Busbreite SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 13 Synthese – HW-Zustandsextraktion Ergebnisse für DES56-Modul von opencores.org (862 Flipflops,1899 LUTs) Scan Chain SC H LUT = +28% SC H FF = +8% Shadow Scan Chain Memory Mapped SHC H LUT = +95% MM H LUT = +47% SHC H FF = +112% MM = +5% H FF Checkpoint Overhead (Zeitdauer der Zustandsextraktion) CSC ( N ) = O( N 2 ) CSHC ( N ) = O(1) 10354 Takte SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 0 Takte CMM ( N ) = O( N ) 1188 Takte 14 Implementierung – Hardware-Migration HDL-Source front-end synthesis (Synopsis DesignCompiler) Netlist GTECH-Netlist Interface template Initial System StateAccess register description file GTECH-Netlist GTECH*-library back-end synthesis and place & route (Altera Quartus, Xilinx ISE) config. bitstream ¾ T. Streichert, D. Koch, C. Haubelt, and J. Teich: Modeling and Design of Fault-Tolerant and Self-Adaptive Reconfigurable Networked Embedded Systems. To appear in EURASIP Journal on Embedded Systems; Hindawi Publishing Corporation, 2006. SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 15 Gliederung ¾ Einleitung ¾ Online Hardware/Software-Partitionierung Optimierung der Task-Bindung Hardware/Software-Migration Hardware/Software-Morphing ¾ Implementierung ¾ Kooperationen ¾ Events SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 16 Hardware/Software-Morphing ¾ ¾ Allokation der Hardware- bzw. Software-Ressourcen Übertragung und Transformation des Zustandes ¾ Funktionale Beschreibung durch T’ TCP SW HW einen deterministischen, endlichen Zustandsautomaten Verfeinerung in Hardware bzw. Software erhöht die Anzahl der internen Zustände Hardware-Software-Morphing nur möglich, wenn eine bijektive Transformation von S in beiden Verfeinerungen existiert S SSW SHW MSW MHW ¾ ¾ -1 MSW SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt -1 MHW 17 Analyse – Hardware-Software-Morphing ¾ Welche Einschränkungen gibt es? Granularität (wie viele Morphpunkte?) Einschränkungen in Kontroll- und Datenflüssen? ¾ Automatische Morphfunktionsgenerierung Wie muss Einfluss auf Zustandscodierungen genommen werden? Effiziente Algorithmen ¾ Morphpunktoptimierung (Wo Morphpunkte einfügen?) Minimaler Kontext (Extraktion und Morphen nicht aller Variablen erforderlich) Minimierung der Zeit zwischen den Morphpunkten ¾ Overhead Zusätzlicher SW/HW-Aufwand für die Zustandstransformation? Benötigte Zeiten? SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 18 Gliederung ¾ Einleitung ¾ Online Hardware/Software-Partitionierung Optimierung der Task-Bindung Hardware/Software-Migration Hardware/Software-Morphing ¾ Implementierung ¾ Kooperationen ¾ Events SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 19 Implementierung – ReCoNets ¾ Netzwerk mit vier Knoten ¾ Punkt-zu-Punkt Kommunikation ¾ Plattform: Altera FPGAs (aktueller Stand) Portierung auf ESM (in Arbeit) MicroC/OS - Message-Passing Interprozess-Kommunikation ReCoNets SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 20 Betriebssysteminfrastruktur Applikationen Dynamische Hardware/Software Partitionierung Dynamisches Rerouting Hardware/Software Hardware/Software Task Migration Morphing Basis Netzwerkdienste Lokales Betriebssystem Rekonfigurierbares Rekonfigurierbares Netzwerk Netzwerk ¾ D. Koch, T. Streichert, S. Dittrich, C. Strengert, C. Haubelt, and J. Teich: An Operating System Infrastructure for Fault-Tolerant Reconfigurable Networks. In Proc. of the 19th International Conference on Architecture of Computing Systems (ARCS 2006), Frankfurt / Main, Germany, pp 202-216, March 13-16, 2006. SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 21 SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 22 Gliederung ¾ Einleitung ¾ Online Hardware/Software-Partitionierung Optimierung der Task-Bindung Hardware/Software-Migration Hardware/Software-Morphing ¾ Implementierung ¾ Kooperationen ¾ Events SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 23 Kooperationen – PadErOl ¾ Ziel: Ein durchgängiger Entwurfsfluss für dynamisch rekonfigurierbare Systeme ¾ Momentan: Evaluierung anhand eines dynamisch rekonfigurierbaren KryptographieSystems ¾ Christian Haubelt: Automatic Model-Based Design Space Exploration for Embedded Systems - A System Level Approach. Dissertation, Universität Erlangen-Nürnberg, ISBN 3-89574-572-3, 2005 SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 24 Weitere Kooperationen ¾ Projekt ReCoNodes Kopplung ReCoNodes (Mikrosicht) und ReCoNets (Makrosicht) Platzierungsalgorithmen für Hardware-Migration/Morphing Checkpoints für Relokation ¾ Projekt CRC (Configurable Reconfigurable Core) (Universität Tübingen) Abbildung datenflussdominanter regelmäßiger Algorithmen auf das CRC-Modell im Rahmen des DFG-Projekts CoMap Rekonfigurierbare Verbindungsnetzwerke SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 25 Events ¾ Lange Nacht der Wissenschaften ¾ EuroScienceOpenForum (15.-19.7.06 in München) ¾ DATE’06 Friday Workshop ¾ Hannover Messe Industrie (Halle 2, Research & Technology) ¾ J. Teich, C. Haubelt, D. Koch, and T. Streichert: Concepts for Self-Adaptive Automotive Control Architectures. DATE'06 Friday Workshop Future Trends in Automotive Electronics and Tool Integration, Conference Design Automation and Test in Europe, March 10, 2006, Munich, Germany. SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 26 Zusammenfassung ¾ Modellierung AP1: Modelle für das HW/SW-Morphing AP2: Selbstroutende Netze In Bearbeitung Erledigt Noch zu Bearbeiten ¾ Analyse AP3: Mechanismen selbstroutender Netzverbindungen AP4: Kosten für das HW/SW-Morphing AP5: Kostenanalyse von Reparaturstrategien ¾ Synthese und Optimierung AP6: Extraktion von HW/SW-Kontexten; AP7: Algorithmen zum Morphen von HW/SW-Kontexten AP8: Repartitionierung mit Datenabhängigkeiten ¾ Implementierung AP9: Betriebssysteminfrastruktur AP10: Morphing & Repartitionierung AP11: Plazierung duplizierter Tasks AP12: Demonstrator mit Automotive-Beispiel SPP1148-Zwischenkolloquium, 01./02.06.06, Darmstadt 27