Uebung10_FET_switch

Werbung

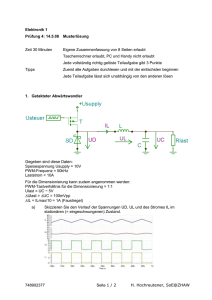

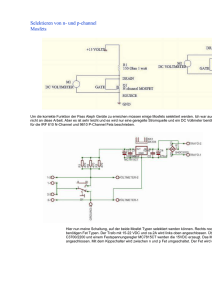

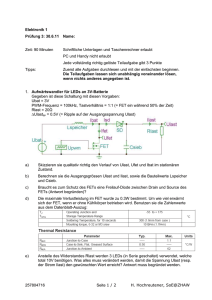

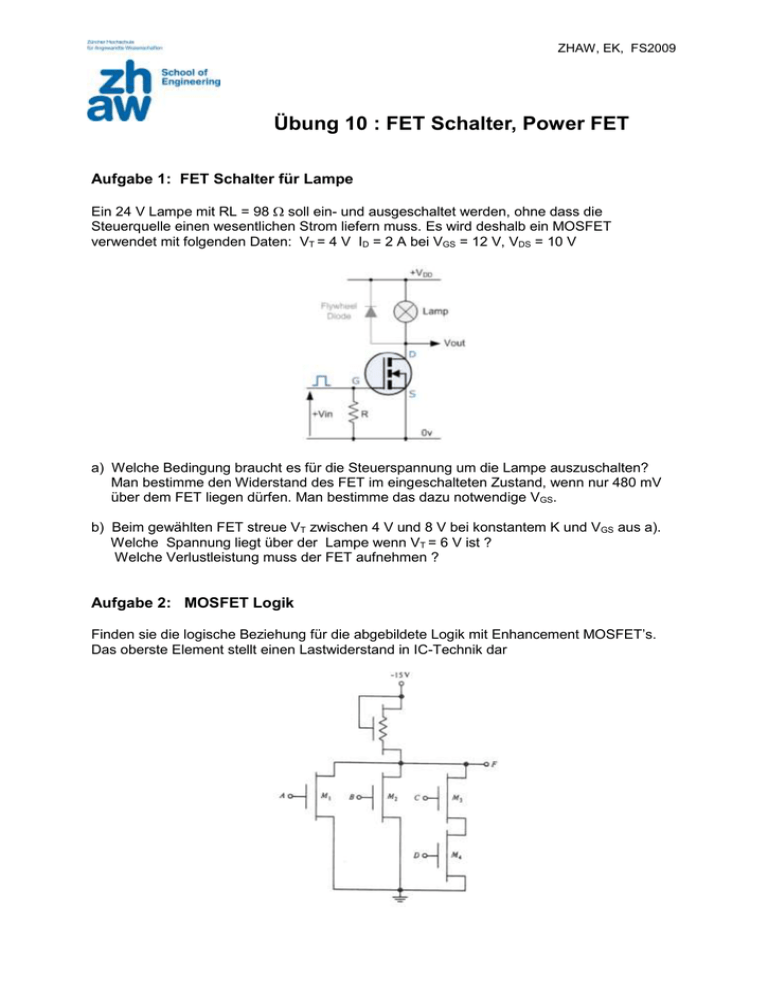

ZHAW, EK, FS2009 Übung 10 : FET Schalter, Power FET Aufgabe 1: FET Schalter für Lampe Ein 24 V Lampe mit RL = 98 soll ein- und ausgeschaltet werden, ohne dass die Steuerquelle einen wesentlichen Strom liefern muss. Es wird deshalb ein MOSFET verwendet mit folgenden Daten: VT = 4 V ID = 2 A bei VGS = 12 V, VDS = 10 V a) Welche Bedingung braucht es für die Steuerspannung um die Lampe auszuschalten? Man bestimme den Widerstand des FET im eingeschalteten Zustand, wenn nur 480 mV über dem FET liegen dürfen. Man bestimme das dazu notwendige VGS. b) Beim gewählten FET streue VT zwischen 4 V und 8 V bei konstantem K und VGS aus a). Welche Spannung liegt über der Lampe wenn VT = 6 V ist ? Welche Verlustleistung muss der FET aufnehmen ? Aufgabe 2: MOSFET Logik Finden sie die logische Beziehung für die abgebildete Logik mit Enhancement MOSFET’s. Das oberste Element stellt einen Lastwiderstand in IC-Technik dar ZHAW, EK, FS2009 Aufgabe 3: Boost Konverter Dimensionieren sie eine Boost Konverter, der mit 500 kHz taktet und aus einer Lithium Zelle mit 3.6 V eine Betriebsspannung von 12 V 0.05 V erzeugt. Die Last verbraucht 200 mA Strom. a) Wie gross ist das Tastverhältnis D ? b) Berechnen sie L und C Werte mit denen sie die Erprobung starten können (RF = 5) c) Überlegen sie sich, wie die abgebildete Schaltung aus einer positiven Eingangsspannung eine negative Ausgangsspannung macht. Lösungen: Aufgabe 1: a) Die Lampe ist aus, wenn VGS < VT also < 4 V ist Datenblattwert ist in Saturation Region weil VDS > VGS-VT (üblich) Aus Datenblattwerten: ID = K (VGS-VT)2 folgt K = 1/32 A/V2 rDS darf 2 betragen (Spannungsteiler an 24 V mit Lampe rDS = 1/(2K(VGS-VT)) = 2 liefert VGS-VT = 8 V somit VGS = 12 V b) rDS = 1/(2K(VGS-VT)) = 32/(2(12-6)) = 2.67 vL = 24*98/100.67 = 23.36 V P = VDS2 / rDS = 0.642 / 2.67 = 153 mW Aufgabe 2: Der Ausgang ist 0 V wenn einer der parallel FET Stränge niederohmig , d.h. eingeschaltet ist. Ausgang 0 V wenn A = 1 oder B=1 oder beide C und D = 1 F = A + B + (CD) ZHAW, EK, FS2009 Aufgabe 3: a) D = 1- Vin/Vout b) Lf D = 1 – 3.6/12 = 0.7 70 % ist der FET eingeschaltet. RF Vin2 D 5 3.6 2 0.7 38 H f s I o Vout 500000 0.2 12 Cf D I0 0.7 0.2 2.8 F f s Vout 500000 0.1 c) Q1 (PMOS Depletion) leitet und lädt L auf, Strom fliesst von FET nach Masse. Diode sperrt. Last bezieht Strom aus C Q1 sperrt. Strom in L muss weiter fliessen wegen diL/dt. Spannung über L springt von Vin auf –Vout. Diode leitet. C wird aufgeladen und auch die Last gespiesen.