EK1_P3_2012_05_21_Lo..

Werbung

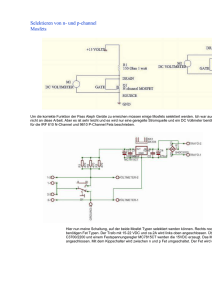

Elektronik 1 MUSTERLÖSUNG zum Kurztest 3 vom 21. Mai 2012 1) Thermisches Design a) Aufgabe: Weshalb ist die vom Hersteller spezifizierte maximale Verlustleistung von 300 W für reale Anwendung wenig realistisch? Nennen Sie zwei Gründe! (TC = case temperature) Lösung: Folgende Gründe können angeführt werden: - Die spezifizierten 300 W gelten nur, wenn die Gehäusetemperatur auf 25 C gehalten werden kann; dies ist bei einer Umgebungstemperatur von ebenfalls ungefähr 25 C gar nicht möglich, da der Kühlkörper einen thermischen Widerstand >0 aufweist. - Selbst wenn der Kühlkörper auf 25 C Temperatur gehalten werden könnte (z. B. mit einem Peltier-Element) ergäbe sich eine höhere Gehäusetemperatur, wegen des Übergangswiderstandes vom Kühlkörper zum Gehäuse (vom Hersteller mit 0.5 C/W spezifiziert). - 300 W Verlustleistung bei TC = 25 C ergibt eine Chip-Temperatur von 175 C; dies ist das erlaubte Maximum und für die Lebensdauer des Bauteils unvorteilhaft. b) Aufgabe: Wie gross darf der Draindauerstrom bei einer Umgebungstemperatur von 50 C auf Grund der im Datenblattauszug gegebenen Informationen maximal sein, wenn das Bauteil ohne Kühlkörper angewandt wird? Lösung: Für die Berechnung der erlaubten Verlustleistung ist der Wärmewiderstand T JA (junction-to-ambient) massgebend. Für die maximale Verlustleistung erhält man: PD ,max T J , max TA RJA (175C 50C ) 2.0 W 62C / W Der maximale (garantierte) ON-Widerstand des FET beträgt 1.5 m, somit ergibt sich für den maximalen Dauerstrom ID,max: I D ,max PD ,max RDSON,max 2.0W 36.5 A 1.5m Bemerkung: Auch hier sollte man eine Sicherheitsreserve vorsehen und auf eine tiefere ChipTemperatur dimensionieren, z. B. 125 C. 2) Aufwärtswandler a) Aufgabe: Zeichnen Sie das Schaltschema eines Aufwärtswandlers (ohne Erzeugung des FET-Steuersignals) und beschrieben Sie in kurzen Sätzen die Funktion jedes Elements. Bezeichnen Sie auch klar, wo der Ein- und der Ausgang der Schaltung ist. Lösung: 257814549 Seite 1 W. Baumberger L ist die Speicherdrossel. Während der ON-Phase liegt sie unmittelbar an der Eingangsspannung und nimmt magnetische Energie auf, während der OFF-Phase entlädt sie sich via die Freilaufdiode D. M ist der Leistungsschalter, ein MOSFET oder ein Bipolartransistor. Das Signal an dessen Gate bestimmt die Dauer von ON- und OFF-Phase. D ist die Freilaufdiode, in der Regel eine Schottky-Diode. Sie sperrt während der ON-Phase und leitet zumindest während eines Teils der OFF-Phase. C ist der Speicherkondensator. Er ist beim Aufwärtswandler notwendig, da die Speicherdrossel L während der ON-Phase ganz vom Ausgang abgetrennt ist und somit keine Energie liefern kann. b) Aufgabe: Wie nennt man den Aufwärtswandler im deutschen und im angelsächsischen Sprachraum auch noch? Nennen Sie je eine Bezeichnung. Lösung: Hochsetzsteller oder boost converter 3) Abwärtswandler a) Aufgabe: Was ist der grundlegende Vorteil des synchronen gegenüber dem konventionellen Abwärtswandler mit Freilaufdiode? Lösung: Der synchrone Abwärtswandler vermeidet den Spannungsabfall über der Freilaufdiode, der auch bei guten Schottky-Dioden und mässigen Strömen selten unter 0.3 V zu liegen kommt, weitgehend. Dies erlaubt v.a. bei Abwärtswandlern mit sehr tiefen Ausgangsspannungen (z. B. Uaus = 1.0 V für Prozessor-Cores) einen deutlich höheren Wandlerwirkungsgrad. b) Aufgabe: Angenommen, die Eingangsspannung Uein sei 12 V und das Tastverhältnis d1 des Schaltsignals von M1 sei 10% (entsprechend dasjenige von M2 d2 = 90%): Wie gross ist die Ausgangsspannung Uaus? Lösung: Bei Abwärtswandlern gilt unter Vernachlässigung der Verluste und des Spannungsabfalls über der Freilaufdiode (d = Tastverhältnis des Serie-FET = d1): U aus d U ein = 1.2 V In synchronen Abwärtswandler ist die Näherung sogar genauer als beim konventionellen Abwärtswandler, und zwar wegen dem weitgehenden Wegfall des Spannungsabfalls über der Freilaufdiode. c) Aufgabe: Berechnen Sie die Gesamtverlustleistung des Wandlers bei d1 = 10% und Iaus = 3 A, wenn der Restwiderstand jedes FET's RDS,ON = 0.01 und der Gleichstromwiderstand der Spule RLS = 0.01 ist! Die Schaltverluste der FET's können Sie vernachlässigen. Lösung: Für die Gesamtverlustleistung erhält man: 2 2 d1 RDS,ON1 d 2 RDS,ON 2 RLS I aus RDS,ON RLS 0.18 W PD,tot I aus Bemerkung: Mit einer Ausgangsleistung Paus = 3.6 W (3 A bei 1.2 V gemäss Teilaufgabe b)) erhält man einen Wirkungsgrad von: d) Paus Paus 95% Pein Paus PD ,tot Aufgabe: Weshalb arbeiten moderne Wandler mit einer höheren Schaltfrequenz als früher (ca. 1 MHz gegenüber 0.1 MHz vor rund 15 Jahren)? Nennen Sie den wichtigsten Grund! 257814549 Seite 2 W. Baumberger Lösung: Eine höhere Schaltfrequenz erlaubt bei gegebenen Verlusten und gegebener Welligkeit den Einsatz einer physisch kleineren Speicherdrossel (weniger L bei gleichem Strom) und eines kleineren Glättungskondensators. Bemerkung: Praktikabel wurden die höheren Schaltfrequenzen erst mit der Verfügbarkeit schnellerer (kapazitätsärmerer) FET's, da ansonsten die Schaltverluste bei den hohen Frequenzen eine dominierende Rolle spielen würden. 4) Flyback-Wandler a) Weshalb ist der Flyback-Wandler die am weitesten verbreitete DC-DC-Wandlertopologie für kleine und billige Netzteile (z. B. für Notebook-Computer oder Handy-Ladegeräte)? Nennen Sie drei dafür relevante Merkmale oder Eigenschaften. Lösung: Folgende Eigenschaften sprechen für den Flyback-Wandler in solchen Anwendungen: - Er benötigt wenige Bauteile (lediglich eine geringfügig komplexere Drossel als ein Aufwärtsoder ein Abwärtswandler), d.h. er ist billig. - Durch den Einsatz einer Drossel mit zwei getrennten Wicklungen kann die aus Sicherheitsgründen erforderliche Netztrennung einfach realisiert werden. - Ein Flyback-Wandler ist gegenüber einem konventionellen Netzteil mit 50 Hz-Trafo und nachgeschaltetem Ab- oder Aufwärtswandler sehr viel kleiner und leichter. - Ein Flyback-Wandler ist gegenüber einem konventionellen Netzteil mit 50 Hz-Trafo und nachgeschaltetem Linearregler kleiner und leichter und hat zudem einen besseren Wirkungsgrad. - Durch das frei wählbare Windungsverhältnis kommt der Flyback-Wandler selbst bei extremen Verhältnissen von Ausgangs- zu Eingangsspannung ohne extreme Tastverhältnisse aus. - Durch ein (automatisches) Anpassen des Tastverhältnisses lassen sich grosse Netzspannungsbereiche abdecken (Weitbereichsnetzteil). 5) Leistungsschalter mit MOSFET's a) Aufgabe: Nennen Sie zwei Vorteile von MOSFET's gegenüber Bipolartransistoren in Anwendungen dieser Art. Lösung: Folgende Eigenschaften sprechen für den Einsatz von Power-MOSFET's in Schaltanwendungen: - MOSFET's benötigen weder im ON- noch im OFF-Zustand eine statische Steuerleistung. - MOSFET's weisen keine (minoritätsträgerbedingte) Sperrverzögerung auf und sind deshalb tendenziell schneller zu schalten als Bipolartransistoren. - Ein MOSFET verhält sich im ON-Zustand wie ein echter Widerstand, während der Bipolartransistor eine Restspannung aufweist (flache UCE-IC-Kennlinie in der Nähe des Kennlinienursprungs). - MOSFET's haben wegen ihres spezifischen Temperaturverhaltens (positiver Temperaturkoeffizient von RDS,ON) keinen Second Breakdown, wie er bei bipolaren Leistungstransistoren zuweilen ein Problem darstellt (Konzentration des Kollektorstromes in einem kleinen Teil des Chips wegen unterschiedlicher Temperaturverteilung). b) Aufgabe: Skizzieren Sie den Verlauf der Steuerspannung UGS(t) sowie der Drainspannung UDS(t) während des Einschaltvorgangs unter der Annahme, dass der Treiber einen Spannungsschritt von 0 auf UGS,max erzeugt und während des Umschaltens einen konstanten Strom IGT liefert (Treiber mit Strombegrenzung). Sie sollen dabei die Eingangs- und die Rückwirkungskapazität des FET berücksichtigen. 257814549 Seite 3 W. Baumberger Lösung: Während dem Abfall der Drain-Source-Spannung verharrt die Steuerspannung am Gate auf einem konstanten Wert in der Gegen der Schwellenspannung des FET Uth, da in dieser Phase die Gate-Drain-Kapazität umgeladen wird. c) Aufgabe: Berechnen Sie die für den ganzen Umschaltvorgang vom Treiber zu liefernde Ladung QG unter folgenden Voraussetzungen: Gate-Source- und Gate-Drain-Kapazitäten des FET spannungsunabhängig, CGS = 1.0 nF, CGD = 100 pF; Steuerspannung im eingeschalteten Zustand UGS,max = 10 V; Treiberstrom IGT = 1.0 A; Schaltspannung auf der Lastseite U+ = 100 V, Schwellenspannung des FET Uth = 4.0 V. Lösung: Die Lösung der Aufgabe ist im Falle konstanter Kapazitäten CGS und CGD denkbar einfach: Es reicht, die Differenz der Ladung der Kapazitäten vor und nach dem Umschaltvorgang zu bilden. Es kommt die für die Ladung einer Kapazität relevante Formel Q = CU zum Zug. Vor dem Umschaltvorgang hat CGS keine Ladung (UGS = 0), an der Kapazität CGD liegt eine Spannung UGD = -100 V (Vorzeichen s. Schemaskizze). Somit gilt für die Anfangsladung: QOFF U GD,OFF CGD 100V 100 pF -10 nC Nach dem Umschalten liegen an CGS resp. CGD jeweils +10 V. Somit erhält man für die Endladung: QON U GD,ON CGD U GS ,ON CGS 10V 100 pF 10V 1000 pF +11 nC Die gesamte Ladungsdifferenz ist somit: QG QON QOFF 21 nC d) Aufgabe: Berechnen Sie auf Grund der in Teilaufgabe c) berechneten Gateladung QG die Schaltzeit tON (Anstieg von UGS = 0 auf UGS,max). Lösung: Hier kommt die Definitionsgleichung für die elektrische Ladung zum Zug: Q=It. Somit erhält man für die Umladezeit: t ON QG 21nC 21 ns I GT 1A Bemerkung: Alle Zahlenwerte sind realistisch für einen zeitgenössischen n-Kanal-MOSFET, der 10 A bei 100 V mit Reserve schalten kann (Bsp.: IRFR13N15), allerdings sind die Kapazitäten in der Realität alle stark spannungsabhängig, so dass man wenn immer möglich mit den Ladungswerten für QG aus dem Datenblatt arbeiten sollte. 257814549 Seite 4 W. Baumberger