Elektronik1 - baumberger hochfrequenzelektronik

Werbung

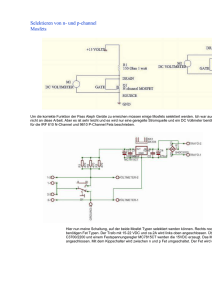

Elektronik 1 MUSTERLÖSUNG zur Schlussprüfung vom 27. Juni 2012 1) Grundlagen a) Aufgabe: Nennen Sie drei charakteristische Kenngrössen eines Operationsverstärkers und geben Sie an, wie gross diese bei einem idealen Operationsverstärker sind. Lösung: Folgende Eigenschaften können genannt werden: b) - Die Leerlaufverstärkung ist sehr hoch, idealerweise gegen unendlich, in realen OP's bei tiefen Frequenzen mindestens einige 103 bis einige 106. - Die Eingangsimpedanz zwischen invertierendem und nichtinvertierendem Eingang ist sehr hoch, idealerweise unendlich, real einige 100 k bis in den T-Bereich parallel zu wenigen pF. - Die Ausgangsimpedanz ist nahe 0, real im Bereich wenige . - Die Gleichtaktverstärkung ist idealerweise 0, real bei tiefen Frequenzen viele 10 dB bis über 100 dB geringer als die Leerlaufverstärkung. Aufgabe: Ein invertierender Verstärker habe eine Spannungsverstärkung vU = -200. Wie gross ist dessen Verstärkung in dB? Lösung: vU ,dB 20 log vU 46 dB c) Aufgabe: Die Flussspannung UF einer Schottky-Diode HSMS-2800 bei 10 A und -25C ist vom Hersteller mit 0.25 V spezifiziert. Wie gross dürfte UF bei -50C sein? Lösung: Mit der Faustregel für den Temperaturkoeffizienten von -2 mV/K erhält man 25C mal 2 mV mehr, also 0.30 V. d) Aufgabe: Wodurch unterscheiden sich pn- von Schottky-Dioden im Aufbau? Lösung: Während pn-Dioden aus, wie der Name sagt, einem Kontakt von p- und ndotiertem Halbleitermaterial besteht, verwenden Schottky-Dioden einen Kontakt zwischen einem speziellen Metall und n-dotiertem (selten auch p-dotiertem) Halbleiter. e) Aufgabe: Nennen Sie zwei Eigenschaften, in denen sich pn- und Schottky-Dioden wesentlich unterscheiden und erklären Sie, wo diese Eigenschaften wichtig sind. Lösung: Folgende Eigenschaften können genannt werden: f) - Die Schottky-Diode weist eine deutlich kleiner Flussspannung UF auf als pn-Dioden. Dies vermindert z. B. in DC-DC-Konvertern oder Leistungsgleichrichtern die Verluste. - Die Schottky-Diode zeigt gegenüber der pn-Diode keine Sperrverzögerung, da keine Minoritätsträger am Stromfluss beteiligt sind. Dies vermindert Schaltverluste in DCDC-Konvertern und macht höhere Schaltfrequenzen (heute im MHz-Bereich) überhaupt erst möglich. - Schottky-Dioden weisen wesentlich höhere Sperrströme und geringere Sperrspannungen auf als pn-Dioden. Dies verhinderte bisher ihren Einsatz in Schaltnetzteilen für höhere Spannungen als ca. 100 V. Aufgabe: Wie gross ist der Wirkungsgrad moderner, zur kommerziellen Stromerzeugung verwendeter Solarzellen und was ist der aktuelle Grosshandelspreis pro Watt Leistung bei maximaler Einstrahlung? 481378459 Seite 1 W. Baumberger Lösung: Kommerzielle Solarzellen erreichen rund 15% Wirkungsgrad und kosten rund 1 CHF/W. 2) Invertierender und nichtinvertierender Schmitt-Trigger a) Aufgabe: Bei welchen Eingangsspannungen Uein+ und Uein- schaltet der Schmitt-Trigger vom einen in den anderen Zustand? Lösung: Da die Schaltschwelle dann erreicht wird, wenn die Eingangsdifferenzspannung UD zwischen invertierendem und nichtinvertierendem Eingang durch null geht, reicht es, die Spannung am nichtinvertierenden Eingang UP1,2 für die beiden möglichen Ausgangsspannungen Uaus1,2 (= 12 V) zu berechnen. Man erhält: U ein1, 2 U P1, 2 U aus1, 2 b) R2 1 (+12 V, -12 V) = 2 V R1 R2 6 Aufgabe: Zeichnen Sie das Schaltschema und dimensionieren Sie die Werte der Widerstände für einen nichtinvertierenden Schmitt-Trigger mit den Schaltschwellen Uein+ = +3.0 V und Uein- = -3.0 V. Die Speisespannung und der Operationsverstärker sollen identisch sein wie in Teilaufgabe a). Lösung: Das Schaltschema ist unten gezeigt. Die Schaltschwelle ist auch hier erreicht, wenn UD = 0 ist; im speziellen hier Fall muss UP = 0 sein. Die Lösung erhält man mit dem Überlagerungssatz: Am Eingang liegen +3 V, am Ausgang -12 V und es muss UD = 0 resultieren, also: U P U ein,1 Mit R2 R1 U aus,1 0 R1 R2 R1 R2 U ein1 1 und freier Wahl von R1 = 10 k erhält man: U aus1 4 R2 U aus R1 40 k U ein 3) Integrator mit konventionellem und mit Single Supply-Operationsverstärker a) Aufgabe: Nennen Sie eine Ihnen bekannte Anwendung eines Integrators! Lösung: Folgende Anwendungen können genannt werden: b) - Rechteck-Dreieck-Generator - Soft-Start-Schaltung in DC-DC-Konvertern Aufgabe: Am Eingang des Integrators liegt ein positiver Spannungspuls der Amplitude +1.0 V und der Dauer 400 s (Rechteckimpuls, s. Figur unten). Wie gross ist die Spannung am Ausgangs des Integrators nach dem Puls, wenn die Ausgangsspannungs vor dem Puls 0.0 V war? Skizzieren Sie auch den Spannungsverlauf am Ausgang. 481378459 Seite 2 W. Baumberger Lösung: Da C am Anfang Ladung 0 hat, muss auch dessen Spannung dann 0 sein. Anschliessend lädt während 400 s ein konstanter Strom I von 50 A (Uein/R) den Kondensator. Am Ende des Pulses hat er also eine Ladung von: Q t U ein =20 nC R Die durch diese Ladung am Kondensator aufgebaute Spannung Uaus ist: U aus U Q t ein -2.0 V C RC Das Vorzeichen ergibt sich einerseits aus der Tatsache, dass der Operationsverstärker an seinem invertierenden Eingang gesteuert wird, andererseits aus der Parallelität von Strom- und Spannungspfeil am Kondensator: Er wird geladen, also ist er ein Verbraucher. c) Aufgabe: Oft wird zum Gegenkopplungskondensator C des Integrators ein hochohmiger Widerstand parallel geschaltet. Erklären Sie, was der Zweck dieses Widerstandes ist. Lösung: Auf Grund von Nichtidealitäten des Operationsverstärkers wie Bias-Ströme in die Eingänge und Offset-Spannung würde die Ausgangsspannung des Integrators auch bei Eingangsspannung 0 langsam wegdriften, bis der Ausgang sättigt. Ein Parallelwiderstand über C leitet den Bias-Strom ab und ermöglicht ein Kompensieren der Eingangs-Offset-Spannung durch einen konstanten kleinen Offset am Ausgang.Das Wegdriften wird so verhindert. d) Aufgabe: Skizzieren Sie die Schaltung eines Integrators mit Single SupplyOperationsverstärker (unipolare Speisespannung +5 V). Tipp: Der nichtinvertierenden Eingang verlangt eine besondere Behandlung (ohne Berechnung der Bauteile). Lösung: Der nichtinvertierende Eingang muss auf eine Spannung zwischen 0 (negative Speisung) und VCC (+5 V) angehoben werden, damit der Integrator weiterhin in beide Richtungen ausgesteuert werden kann. In der Regel wählt man die Hilfsspannung VCC/2, so dass die beiden Spannungsteilerwiderstände den selben Wert haben (RP, s. Schema). 481378459 Seite 3 W. Baumberger 4) Konstantstromquelle a) Aufgabe: Die Referenzspannung URef sei 1.2 V. Dimensionieren Sie den Spannungsteiler R1, R2 so, dass die Spannung am nichtinvertierenden Eingang des Operationsverstärkers UP = 200 mV wird. Lösung: Man benötigt hier die Spannungsteilerformel. Einen der Widerstände wählt man vor, z. B. R2 = 10 k. Nach R1 aufgelöst und eingesetzt erhält man: U Re f R1 R2 1 50 k UP b) Aufgabe: Wie gross muss R3 gewählt werden, damit der Diodenstrom ID = 350 mA wird? Den Einfluss des Basistroms des Transistors T können Sie für diese Rechnung vernachlässigen. Lösung: Da die Differenzspannung am Operationsverstärkereingang UD = 0 sein muss und UP = 0.2 V, muss auch UN = 0.2 V sein; dies ist gerade der Spannungsabfall über R3, durch den der LED-Strom fliesst (bei Vernächlässigung des Basisstroms wie vorgegeben). Somit erhält man für R3: R3 c) UN 0.57 ID Aufgabe: Erklären Sie, wie sich der bisher vernachlässigte Basistrom von T auf die Genauigkeit des erzeugten Stroms ID auswirkt (Vorzeichen und Grössenordnung des Fehlers). Wie liesse sich die Schaltung modifizieren, um diesen Fehler gänzlich zu eliminieren? Lösung: Der für die Steuerung des Bipolartransistors T notwendige Basisstrom fliesst ebenfalls durch R3 ab, d.h. der Strom durch R3, auf den der Operationsverstärker regelt, ist um den Basistrom grösser als der LED-Strom (Kollektorstrom). Geht man von einer Stromverstärkung von T von ca. 100 aus, ist der LED-Strom damit rund 1% geringer als gewünscht. Der Fehler wird erst grösser, wenn T in die Sättigung gerät, d.h. UCE sehr klein wird (unter etwa 200 .. 400 mV). 5) Aufbau und Eigenschaften von MOSFET's a) Aufgabe: Skizzieren Sie den Aufbau eines n-Kanal-Enhancement-MOSFET's für Logikanwendungen (lateraler MOSFET) und beschreiben Sie dessen wichtigste Bestandteile (Kurzbeschreibung der Funktion oder Bedeutung jedes Bestandteils). Lösung: Der einfachstmögliche FET-Querschnitt ist in unten stehender Figur gezeigt. Die schwarz schraffierten Flächen sind Metallisierungen zur Kontaktierung von Source-, Drain- und Bulk- (Substrat-) Anschluss. Durch eine geeignete Auswahl des Metalls entstehen hier ohmsche Kontakte, keine Schottky-Kontakte. 481378459 Seite 4 W. Baumberger Ebenfalls schwarz schraffiert ist das Gate, also die Steuerelektrode. Dieses ist aus Metall oder Polysilizium. Die blau schraffierten Flächen (n+) sind stark n-dotiertes Halbleitermaterial. Sie bilden einen niederohmigen Übergang zwischen S- und D-Metallisierung, also den Kanalanschlüssen, und dem sich im schwach dotierten p-Halbleiter bei Anlegen einer genügend positiven Gate-Spannung durch Inversion ausbildenden Kanal. Der p-Halbleiter (p-, rot gepunktet) ist das Grundmaterial, auf dem der FET aufgebaut wird. Das Gate-Oxyd (gelb) trennt Gate und Kanal physisch und isoliert elektrisch. Diese Schicht ist aus SiO2 und ist extrem dünn. Da es sich um einen Enhancement- (Anreicherungs-) FET handelt, ist für den n-Kanal keine n-dotierte Schicht unmittelbar unter dem Gate notwendig. b) Aufgabe: Wodurch unterscheidet sich ein Enhancement- von einem Depletion-MOSFET (jeweils n-Kanal) im Aufbau und in dessen elektrischen Eigenschaften? Lösung: Der Depletion-FET hat unmittelbar unter dem Gate-Oxid eine dünne n-dotierte Schicht. Sie sorgt dafür, dass der FET-Kanal bereits bei einer Gate-Spannung von 0 V mehr oder weniger stark leitet. Er muss durch eine negative Gate-Spannung gesperrt werden. Man nennt den Depletion- (D-, auch Verarmungs-) FET selbstleitend, den Enhancement(E-, auch Anreicherungs-) FET selbstsperrend. Zur Verdeutlichung zeigt folgende Figur die beiden Transferkennlinien (Drainstrom in Funktion der Gate-Source-Spannung). Die Schwellenspannungen des D- resp. des E-FET sind negativ (-6 .. -0.5 V) resp. positiv (+1 .. +4 V). 6) Spannungsstabilisierung mit Z-Diode a) Aufgabe: Berechnen Sie den erforderlichen Vorwiderstand R1, und zwar so, dass der Diodenstrom IZ,min 5 mA nie unterschreitet. Den differenziellen Widerstand der Z-Diode können Sie vernachlässigen. Lösung: Der minimale Diodenstrom fliesst bei minimaler Eingangsspannung (10 V) und maximalem Laststrom (20 mA). Durch den Vorwiderstand fliesst die Summe von Dioden(5 mA) und Laststrom (20 mA), also 25 mA. Somit gilt für dessen Wert (UZ = ZDiodenspannung): R1 b) U ein,min U Z I Z ,min I L ,max 6.7V 268 25mA Aufgabe: Der Hersteller der Diode spezifiziert eine max. Verlustleistung von 250 mW. Überprüfen Sie, ob Ihre Dimensionierung von Aufgabe a) unter allen Umständen diesen Grenzwert einhält. 481378459 Seite 5 W. Baumberger Lösung: Der maximale Diodenstrom fliesst bei maximaler Eingangsspannung (20 V) und minimalem Laststrom (0 mA): I Z ,max U ein,max U Z R1 20V 3.3V 62 mA 268 Die in der Z-Diode umgesetzte Verlustleistung ist demnach: PD ,max I Z ,max U Z 206 mW Die Herstellerspezifikation wird also gerade noch eingehalten. 7) Abwärtswandler a) Aufgabe: Wie gross wird das Tastverhältnis des im IC integrierten Leistungsschalters (ON-Zeit zu Periodendauer) bei den im Schema angegebenen Spannungsverhältnissen sein? Vernachlässigen Sie für die Rechnung alle unerwünschten Spannungsverluste. Lösung: Das Tastverhältnis d entspricht gerade dem Verhältnis von Aus- zu Eingangsspannung: d b) U aus 0.417 U ien Aufgabe: Wie gross muss L1 gewählt werden, wenn die Welligkeit des Spulenstroms 30% des nominellen Laststroms von 2.0 A betragen soll? Lösung: Die ON-Zeit beträgt (mit d aus Teilaufgabe a)): t ON d 2.8 s f Während dieser Zeit wird die Spule "geladen" und ihr Strom steigt um I = 0.6 A an (30% von 2 A). Über der Spule liegt während dieser Zeit eine Spannung von U = 7 V. Für die Induktivität, deren Strom während t = tON bei Anliegen von U um I ansteigt, erhält man: L U c) t 32 H I Aufgabe: Sogenannte synchrone Abwärtswandler erreichen einen höheren Wirkungsgrad als einfache Wandler wie der LM2952HV. Erklären Sie in kurzen Sätzen, evtl. auch unter Zuhilfenahme einer Skizze, wodurch sich der synchrone Abwärtswandler unterscheidet und weshalb er einen besseren Wirkungsgrad erreicht. Lösung: Beim synchronen Abwärtswandler wird die Freilaufdiode D1 mit ihrem unvermeidlichen Spannungsverlust in der Region einiger 100 mV durch einen weiteren Leistungsschalter (MOSFET) ersetzt. Der Spannungsabfall kann dadurch beliebig minimiert werden (praktisch auf einige 10 mV). Allerdings muss dieser zweite MOSFET ebenfalls gesteuert werden, und zwar mit einem exakten Timing in Bezug auf den Längsschalter. 8) Spezifikationen von Power-MOSFETs und thermisches Design a) Aufgabe: Wie gross ist die maximale Verlustleistung des FET's, wenn er ohne Kühlkörper bei 25C Umgebungstemperatur eingesetzt wird? Lösung: Hier benötigt man RJA (62.5C/W, Wärmewiderstand zwischen Halbleiter und Umgebung) sowie die maximale Chip-Temperatur (TJ,max = 150C). Man erhält: 481378459 Seite 6 W. Baumberger Pmax 1 b) TJ ,max TA RJA 2.0 W Aufgabe: Wie gross ist der maximale Dauerdrainstrom des Bauteils, wenn es gelingt, die Kühlkörpertemperatur auf +75C zu halten und der thermische Widerstand zwischen Kühlkörper und FET-Gehäuse 1.0C /W beträgt? Lösung: Hier benötigt man den gesamten Wärmewiderstand zwischen Chip und Kühlkörper, welcher sich aus RJC (chip to case) und Übergangswiderstand zwischen Gehäuse und Kühlkörper (1.0C /W) zusammensetzt, total also Rtot = 5.63C /W. Man erhält mit TK = Kühlkörpertemperatur: Pmax 2 TJ ,max TK Rtot 13.3 W Zusammen mit dem ganz oben im Datenblattauszug spezifizierten ON-Widerstand des FET (RDS(on) = 1.35 ) berechnet man den korrespondierenden maximalen Drainstrom: I max c) Pmax 2 3.1 A RDS ( on) Aufgabe: Erklären Sie die Bedeutung der Spezifikation für die "Gate Charge" (4 nC). Sie können dies anhand eines Schaltungsbeispiels (Anwendung des FET als Leistungsschalter) und eines Zahlenbeispiels tun. Lösung: Die Gate-Ladung ist die gesamte Ladung, die zum vollständigen Ein- oder Ausschalten des FET mit Last an einer bestimmten Drain-Spannung ins Gate hinein (einschalten) oder aus diesem heraus (ausschalten) gepumpt werden muss (Integral des Gate-Stroms über die gesamte Umschaltzeit). Zusammen mit der Information über den Maximalstrom, den ein Gate-Treiber liefern kann, kann so leicht die Schaltzeit berechnet werden. Die Spezifikation der Gate-Ladung anstatt der FET-Kapazitäten ist für den Anwender sehr viel handlicher, da letztere eine ausgeprägte Spannungsabhängigkeit aufweisen (d.h. nicht konstant sind). Die Gate-Ladung hängt stark von der Drain-Spannung ab, an der die Last hängt, da die Rückwirkungskapazität (CGD) einen wesentlichen Beitrag zu dieser Ladung beisteuert.. 481378459 Seite 7 W. Baumberger