Komplett-Download

Werbung

Technische Universität Ilmenau

Fakultät für Informatik und Automatisierung

Institut für Technische Informatik und Ingenieurinformatik

Lehrgebiet Methodik des Hardwareentwurfs

Script zur Lehrveranstaltung

Analoge und Digitale Schaltungen

Studiengang Elektrotechnik/Automatisierungstechnik

Teil: Digitale Schaltungen

von Dr.-Ing. Norbert Hirt

Digitale Schaltungen

Inhalt

Einleitung

1.

Elektronische Bauelemente

1.1

1.2

1.3

1.4

1.5

1.6

1.7

2.

Elektronische Schalter

2.1

2.2

2.3

2.4

2.5

(42 Seiten)

Widerstände

1.1.1

Lineare Widerstände

1.1.2

Fotowiderstände

1.1.3

Nichtlineare Widerstände

1.1.3.1 Varistoren

1.1.3.2 Heißleiter (NTC-Widerstände, Thermistoren)

Kondensatoren

Induktivitäten (Übertrager, Relais)

Halbleiterdioden

1.4.1

Universal- und Schaltdioden

1.4.1.1 Statisches Verhalten

1.4.1.2 Statische Kennwerte

1.4.1.3 Dynamische Kennwerte

1.4.2

Z-Dioden

1.4.2.1 Kennlinie und Kennwerte

1.4.2.2 Anwendungsschaltungen mit Z-Diode

Bipolartransistoren

1.5.1

Statische Eigenschaften, Ersatzschaltungen und Kennwerte

1.5.2

Bipolartransistor in Analogschaltungen (Verstärker)

1.5.2.1 Arbeitspunkteinstellung und -stabilisierung

1.5.2.2 Driftverhalten

1.5.2.3 Schaltungen zur AP-Stabilisierung

1.5.3

Transistor in Digitalschaltungen

1.5.3.1 Statisches Verhalten

1.5.3.2 Zur statischen Bemessung von Transistor-Schaltstufen

1.5.3.3 Schaltzeiten des Transistorschalters

Feldeffekttransistoren (FET, unipolare Transistoren)

1.6.1

Isolierschicht-Feldeffekttransistoren (MOSFET)

1.6.2

Sperrschicht-FET

1.6.3

Statisches Verhalten von MOSFET

1.6.3.1 Ausgangskennlinienfeld

1.6.3.2 Ersatzschaltbild und Kennliniengleichungen

1.6.4

FET als steuerbarer Widerstand

1.6.5

Schaltstufen mit FET

1.6.6

Dynamisches Verhalten von FET-Schaltstufen

Schaltverhalten einfacher passiver Zweitore (Spannungsteiler)

1.7.1

Schaltverhalten ohmscher Spannungsteiler

1.7.2

Schaltverhalten von RC-Gliedern

1.7.3

Schaltverhalten einer Induktivität

1.7.4

Zur Lösung linearer Differentialgleichungen

Idealer und realer Schalter

2.1.1

Statisches Verhalten

2.1.2

Dynamisches Verhalten

Schaltstufen mit Transistoren

2.2.1

Schaltstufen mit Bipolartransistor

2.2.2

Schaltstufen mit Unipolartransistor

2.2.3

Zur statischen Dimensionierung

Lastverhalten von Transistorschaltstufen

2.3.1

Statische Lastschaltungen

2.3.2

Schalten kapazitiver Lasten

2.3.3

Schalten induktiver Lasten

Gegentaktschaltstufen

Ungesättigte Transistorschalter

(16 Seiten)

Digitale Schaltungen

3.

Logische Elemente und Schaltungen

3.1

3.2

3.3

3.4

3.5

4.

Logische Grundfunktionen

Signalpegel in logischen Schaltungen

3.2.1

Positive und negative Logik

3.2.2

Pegelbereiche und Übertragungskennlinie

Kenngrößen logischer Schaltungen

3.3.1

Statische Kennwerte

3.3.1.1 Spannungspegel, Störabstand

3.3.1.2 Eingangs- und Ausgangsströme, Lastfaktoren

3.3.1.3 Ausgangsstufen

3.3.2

Schaltzeiten

3.3.3

Verlustleistung

Schaltungstechnische Realisierung elektronischer Verknüpfungsglieder

3.4.1

Schaltungen in Kontakttechnik

3.4.2

Dioden- und Transistorschaltungen

3.4.2.1 Diodenschaltungen

3.4.2.2 Transistorschaltungen

Zum Entwurf logischer Schaltungen

3.5.1

Entwurfsdarstellung und -verifikation

3.5.2

Simulationsarten

3.5.2.1 Circuit-Simulation

3.5.2.2 Switch-Level-Simulation

3.5.2.3 Logik-Simulation

3.5.2.4 Mixed-Mode-Simulation

Digitale Schaltkreisfamilien

4.1

4.2

4.3

4.4

4.5

4.6

4.7

4.8

(20 Seiten)

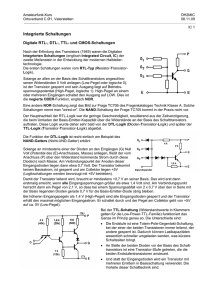

Dioden-Transistor-Logik (DTL, DZTL)

TTL-Schaltkreise

4.2.1

Überblick

4.2.2

Schaltung des NAND-Gatters 7400

4.2.3

TTL-Schaltungen mit offenem Kollektor

4.2.4

TTL-Schaltungen mit Tristate-Ausgängen

4.2.5

TTL-Schaltungen mit Schottky-Transistoren (STTL)

4.2.6

Kennwerte von TTL-Schaltungen

4.2.6.1 Signalpegel und statischer Störabstand

4.2.6.2 Eingangs- und Ausgangsströme

4.2.6.3 Dynamische Kennwerte

ECL-Schaltkreise

4.3.1

Allgemeines

4.3.2

Grundschaltung in ECL

4.3.3

Logische Verknüpfung in ECL

Integrierte Injektions-Logik (I2 L)

4.4.1

Grundschaltung der I2 L-Logik

4.4.2

Logische Verknüpfung bei I2 L-Schaltungen

4.4.3

Verzögerungszeit bei I2 L

n-MOS-Schaltkreise

CMOS-Schaltkreise

4.6.1

CMOS-Grundschaltungen

4.6.2

Transmissionsgatter, Analogschalter

4.6.3

Tristate-Schaltungen in CMOS-Technik

4.6.4

Kennwerte von CMOS-Schaltkreisen

4.6.4.1 Eingangskennwerte

4.6.4.2 Ausgangsstufen und -kennwerte

4.6.5

High-speed-CMOS-Baureihe 74 HC / 74 HCT

BICMOS-Schaltkreisreihe 74 BCT

Gallium-Arsenid-MESFET-Schaltkreise

(28 Seiten)

Digitale Schaltungen

5.

Rückgekoppelte Kippschaltungen

5.1

5.2

5.3

5.4

6.

Kodier- und Dekodierschaltungen

6.1

6.2

7.

7.2

8.

8.3

8.4

8.5

8.6

( 6 Seiten)

Dualzähler

7.1.1

Asynchrone Dualzähler

7.1.2

Synchrone Dualzähler

Dezimalzähler

7.2.1

Asynchrone BCD-Zähler

7.2.2

Synchrone BCD-Zähler

Interface-Schaltungen

8.1

8.2

(10 Seiten)

Kodewandler

6.1.1

Allgemeine Kodewandler

6.1.2

Dekodierer (Decoder)

6.1.3

Kodierer

Multiplexer und Demultiplexer

6.2.1

Demultiplexer

6.2.2

Multiplexer

6.2.3

Anwendungen von Multiplexern und Demultiplexern

6.2.4

Multiplexer / Demultiplexer als Funktionsspeicher

6.2.4.1 Multiplexer als Funktionsspeicher

6.2.4.2 Demultiplexer als Funktionsspeicher

Zähler und Frequenzteiler

7.1

(20 Seiten)

Flipflop-Schaltungen

5.1.1

Basis-Flipflop

5.1.2

Taktgesteuerte Flipflops

5.1.3

Logisches Verhalten von Flipflops

5.1.4

Parallel- und Schieberegister

5.1.4.1 Parallelregister

5.1.4.2 Schieberegister

Schmitt-Trigger (Schwellwertschalter)

Monoflops

5.3.1

Monoflop mit Logikgattern

5.3.2

Retriggerbare Monoflops

Impulsgeneratoren (astabile Multivibratoren)

5.4.1

Impulsgeneratoren mit Gatterschaltkreisen

5.4.2

Quarzgeneratoren

Allgemeine Betrachtungen

Pegelwandler

8.2.1

Pegelumsetzung zwischen Logikpegeln

8.2.2

Umsetzung zwischen Logikpegel und V.24-Pegel

8.2.3

Dioden-Begrenzerschaltungen für LSI-Schaltkreise

Anzeigeelemente und ihre Ansteuerschaltungen

8.3.1

LED-Anzeigeeinheiten

8.3.2

Ansteuerschaltungen für LED-Anzeigen

Optokoppler

8.4.1

Grundtypen von Optokopplern

8.4.2

Ansteuerung von LED in optischen Sendern

Busschaltungen

8.5.1

Sender mit offenem Kollektor

8.5.2

Sender mit Tristate-Stufen

Zur worst-case-Bemessung digitaler Schaltungen

8.6.1

Totales Fehlerdifferential

8.6.2

Praktisches Verfahren der Worst-Case-Analyse

8.6.3

Ersatzschaltungen für Ein- und Ausgangsstufen integrierter Schaltkreise

8.6.3.1 Ersatzschaltungen für Eingangsstufen

8.6.3.2 Ersatzschaltungen für Ausgangsstufen

8.6.4

Beispiele zur worst-case-Bemessung

(24 Seiten)

Digitale Schaltungen

9.

Halbleiterspeicher

9.1

9.2

9.3

9.4

10.

Anwendungsspezifische Integrierte Bausteine (ASICs)

10.1

10.2

10.3

10.4

11.

11.3

11.4

11.5

12.

12.4

12.5

(10 Seiten)

Allgemeiner Überblick

Störungen durch Leitungsreflexionen

11.2.1 Elektrisch lange Leitung, Wellenwiderstand

11.2.2 Schaltverhalten elektrisch langer Leitungen

Symmetrische und unsymmetrische Signalübertragung

Störungen durch Übersprechen

Störungen durch die Induktivität der Stromversorgungsleitungen

Bussysteme, Schnittstellen

12.1

12.2

12.3

(18 Seiten)

Überblick

Programmierbare logische Schaltungen

10.2.1 Prinzip

10.2.2 Varianten von PLD-Bausteinen

10.2.3 Programmier- und löschbare PLDs

10.2.4 Programmierbare Gate Arrays

Pinout und Gehäuseformen von PLDs/FPGAs

Überblick über FPGA-Familien

Störeinflüsse bei der Datenübertragung

11.1

11.2

(12 Seiten)

Allgemeiner Überblick

Festwertspeicher, ROMs

9.2.1 Zur Einteilung von ROMs

9.2.2 Schaltungstechnische Realisierung der Speichermatrix

Schreib-Lese-Speicher (RWM, RAM)

9.3.1

Statische RAMs

9.3.1.1 Aufbau und Funktionsweise

9.3.1.2 Dynamische Kenngrößen statischer RAMs

9.3.2

Dynamische RAMs

Speicher mit seriellem Zugriff

Überblick

Parallele Bussysteme

Serielle Schnittstelle, serielle Datenübertragung

12.3.1 Serielle Datenübertragung

12.3.2 Asynchrone und synchrone Datenübertragung

Einheitliche serielle Schnittstellen

12.4.1 RS-232C-, V.24-Schnittstelle

12.4.2 Schnittstellen nach der RS-422/485-Norm

Schnittstellenvergleich

(14 Seiten)

Digitale Schaltungen

Literatur:

/ 1/

Seifart, M.: Digitale Schaltungen. Verlag Technik Berlin, 1988.

/ 2/

Tietze, U.; Schenk, Ch.: Halbleiter-Schaltungstechnik.

Springer-Verlag Berlin-Heidelberg-New York 1988.

/ 3/

Kühn, E.: Handbuch TTL- und CMOS-Schaltkreise. Verlag Technik Berlin, 1985.

/ 4/

Seifart, M.: Analoge Schaltungen. Verlag Technik Berlin, 1987.

/ 5/

Roth, M.; Hirt, N.: Schaltungen für Digital-Analog- und Analog-Digital-Umsetzer.

In: Taschenbuch Elektrotechnik, Bd. 3/II (Hrsg. E. Philippow), Verlag Technik Berlin, 1988.

/ 6/

Schiffmann/Schmitz: Technische Informatik 1. Grundlagen der digitalen Elektronik.

(Springer-Lehrbuch) Springer-Verlag Berlin-Heidelberg-New-York-London-ParisTokyo-Hong Kong-Barcelona-Budapest 1993.

/ 7/

Borucki, L.: Digitaltechnik. B.G.Teubner Stuttgart 1989.

/ 8/

Beuth, K.: Digitaltechnik. Vogel Buchverlag Würzburg 1992.

/ 9/

Brauer/Lehmann: Elektronik-Aufgaben. Fachbuchverlag Leipzig 1988.

/10/

Dostál, J.: Operationsverstärker. Verlag Technik Berlin 1986.

/11/

Weißel, R.; Schubert, F.: Digitale Schaltungstechnik.

Springer Verlag Berlin-Heidelberg-New York-London-Paris-Tokyo-Hong Kong 1990.

/12/

Siegl, J.; Eichele, H.: Hardwareentwicklung mit ASIC. Einsatz und Anwendung von

CAE-Entwurfswerkzeugen (Reihe Mikroelektronik, Band 8).

Hüthig Buchverlag Heidelberg 1990.

/13/

Baumann, P./Möller, W.: Schaltungssimulation mit Design Center.

Fachbuchverlag Leipzig-Köln 1994.

/14/

Lehmann, C.: Elektronik-Aufgaben. Band II: Analoge und digitale Schaltungen.

Fachbuchverlag Leipzig-Köln 1994.

/15/

Scarbata, G.: Synthese und Analyse Digitaler Schaltungen.

R.Oldenbourg Verlag München Wien 1996

Anhang

Ü

P

Übungsaufgaben

Praktikumsaufgaben "Circuit-Simulation" (PSPICE)

Digitale Schaltungen

Einleitung

Die stürmische Entwicklung der Mikroelektronik hält seit der Erfindung des Transistors im Jahre

1948 ungebrochen an. Wesentliche Meilensteine dieser Entwicklung waren die Realisierung der

ersten integrierten Schaltungen um 1960 und die Einführung der ersten Mikroprozessoren um 1974

(einschließlich anwenderprogrammierbarer Speicher) als Vorläufer der gegenwärtigen Computer.

{ Der Integrationsgrad mikroelektronischer Bausteine und die Komplexität damit aufgebauter

elektronischer Systeme wachsen noch immer. Der technologische Stand der Halbleitertechnik

ermöglicht heute Integrationsgrade von über 105 ... 107 Transistorfunktionen pro Baustein mit

Strukturgeometrien im 100 nm - Bereich und kleiner.

Mit der Verfügung über enorme und kostengünstige Rechenleistung bietet sich die Möglichkeit,

auch komplexe Systemaufgaben mittels Software auf einer Standard-Hardware zu lösen.

Heute kann bei der technischen Realisierung digitaler elektronischer Systeme zwischen einer

"Softwarelösung" und einer "Hardwarelösung" unterschieden werden (Bild 1).

{ Bei der Softwarelösung wird eine Standard-Hardware mit Universal- oder Signalprozessoren,

Speicher- und Peripheriebausteinen verwendet. Die anwendungsspezifische Lösung wird

dann durch ein entsprechendes Hochsprachprogramm (HLL - High Level Language) erreicht.

Die Verwandtschaft zu Lösungen komplexer Softwareaufgaben ist unmittelbar zu erkennen.

{ Bei Hardwarelösungen unterscheidet man Realisierungen mit Standard-Schaltkreisen und

Anwenderspezifischen Integrierten Schaltkreisen ASICs (PLD, Standard-Zellen, Gate-Array).

Im Gegensatz zu Softwarelösungen sind Änderungen nach der Implementierung nur noch

eingeschränkt möglich.

Technische

Realisierung

Softwarelösung

Mikroprozessoren

Speicher

Peripherieschaltkreise

Hardwarelösung

Standard-IC

analog

digital

CMOS, TTL

ASICs

Semi-Kunden-IC

Kunden-IC

Standardschaltkreise

Standardschaltkreise

Gate-Array

PLD

Standard-Zelle

vollständig vorgefertigt

vollständig vorgefertigt

vorgefertigt

Änderungen durch

Programm möglich

keine Änderungen

möglich

Änderungen bedingt möglich

z.B. Verbindungen, Plazierung

vorgefertigte

Makrozellen

Bild 1: Technische Realisierung elektronischer Systeme als Hard- oder Softwarelösung

Digitale Schaltungen

Parallell zu den technologischen Fortschritten wurden und werden leistungsfähige Verfahren und

Werkzeuge für den Entwurf komplexer Systeme entwickelt (CAE - Computer Aided Engineering).

Diese CAE-Werkzeuge bieten in Verbindung mit Bauteilbibliotheken vielfältige Verifikations- und

Testmöglichkeiten im gesamten Entwurfsprozeß ohne eine physikalische Realisierung (virtuelles

Labor). Wichtigstes Werkzeug zur Schaltungsverifikation ist die Simulation (Analyse und

Modifikation am Modell). Man unterscheidet u.a. zwischen

{ Device-Simulation: Simulation von Einzelhalbleitern und geometrischen Strukturen, z.B.

zur Ermittlung von Modellparametern,

{ Circuit-Simulation: Netzwerkanalyse (meist modifizierte Knotenspannungsmethode) auf

Basis von Transistor- bzw. Makromodellen von ICs; Ergebnisse dieser

Simulation sind typisch die Spannungs-/Stromverläufe im Zeitbereich,

{ Logik-Simulation: Berechnung der logischen Zustände (1-0-X) einer Logikschaltung bei

gegebenen Eingangsbelegungen.

CAE-Entwurfswerkzeuge

(auf CAE-Workstations)

Schaltungsstruktur

Schaltungsverifikation

(Simulation)

Schaltplaneingabe

Symbolgenerierung

Circuit-Simulation

Logik-Simulation

Layouterstellung

Dokumentation

Leiterplatten

ASICs

Bild 2: Einsatzbereiche von CAE-Werkzeugen beim Schaltungsentwurf

Bei der Entwicklung einer Hardwarelösung ist der Aufwand für den Aufbau von Versuchs- und

Testschaltungen aus Standardelementen, die Verifikation und Optimierung von Teilschaltungen

wegen der Komplexität der Gesamtsysteme und aus Zeit- und Kostengründen nicht mehr zeitgemäß

bzw. muß zumindest stark reduziert werden. Der Entwurf komplexer Systemfunktionen und deren

relativ kostspielige Realisierung in Silicium erfordert zunehmend eine systematische Methodik; ein

Entwurf muß bereits vor seiner Realisierung getestet und optimiert werden.

Physikalisch-technische Beschränkungen der späteren Realisierung (Parameter, Grenzwerte,

Restriktionen, ...) müssen schon in der Konzipierungsphase berücksichtigt werden. Dazu werden

vom Entwickler solide Kenntnisse in der Schaltungstechnik, über Schaltkreistechnologien sowie

über Entwurfswerkzeuge und deren Möglichkeiten gefordert.

Das gilt im Prinzip auch für den Entwurf technischer Realisierungen mittels einer Softwarelösung.

Jede Aufgabenstellung erfordert eine spezifische, in Leistungsumfang, Kosten usw. gut angepaßte

Rechnerkonfiguration aus einem sehr breiten Spektrum von Systemkomponenten mit spezifischen

Kenngrößen. Besonders wichtig dabei ist die Festlegung und Auswahl geeigneter Schnittstellen für

die Prozeßperipherie. Dazu werden zumindestens Kenntnisse über deren technische Realisierung

und der damit verbundenen Kennwerte und Eigenschaften vorausgesetzt.

{ Zur Entwicklung effektiver Systemlösungen muß ein Entwickler i.a. über ein breites

Spektrum von Grund- und Spezialkenntnissen aus unterschiedlichen Teilbereichen verfügen,

da moderne Lösungen zunehmend als integrierte Hard-/Softwarelösungen entstehen.

{ Die Verteilung der geforderten Grund-/Spezialkenntnisse auf die einzelnen Teilbereiche ist

für die einzelnen Entwickler unterschiedlich und aufgabenspezifisch.

Digitale Schaltungen

Die schnelle Weiterentwicklung der Halbleiter- und Digitaltechnik sowie die Bereitstellung immer

neuer und/oder komplexer werdender Funktionselemente und Entwurfswerkzeuge läßt Details

rasch veralten. Wir konzentrieren uns deshalb auf allgemeingültige Grundlagen und Kentnisse zur

digitalen Schaltungstechnik. Sie sollen helfen, den aktuellen Stand der Digitaltechnik einzuschätzen

und auch künftige Weiterentwicklungen zu erfassen und richtig einzuordnen. Gleichzeitig wird

damit der notwendige Hardwarehintergrund für andere Lehrveranstaltungen geliefert.

Das vorliegende Script entstand auf der Grundlage der Manuskripte zu den Lehrveranstaltungen

Rechnertechnik im Studiengang Informatik und Analoge und digitale Schaltungen im Studiengang

Elektrotechnik/Automatisierungstechnik an der Technischen Universität Ilmenau, die seit Jahren

vom Autor als Lehrbeauftragter wahrgenommen werden.

Das Script stellt in der vorliegenden Form bewußt eine teilweise erweiterte Fassung des Inhaltes der

Lehrveranstaltung Analoge und digitale Schaltungen (Teil Digitale Schaltungen) im Studiengang

Elektrotechnik/Automatisierungstechnik dar.

Dem interessierten Studierenden wird damit die Möglichkeit gegeben, sich mit der Hardwareproblematik über den in Vorlesung, Übung und Praktikum vermittelten Stoff hinaus eigenständig

zu beschäftigen.

Das Script wird ergänzt durch eine umfangreiche Sammlung von Übungsaufgaben zur Berechnung

digitaler Grundschaltungen sowie Anleitungen zu Praktikumsversuchen mit Entwurfswerkzeugen

zur Circuitsimulation (PSPICE) .

Ilmenau, im Oktober 2003

1. Elektronische Bauelemente

1

(OHNWURQLVFKH%DXHOHPHQWH

In diesem Abschnitt werden die Kennwerte und Eigenschaften der wichtigsten Bauelemente der

elektronischen Informationsverarbeitung zusammenfassend dargestellt. Dieser Überblick ist nicht

zum Einstieg in die Problematik gedacht, sondern dient den Ausführungen in den weiteren

Abschnitten als Bestandsaufnahme für die Schaltungstechnik mit diesen Elementen.

^ Auf eine physikalische Begründung bzw. Herleitung wird an dieser Stelle bewußt verzichtet

und auf die einschlägige Fachliteratur verwiesen.

Zur Beschreibung der schaltungstechnischen Eigenschaften von Bauelementen werden praktisch

Gleichungen, Kennlinien und Ersatzschaltungen bzw. Netzwerke verwendet.

Grundlage der Beschreibung elektrischer Elemente ist ihr .OHPPHQYHUKDOWHQ (Ohmsches Gesetz).

Die entsprechenden U-I-Relationen können linear und nichtlinear sein. Man spricht deshalb auch

von linearen und nichtlinearen Bauelementen.

Widerstände, Kondensatoren, Induktivitäten (Spulen) werden als SDVVLYH Bauelemente klassifiziert.

Die Symbole als Bauelement und ideales Netzwerkelement sind identisch (Tafel 1). Dagegen

werden Transistoren oft auch als DNWLYH Bauelemente bezeichnet, obwohl sie eigentlich steuerbare

passive Widerstände sind. Ihr DNWLYHV Verhalten läßt sich grundsätzlich nur mit einer Schaltung

erzeugen, die an eine Energiequelle, typisch eine Gleichspannung, angeschlossen ist. Zu ihrer

Beschreibung werden Ersatz-Netzwerke mit mehreren Netzwerkelementen bzw. entsprechend

aufwendige Gleichungen benötigt.

Widerstand, allgemein

Fotowiderstand

Induktivität

Quarz

-

Kapazität

+

Batterie

Spannungsquelle, allgemein

Gleichspannungsquelle

Stromquelle

Masse, GND

A

K

Diode, allgemein

Universaldiode

A

K

Z-Diode

A

K

Leuchtdiode, LED

A

K

Schottky-Diode

npn-Transistor

B

B

C

C

C

B

E

A

C

K

E

pnp-Transistor

B

S

n-Kanal-FET

selbstsperrend

B

G

S

B

S

n-Kanal-FET

selbstleitend

D

D

G

Optokoppler

D

D

G

Schottky-Transistor

E

E

p-Kanal-FET

selbstsperrend

B

G

S

p-Kanal-FET

selbstleitend

Tafel 1: Schaltzeichen für Netzwerkelemente und elektronische Bauelemente

2

1. Elektronische Bauelemente

:LGHUVWlQGH

Widerstände sind passive Bauelemente, an denen ein Spannungsabfall UR entsteht, wenn sie von

einem Strom IR durchflossen werden (Ohmsches Gesetz).

^ 'HILQLWLRQVJOHLFKXQJ

UR = R . IR .

(1.1.1)

In der Wechselstromtechnik wird zusätzlich ein Scheinwiderstand (Wirk- und Blindwiderstand)

verwendet. Der Wirkanteil R wird als ohmscher Widerstand oder einfach Widerstand bezeichnet.

^ 6FKHLQZLGHUVWDQG

Z = R2 + X2

(1.1.2)

Die elektrische Energie W kann an einem Widerstand umgesetzt (Wirkwiderstand - Wärme) oder

gespeichert werden (Blindwiderstand X, vgl. Kapazität, Induktivität)

^ (OHNWULVFKH(QHUJLH

W = U. I. t

(1.1.3)

/LQHDUH:LGHUVWlQGH

Die industrielle Elektronik schafft i.a. die Voraussetzungen dafür, daß ohmsche Widerstände als

lineare konzentrierte Bauelemente betrachtet werden können. Für sehr hohe Frequenzen trifft das

immer weniger zu, hier wird das Verhalten besser durch eine R-L-C-Ersatzschaltung beschrieben

(Bild 1.1.1). Für den komplexen Scheinwiderstand Z(p) gilt dann:

Z(p) = pL +

R

1 + pCR

mit p = j* = j . 2 . f .

(1.1.4)

Es kann eine Grenzfrequenz fg angeben werden, bis zu der ein ohmscher Widerstand als solcher

einsetzbar ist. Da mit steigender Frequenz f zuerst die parasitäre Parallelkapazität C wirksam wird,

sinkt oberhalb von fg der Scheinwiderstand von Z(p) zunächst ab, wächst dann infolge des

induktiven Anteils L und übersteigt schließlich den statischen Wert R (Bild 1.1.1).

|Z(p)|

L

UR

R

R

IR

C

}

Z(p)

R

lg f

fg

Bild 1.1.1: Ohmscher Widerstand, Ersatzschaltung für hohe Frequenzen

^ Lineare Widerstände werden als Draht- oder Schicht- bzw. Filmwiderstände hergestellt (vgl.

auch Tafel 1.1.4).

^ Sie werden nach Widerstandswerten und anderen Kenngrößen (Verlustleistung, ...) eingeteilt.

Widerstände der gleichen Bauform und mit gleicher Kennfarbe werden in einer %DXUHLKH

zusammengefaßt.

1. Elektronische Bauelemente

3

:LGHUVWDQGVZHUWHXQG.HQQ]HLFKQXQJ

Nach einer Empfehlung der Internationalen Kommission für Elektrotechnik IEC sind die

Nennwerte handelsüblicher Widerstände und Kondensatoren nach sogenannten (5HLKHQ gestuft

(Tafel 1.1.1).

Die Reihen werden nach der Anzahl der Nennwerte je Dekade bezeichnet. So enthält die Reihe E 6

genau n = 6 Nennwerte je Dekade (Spalte 1 in Tafel 1.1.1). Die Stufung innerhalb der Reihen

1

erfolgt nach geometrischen Folgen und entspricht etwa dem Faktor 10 E n .

Die Prozentangaben geben die relativen Toleranzen vom Nennwert an. Die Toleranzbereiche

zwischen benachbarten Werten überlappen sich teilweise.

Wert

1

2

3

4

5

6

7

8

Reihe

Spalten

Toleranz

1,00

1,05

1,10

1,15

1,20

1,25

1,30

1,40

E 6

1

± 20 %

1,50

1,55

1,60

1,70

1,80

1,90

2,00

2,10

E 12

1, 5

± 10 %

2,20

2,30

2,40

2,55

2,70

2,85

3,00

3,15

E 24

3,30

3,45

3,60

3,75

3,90

4,10

4,30

4,50

E 48

4,70

4,90

5,10

5,35

5,60

5,90

6,20

6,50

E 96

6,80

7,15

7,50

7,85

8,20

8,60

9,10

9,55

1, 3, 5, 7 ± 5 %

1-8

± 2%

± 1%

Tafel 1.1.1: Widerstandswerte der internationalen E-Reihen

Die Kennzeichnung der Widerstandswerte am Bauelement Widerstand erfolgt durch Aufdruck

eines Buchstaben-Zahlenkodes oder eine Farbkodierung (Farbringe oder Farbpunkte). Der

Nennwert des Widerstandes wird dabei immer in Ohm angegeben.

Tafel 1.1.2 gibt die verwendeten Symbole des Buchstaben-Zahlenkodes an und zeigt Beispiele zur

Kennzeichnung von Widerständen. Der Kennbuchstabe für die Grundeinheit wird gleichzeitig als

Komma genutzt.

Nennwert

Buchstabe

Toleranz

in %

Buchstabe

Beispiel

Aufdruck

Bedeutung

Ohm

R

20

ohne

2R2

2,2 (1 ± 20 %)

Ω

Kiloohm

K

10

K

3k3 K

3,3 (1 ± 10 %)

kΩ

Megaohm

M

5

J

2M2 J

2,2 (1 ± 5 %)

MΩ

Gigaohm

Teraohm

G

T

2

1

G

F

Tafel 1.1.2: Zur Kennzeichnung der Widerstandswerte durch Buchstaben-Zahlenkode

Bei Verwendung der internationalen Farbreihe wird der Widerstandskörper mit meist 4 Farbringen

gekennzeichnet (Tafel 1.1.3).

^ Die ersten beiden Ringe kodieren die zwei Ziffern des Widerstands-Nennwertes. Der erste

Farbring liegt einem Anschluß am nächsten.

^ Der dritte Ring kodiert den Multiplikator und der vierte Ring die Toleranz vom Nennwert.

4

1. Elektronische Bauelemente

Farbe

1. Ring

1. Zahlenwert

2. Ring

2. Zahlenwert

3. Ring

Multiplikator

4. Ring

Toleranz in %

ohne

-

-

-

20

silber

-

-

10-2

-

-1

5

0

gold

-

10

10

schwarz

-

0

10

-

braun

1

1

101

1

2

2

2

3

-

4

-

5

0,5

6

0,25

7

rot

2

orange

3

gelb

3

4

grün

10

4

5

blau

10

10

5

6

10

6

10

violett

7

7

10

0,1

grau

8

8

108

0,05

9

9

weiß

9

10

-

Tafel 1.1.3: Internationaler Farbkode zur Kennzeichnung von Widerständen

=XOlVVLJH9HUOXVWOHLVWXQJ7HPSHUDWXUNRHIIL]LHQW

Die Nenn(verlust)leistung PN ist die bis zu einer bestimmten Nenntemperatur a = N zulässige

Leistung, die an einem Widerstand in Wärme umgesetzt wird. Erfolgt der Einsatz bei höheren

Temperaturen bis zu max , so muß die Verlustleistung auf den zulässigen Wert PZ reduziert werden

(Bild 1.1.2).

zulässige Verlustleistung

PZ

PN

PN

für a > N

PZ =

max − a P N für a P N

max − N

1

0,5

0

ϑN

ϑ max

Bild 1.1.2: Zulässige Verlustleistung für Widerstände

ϑa

(1.1.5)

1. Elektronische Bauelemente

5

7HPSHUDWXUNRHIIL]LHQW7.

Bei einer Temperaturänderung ändert sich auch der Widerstandswert. Als Maß dafür dient der

Temperaturkoeffizient TK. Er ist materialabhängig und gibt die auf den Nennwert bei a = 20°C

bezogene Änderung R des Widerstandswertes für 1 Grad Temperaturänderung an.

TKR = RR

. T

R = R 20 (1 + TK R . T ) ,

(1.1.6)

Bei Reihen- bzw. Parallelschaltung von zwei Widerständen gilt für den resultierenden TKR

^ Reihenschaltung

TKR =

R 1 TK R1 + R 2 TK R2

R1 + R2

mit R = R1 + R2

^ Parallelschaltung

TKR =

R 1 TK R2 + R 2 TK R1

R1 + R2

mit R = R 1+ R2

1

2

R .R

(1.1.6 a)

(1.1.6 b)

Einen Überblick über Temperaturkoeffizienten und deren Stabilität für verschiedene Widerstände

und Widerstandsverhältnisse zeigt Tafel 1.1.4.

TK für Einzelwiderstand

Widerstandsverhältnisse

absolut

typische Drift

pro Jahr

TK

typische Drift

pro Jahr

in ppm

in ppm

in ppm

in ppm

Laborgewickelte Drahtwiderstände

1

2-5

0,5

1-5

Industrielle Präzisionsdrahtwiderstände

2

15 - 50

1-2

10 -30

Filmwiderstände

3

25

1,5

15 - 40

Gedruckte

Spezial-Dünnfilmwiderstände

5 - 15

25 - 50

3-5

25 - 50

Dünnfilmwiderstände

20 - 60

200 - 400

2-6

100 - 400

Laserabgeglichene

20 - 60

200 - 600

3 - 10

200 - 600

50 - 100

500 - 1000

5 - 50

200 - 2000

50 - 100

500 - 1000

5 - 50

200 - 2000

1000 - 2000

20 000

500 - 1000

20 000

Widerstandsart

Kleinstdünnfilmwiderstände

Diskrete Dünnfilmwiderstände

(RN55E)

Abgeglichene Dünnfilmwiderstandsnetzwerke

Kohleschichtwiderstände

Tafel 1.1.4: Stabilität von Widerständen im Vergleich

6

1. Elektronische Bauelemente

(LQVWHOOEDUH:LGHUVWlQGH6SDQQXQJVWHLOHU

Veränderbare Widerstände werden als Dreh- oder Schiebewiderstände hergestellt. In der Praxis

werden Schiebewiderstände nur für Laboraufbauten eingesetzt.

^ Spannungsteilung :

U2

=

U1

^ Schleiferbelastung :

Imax =

^ Innenwiderstand

Rx

R

1 + (1 − x) X

RL

R

mit x = R x

max

(1.1.7)

Pz

R max

(1.1.8)

Ri ers = Rx (1 - x )

R max

U1

x

(1.1.9)

Rmax - R x

U2

R

L

U1

Rx

U2

RL

Bild 1.1.3: Spannungsteiler mit einstellbarem Widerstand

)RWRZLGHUVWlQGH

Fotowiderstände sind Halbleiter-Bauelemente ohne ausgeprägte Sperrschicht, d.h. sie bestehen aus

einem homogenen dotierten Halbleitermaterial (CdS, CdSe, PbS, Si). Dazu wird das HalbleiterMaterial als dünne Schicht im Inneren eines Glaskolbens aufgetragen und eingeschmolzen. Wegen

der homogenen Verteilung der HL-Elemente im Kristall ist der Widerstandswert in weiten Grenzen

sowohl von der angelegten Spannung als auch von ihrer Polarität unabhängig (gute Linearität).

Bei Beleuchtung erhöhen die auftreffenden Photonen die Beweglichkeit der Elektronen und der

Widerstand ändert sich von seinem 'XQNHOZHUW RD auf seinen +HOOZHUW RH um mehrere Dekaden.

Da die Elektronen den Kristall nicht verlassen (sogenannter innerer fotoelektrischer Effekt), haben

Fotowiderstände eine hohe spektrale Empfindlichkeit ( = 400 nm ... 1 200 nm).

Für den Widerstandswert gilt R x = R o E − c mit c = 0,5 ... 1,0.

^ Der Widerstandswert Rx ist abhängig von dem auf eine Beleuchtungsstärke von 1 lx

bezogenen Widerstand Ro , von der Beleuchtungsstärke E sowie einer Materialkonstanten c.

Fotowiderstände auf Cadmiumsulfid-Basis (CdS) haben ihre höchste Empfindlichkeit im Bereich

des sichtbaren Lichts ( O500 nm), ihr Dunkelwiderstand beträgt etwa R D O (10 6 ... 10 8 ) und der

Hellwiderstand liegt bei R H O 1 k .

^ Fotowiderstände sind träge Bauelemente, die Anstiegs- und Abfallzeiten liegen typisch im

Bereich von einigen 10 ms ... > 100 ms.

1. Elektronische Bauelemente

7

1LFKWOLQHDUH:LGHUVWlQGH

9DULVWRUHQ

Varistoren sind spannungsabhängige Halbleiter-Widerstände, deren Kennwerte wesentlich durch

die geometrischen Abmessungen (Formkonstante C) und den verwendeten Werkstoff (Konstante )

bestimmt werden. Die Eigenschaft, daß der differentielle Widerstand bei steigender Spannung

sinkt, wird in technischen Anwendungen zur Signalbegrenzung, Stabilisierung, zur niederohmigen

Signalteilung bzw. zum Überspannungsschutz genutzt (Bild 1.1.4).

^

Widerstand

R = C . I (−1)

(1.1.10)

^

Spannung

U = C.I (1.1.11)

^

Leistung

P = C . I (+1)

(1.1.12)

C - Formkonstante (Spannungsabfall bei I = 1 A)

- Materialkonstante (Zinkoxid ca. 0,05, Si-Carbid 0,15...0,25)

^ differentieller Widertstand

U

r

−1

r 0 = d U (I 0 ) = C . . I 0 , 0 = R0

dI

I

C = 270

C = 100

I

R

Uo

I

Io

U 1+ ∆U1

U2+ ∆ U2

U1+ ∆ U1

R

U2+ ∆ U2

niederohmige Signalteilung

Signalbegrenzung

typische Kennlinie

für f < 1 kHz

(1.1.13)

∆ U 2 => 0 für |U1| > U1min

∆ U2 => ∆ U1 für |U1| > U 1min

Bild 1.1.4: Kennlinie und Grundschaltungen für Varistoren

+HLOHLWHU17&:LGHUVWlQGH7KHUPLVWRUHQ

Heißleiter sind nichtlineare Halbleiter-Widerstände mit negativem Temperaturkoeffizienten (NTC).

Sie werden z. B. als Meßfühler, Anlaßheißleiter und zur Temperaturgangkompensation eingesetzt.

Die Eigenzeitkonstante liegt im Sekundenbereich.

Wird bei anliegender Spannung die Grenzleistung Pg überschritten, heizt sich der Thermistor

zunehmend selbst auf (signalabhängiger Widerstand).

−b

^ Widerstand

^ Eigenerwärmung

RT = R0 e

T = Rth P

^ Grenzleistung mit

vernachlässigbarer Eigenerwärmung

Pg = Ug . Ig

1 −1

T0 T

(1.1.14)

(1.1.15)

(1.1.16)

R0 - Bezugswiderstand bei T0 (meist 25°C), b - Energiekonstante, Herstellerangabe.

8

1. Elektronische Bauelemente

.RQGHQVDWRUHQ

Ein Kondensator ist ein Bauelement, das elektrische Ladungen aufnehmen und speichern kann.

Diese Eigenschaft heißt .DSD]LWlW des Kondensators. Die Ladungsspeicherung bewirkt eine

Energiespeicherung. Die elektrische Energie wird im elektrischen Feld gespeichert, welches sich im

Dielektrikum ausbildet.

^ Kondensatoren sind die wichtigsten energiespeichernden Bauelemente in der elektronischen

Schaltungstechnik. Die besseren elektrischen Eigenschaften und die wesentlich günstigere

technologische Fertigung führen zu einem klar bevorzugten Einsatz gegenüber Induktivitäten

(Spulen). Das gilt erst recht für die integrierte Schaltungstechnik.

Kondensatoren werden als Bauelemente gezielt in Schaltungen eingesetzt, sie können aber auch als

parasitäre Elemente auftreten. So zeigen z. B. pn-Übergänge in Halbleiterelementen und parallele

Leitungen kapazitive Erscheinungen. Sie machen sich z. B. in einer 9HU]|JHUXQJ von Schaltflanken

bzw. durch hEHUVSUHFKHQ auf benachbarte Leitungen störend bemerkbar.

Kondensatoren werden als Bauelemente in sehr unterschiedlichen Bauformen (Plattenkondensator,

Zylinderkondensator, ...) realisiert. Ihre Kapazitätswerte hängen in sehr starkem Maße vom

geometrischen Aufbau und den verwendeten Materialien für das Dielektrikum ab.

Beim Einsatz muß zwischen gepolten und ungepolten Kondensatoren unterschieden werden.

^ Bei ungepolten Kondensatoren sind die beiden Anschlüsse gleichwertig.

^ Gepolte Kondensatoren (z.B. Elektrolyt-Kondensatoren, kurz Elko) sind nur unter Beachtung

der Polarität der angeschalteten Spannung einsatzfähig. Anderenfalls kommt es zu einem

Abbau des Dielektrikums und damit zur Zerstörung des Kondensators.

Handelsübliche Kapazitätswerte sind entsprechend den E-Reihen gestuft (typisch E 6, E 12), die

Realisierung enger tolerierter Werte bereitet erhebliche technologische Probleme.

'HILQLWLRQVJOHLFKXQJHQ

d U C (t)

,

dt

Zeitbereich

i C (t) = C

Frequenzbereich

I C = L i C (t) = C

0

t

U C (t) = 1 i C (t) d t + U C (0) ,

C0

dU C − pt

e dt .

dt

(1.2.1)

(1.2.2)

Nach partieller Differentiation folgt in Operatorform IC (p) = C [ pUC (p) - UC (0) ]. Mit UC (0) ≡ 0

wird die komplexe Frequenz p = + j * zum +HDYLVLGH2SHUDWRU und es gilt einfacher

IC (p) = C . p . UC (p)

Z C (p) =

U C (p)

= 1.

I C (p)

p C

- Impedanz,

Y C (p) =

I C (p)

= 1 = p.C

Z C (p)

U C (p)

- Admittanz.

1. Elektronische Bauelemente

9

'LPHQVLRQLHUXQJVJOHLFKXQJHQ

Q

^ Kapazität, allgemein

[F = As

]

V

C= U

(1.2.4)

C = 0 r (n − 1) A

d

^ Plattenkondensator

(n - Anzahl der Platten, A - Fläche, d - Plattenabstand)

^ Zylinderkondensator

C = 2 0 r

l

ln r a − ln r i

(Rohrkondensator, Koaxialkabel)

ra - äußerer Radius

ri - innerer Radius

^ elektrische Feldkonstante

(Dielektrizitätskonstante)

.

0 = 8, 86 . 10 −12 A. s

V m

^ Dielektrizitätszahlen r

Vakuum

Luft

Glimmer

Hartpapier

^ gespeicherte Energie

W = C U C2

2

(1.2.5)

^ Temperaturkoeffizient

TK C = 1 . C

C T

(1.2.6)

1

1,0006

6 ... 8

5 ... 6

keramische Massen

NDK-Typen

10 ...

130

HDK-Typen 2000 ...10 000

In der industriellen Informationsverarbeitung bzw. Signalverarbeitung müssen die Kondensatoren

ein breites Frequenzspektrum (0 ... 100 MHz) verarbeiten. Es genügt deshalb meist nicht, die realen

Eigenschaften von Kondensatoren nur bei einer Frequenz zu beschreiben.

^ Insbesondere müssen auch sogenannte 5HOD[DWLRQHQ (dielektrische Nachwirkungen) beachtet

werden. Sie äußern sich in Form von Nach- und Umladeerscheinungen und bewirken ein

"Gedächtnis" des Kondensators. Die Nichtbeachtung kann in Präzisionsschaltungen (z.B.

S&H-Schaltungen bei der Analog-Digital-Wandlung) zu großen Fehlern führen.

5HLKHQXQG3DUDOOHOVFKDOWXQJYRQ.RQGHQVDWRUHQ

Bei der Zusammenschaltung von Kondensatoren ergeben sich die Kennwerte Gesamtkapazität,

Temperaturkoeffizient, Ladespannung und Ladung entsprechend der Ersatzschaltung grundsätzlich

aus den Kirchhoffschen Gleichungen. Nachfolgend sind die Ergebnisse für die Reihen- bzw.

Parallelschaltung von zwei Kondensatoren angegeben.

Reihenschaltung

Gesamtkapazität

Temperaturkoeffizient

C

.

C

Cges = C 1 + C2

1

2

TKges =

C 1 TK 2 + C 2 TK 1

C1 + C2

Parallelschaltung

Cges = C1 + C2

TKges =

C 1 TK 1 + C 2 TK 2

C1 + C2

Ladespannung

Uges = UC1 + UC2

Uges = UC1 = UC2

Ladung

Qges = QC1 = QC2

Qges = QC1 + QC2

10

1. Elektronische Bauelemente

,QGXNWLYLWlWHQhEHUWUDJHU5HODLV

Induktivitäten werden selten zur Signalformung bzw. -übertragung verwendet. In der industriellen

Elektronik sind sie überwiegend in Transformatoren (Übertrager) und Relais eingesetzt. Die

Möglichkeit der potentialfreien bzw. galvanisch getrennten Signalübertragung mit Übertragern wird

zunehmend durch optoelektronische Kopplung realisiert.

^ Parasitär tritt die Induktivität jedoch in Form der /HLWXQJVLQGXNWLYLWlW immer auf und muß als

solche ggf. entsprechend beachtet werden.

'HILQLWLRQVJOHLFKXQJHQ

d i L (t)

dt

^ Zeitbereich

U L (t) = L

^ Frequenzbereich

UL (p) = L . [ p. IL(p) - iL(0) ]

Mit iL (p) ≡ 0 gilt

(1.3.1)

(1.3.2)

UL (p) = L . p. IL(p),

Z L (p) =

U L (p)

= p.L

I L (p)

- Impedanz,

Y L (p) =

1 = 1

Z L (p) p . L

- Admittanz.

/HLWXQJVLQGXNWLYLWlW

Die wichtigste Eigenschaft der Leitungsinduktivität ist der /DXI]HLWHIIHNW und die damit verbundene

5HIOHNWLRQeinerWelle bei Fehlanpassung. In der Folge können Signalverzerrungen auf der Leitung

entstehen, die schaltungstechnisch nur schlecht zu korrigieren sind. Sie müssen deshalb mit Hilfe

der /HLWXQJVDQSDVVXQJ weitgehend vermieden werden. Als allgemeine Anpaßbedingung gilt:

^ Der Abschlußwiderstand Za (p) der Leitung muß gleich ihrem komplexen Wellenwiderstand

ZW (p) sein (vgl. Abschnitt 11).

5HODLV

Ein Relais ist meist ein elektromechanisches Bauelement zur Ausführung einer 6FKDOWIXQNWLRQ. Die

Schaltfunktion wird durch Öffner, Schließer und/oder Umschalter realisiert. Die Steuergröße ist

eine elektrische Leistung, die unterschiedlich umgesetzt wird. Abhängig von dieser Umsetzung

werden elektronische, elektromagnetische, thermische, elektrostatische und elektrodynamische

Relais unterschieden. Weit verbreitet ist das elektromagnetische Relais, bei dem ein Elektromagnet

bei Stromerregung einen Anker anzieht, der seinerseits die Kontakte betätigt.

Wichtige statische Kenngrößen von Relais sind Anzugsstrom IA , Haltestrom IH , Abfallstrom IR und

Fehlstrom IF . Sie müssen durch geeignete Ansteuerschaltungen erzeugt werden. Dazu kommen die

dynamischen Kennwerte in Form der Schaltzeiten und Verzögerungszeiten. Alle Kennwerte sind

stark von technologischen Parametern und dem Aufbau bestimmt.

Beim Einsatz von Relais in elektronischen Schaltungen ist neben der Einhaltung seiner Kennwerte

(Anzugsstrom, Haltestrom, Fehlstrom, ...) das Auftreten einer großen $EVFKDOWVSDQQXQJ zu

beachten, die ggf. eine Begrenzerschaltung erforderlich macht. Meist wird dazu das Prinzip der

)UHLODXIGLRGH angewendet (vgl. Abschnitt 2).

1. Elektronische Bauelemente

11

+DOEOHLWHUGLRGHQ

Halbleiter-Dioden entstehen technologisch durch Diffusion von p- und n-dotierten Bereichen

(pn-Übergang) oder durch einen Metall-Halbleiterübergang (SB, Schottky-Barriere).

Ausgangsmaterial ist heute meist Silicium, für sehr schnelle Dioden wird zunehmend dotiertes

GaAs verwendet (ca. 6 x höhere Ladungsträgerbeweglichkeit als bei Silicium).

8QLYHUVDOXQG6FKDOWGLRGHQ

6WDWLVFKHV9HUKDOWHQ

Die I-U-Kennlinie einer Halbleiter-Diode (Bild 1.4.1) läßt sich in guter Näherung durch einen

exponentiellen Verlauf beschreiben:

UD

ID = IS ( e U T − 1).

(1.4.1)

Dabei bedeuten:

.

Temperaturspannung UT = kqT O 26 mV (bei Raumtemperatur),

Sättigungsstrom

I S = (0,1 ...10) nA - technologieabhängiger Kennwert.

ID

U

F

IF

IF

U

B

A K

20 mA

R

A - Anode

K - Katode

UR

1V

5V

U BR

U

100 µA

UD

S

UF

IR

Bild 1.4.1: I-U-Kennlinie einer Halbleiter-Diode

,GHDOLVLHUWH'LRGH

Zur Vereinfachung der Schaltungsberechnung wird der exponentielle Verlauf der I-U-Kennlinie

realer Halbleiter-Dioden meist durch eine idealisierte .QLFNNHQQOLQLH beschrieben (Bild 1.4.2). Es

sind unterschiedliche Approximationen und Ersatzschaltungen gebräuchlich. Man spricht dann

auch von einer idealisierten Diode. Das Verhalten wird oft vereinfacht mit Gl. (1.4.2) beschrieben

0 für U D < U S

ID =

.

IF für U D P U S

(1.4.2)

^ Praktisch fließt ein nennenswerter Strom ID = IF erst für eine Diodenspannung UD P US .

12

1. Elektronische Bauelemente

UD

ID

K

A

ID

RF

RF = 0

ID

A

RF

US

UZ

UZ

K

US

RS

+ -

UD

RS

US

UD

RZ = 0

RZ

RS

∞

Statische Ersatzschaltung

gebräuchliche Approximationen der Kennlinie

Bild 1.4.2: Statische Ersatzschaltung und idealisierte Diodenkennlinien

Da der Durchlaßwiderstand RF bei leitender Diode sehr klein ist (RF = 1 Ω ... 20 Ω bei Universalund Schaltdioden, RZ = 7 Ω ... 20 Ω bei Z-Dioden) wird praktisch vereinfacht mit konstanter

Flußspannung UF = US = konst. gerechnet. Das ist für US >> ID . RF meist hinreichend erfüllt.

^ Beim praktischen Einsatz muß immer ein Begrenzungswiderstand R für den Diodenstrom ID

im Stromkreis vorgesehen werden, damit die maximal zulässige Verlustleistung Ptot der

P

Diode nicht überschritten wird (I F > Utot ).

F

Bild 1.4.3 zeigt die Zeitverläufe in einer einfachen Schaltung mit idealisierter Diode. Durch die

9HQWLOZLUNXQJ der Diode werden nur die positiven Anteile der Spannung U1 (t) übertragen, während

bei negativer Spannung die Diode gesperrt ist (ID = 0). Bei umgekehrter Polung der Diode werden

entsprechend nur die negativen Teile der Spannung U1 (t) übertragen, während die Diode nun für

positive Spannungen U1 (t) gesperrt ist.

^ Diese Eigenschaft der Halbleiter-Diode wird u.a. in *OHLFKULFKWHUVFKDOWXQJHQ und in

ORJLVFKHQ6FKDOWXQJHQ genutzt.

UF

U1

U1

IF

RL

U1max

t

UA

UA

U 1max- U F = I F RL

t

0

für U D < U S

ID =

.

U 1 − U S für U D P U S

RL

Bild 1.4.3: Gleichrichterwirkung einer idealisierten Diode

1. Elektronische Bauelemente

13

6WDWLVFKH.HQQZHUWH

Für HL-Dioden werden wie bei allen Halbleiter-Bauelementen eine ganze Anzahl von Kenn- und

Grenzwerten verwendet, die wichtigsten sind nachfolgend im Überblick angegeben.

UD

UF

US

UR

UBR

ID

IF

IR

IFSM

Diodenspannung, allgemein,

Flußspannung bei leitender Diode,

Schleusenspannung,

Sperrspannung,

Durchbruchspannung (wird als Kennwert nicht angegeben),

Diodenstrom, allgemein,

Flußstrom bei leitender Diode,

Sperrstrom,

maximaler Stoßstrom.

Wegen der nichtlinearen Kennlinie sind die Dioden-Kenngrößen DUEHLWVSXQNWDEKlQJLJ. Bei vielen

Anwendungen, insbesondere beim Einsatz in digitalen Schaltungen, kann aber vereinfacht mit dem

Modell einer idealisierten Diode gearbeitet werden.

Typische Wertebereiche für die Kennwerte sind:

Flußwiderstand

Sperrwiderstand

RF = RON = (1 ... 20) Ω

RS = ROFF = (0,1 ..10) M Ω

Schleusenspannung

US = (0,6 ... 0,8 ) V

US = (0,3 ... 0,45) V

für PN-Typen

für SB-Typen

Durchbruchspannung

UBR = -5 V ... -180 V für Universal- und Schaltdioden

(angegeben wird meist nur ein Wert UR max für den sicheren Betrieb der Diode)

UZ = (5 ... 24) V

zulässiger Temperaturbereich

für Z-Dioden

- 55 °C < T < 150 °C (typisch)

^ Sperrwiderstand RS, Schleusenspannung US und Durchbruchspannung UBr (UZ bei Z-Dioden)

sind temperaturabhängige Kennwerte. Das wird durch ihren Temperaturkoeffizienten TK

ausgedrückt

TK (US ) = (2 ... 2,2) mV/K,

100%

I S (T 0 )

TK ( I S )

.

= (8 ... 14)% G I S (T ) O (2 ... 3) .

IS

8K

^ Beim Einsatz von Schaltdioden in logischen Schaltungen reicht für die Analyse meist die

Berücksichtigung der Schleusenspannung US und/oder der Durchbruchspannung UBr (UZ )

aus.

^ Bei 9HUNQSIXQJVVFKDOWXQJHQ mit einer großen Anzahl von Dioden (viele Eingänge) muß

ggf. der wirksame Reststrom infolge dieser Temperaturabhängigkeit beachtet werden.

14

1. Elektronische Bauelemente

'\QDPLVFKH.HQQZHUWH

Das Impulsverhalten realer Dioden wird wie bei allen Halbleiter-Bauelementen sehr stark vom

technologischen Aufbau und der äußeren Schaltung (Schaltspannung, -ströme, äußere Widerstände)

bestimmt.

^ Die wichtigsten dynamischen Kenngrößen von HL-Dioden sind die 'LIIXVLRQVNDSD]LWlW CD

und die 6SHUUVFKLFKNDSD]LWlW CS (vgl. Bild 1.4.4).

^ Weitere Einflußfaktoren sind Gehäusekapazität, Leitungsinduktivität und Bahnwiderstände.

Die 6SHUUVFKLFKWNDSD]LWlW CS ist spannungsabhängig und wirkt sowohl bei leitender als auch bei

gesperrter Diode. Die 'LIIXVLRQVNDSD]LWlW CD ist nur bei leitender Diode wirksam. Sie repräsentiert

im wesentlichen die Änderung der Minoritätsträgerladung bei Änderung der Flußspannung UF

CD =

Q Min

.

UF

(1.4.3)

Bei leitender Diode wird die wirksame Kapazität (CD + CS ) und die davon abhängige Zeitkonstante

durch den parallelliegendenen niederohmigen Flußwiderstand RF sehr stark in ihrer Auswirkung

reduziert.

UF

U1

IF

U

t

U(t)

RL

U2

IF

ID

tr

CD

UF

RF

IF

UD

RS

RL

U(t)

t

IS

IR

tS

U =U

1 FS

US

tf

CS

t

U 2= U

R

tE

Bild 1.4.4: Dynamische Ersatzschaltung und Impulsverhalten von Halbleiter-Dioden

(LQVFKDOWYRUJDQJ

Beim Einschalten muß sich zuerst eine 5DXPODGXQJV]RQH am pn-Übergang aufbauen, dabei ist

zunächst noch der Sperrwiderstand RS der Diode wirksam. Kurzzeitig entsteht eine hohe DiodenR

Flußspannung U FS = R +SR U 1 O U 1 . Der ansteigende Strom ID erzeugt die Raumladung und die

S

L

Diodenspannung sinkt auf den stationären Wert US ab.

^ Die Anstiegszeit tr beim Einschalten ist klein und kann gegenüber anderen Schaltzeiten meist

vernachlässigt werden.

1. Elektronische Bauelemente

15

$XVVFKDOWYRUJDQJ

Beim Ausschalten fließt infolge der hohen Anzahl von Ladungsträgern im %DKQJHELHW zunächst ein

relativ großer $XVUlXPVWURP IRS (Speicherzeit tS). Die Diode bleibt leitend (es fließt ein Strom),

obwohl das Steuersignal bereits umgeschaltet hat. Erst wenn die innere Sperrschichtspannung auf

Werte USS < 0 abgesunken ist, wird die Sperrschichtkapazität CS über RL spürbar entladen. Beim

Abschalten tritt so neben der Abfallzeit tf infolge der Speicherwirkung der parasitären Kapazitäten,

insbesondere der Sperrschichtkapazität CS , eine zusätzliche6SHUUYHU]|JHUXQJ auf.

I

^ Für die Speicherzeit tS gilt t S = $ 0 ln ( 1 + I F ) , typisch ( ns ... s ) .

R

^ Für die Abfallzeit tf gilt näherungsweise t f O 2, 2 . R L . C S .

^ Meist geben die Hersteller als dynamischen Kennwert eine sogenannte Erholzeit tE = tS + tf

anstelle einer Sperrverzögerungszeit an.

Diese Aussagen über das dynamische Verhalten gelten prinzipiell für alle Halbleiter-Bauelemente

mit pn-Übergängen, insbesondere auch für Bipolartransistoren (vgl. Abschnitt 1.5.3).

='LRGHQ

Z-Dioden werden in der industriellen Elektronik vorwiegend zur 5HIHUHQ]VSDQQXQJVHU]HXJXQJ und

in 6WDELOLVLHUXQJVVFKDOWXQJHQ angewendet.

^ Z-Dioden sind Halbleiter-Dioden mit einem ausgeprägtem Durchbruchverhalten (Avalanche-,

Lawineneffekt), wenn die Diode in 6SHUULFKWXQJ betrieben wird.

Für die VWDWLVFKHQ Kennwerte von Z-Dioden gelten im Prinzip die gleichen Aussagen wie bei den

Universaldioden. Insbesondere muß im Betrieb stets ein minimaler Z-Strom IZ min gewährleistet

werden, damit ein Stabilisierungseffekt erreicht wird (steiler Kennlinienbereich).

Die G\QDPLVFKHQ Kennwerte von Z-Dioden sind wesentlich schlechter als die von Universal- und

Schaltdioden. Sie werden deshalb im Schalterbetrieb nur in langsamen logischen Schaltungen

(LSL) als sogenannte +XEGLRGHQ eingesetzt (Erhöhung der Umschaltpegel und damit Vergrößerung

des statischen Störabstandes, vgl. auch Abschnitt 4).

.HQQOLQLHXQG.HQQZHUWH

Die I-U-Kennlinie einer Z-Diode ist in Bild 1.4.5 gezeigt. Zur vereinfachten Berechnung wird auch

bei Z-Dioden von der Linearisierung der Kennlinie Gebrauch gemacht.

Zur Schaltungsdimensionierung werden typisch folgende Kennwerte von Z-Dioden verwendet:

UZ

U

rZ = I Z

Z

Ptot

P

IZmax = Utot

Z

IZmin O 0,1 . IZmax

U

Z

TK(UZ ) = U . T

Z

- Z-Spannung (Nennwert)

- Z-Widerstand

- zulässige Verlustleistung

- max. zulässiger Z-Strom

- minimaler Z-Strom (Durchbruchbereich)

- Temperaturkoeffizient der Z-Spannung

16

1. Elektronische Bauelemente

I

ID

D

5V

UZ

UZ

UD

RS

∞

US

UD

I Z min

RZ

RZ = 0

P tot

a) real

b) idealisiert

Bild 1.4.5: I-U-Kennlinie einer Z-Diode

$QZHQGXQJVVFKDOWXQJHQPLW='LRGH

Die Grundstruktur einer Stabilisierungsschaltung mit Z-Diode zeigt Bild 1.4.6 a); sie eignet sich

u.a. zur Erzeugung einer 5HIHUHQ]VSDQQXQJ bei kleinen und konstanten Lastströmen.

Bild 1.4.6 b) zeigt eine Schaltung zur 3HJHOYHUVFKLHEXQJ mit Z-Diode; bei leitender Z-Diode gilt

hier UA = UI - UZ .

Für die Bemessung der Stabilisierungsschaltung lassen sich allgemeine Forderungen ableiten:

Eingangsspannung

UI ± UI P (1,8...2)UZ ,

Vorwiderstand

RV min < RV < RV max

mit

RV min =

(1.4.4)

U I + U I − U Z

U − U − U

, RV max = II + II Z ,

I L min + I Z max

L max

Z min

I Z max >

P tot

,

UZ

U

U

R

U

Stabilisierungsfaktor S = U I . UZ = 1 + RV . UZ .

I

Z

I

Z

Rv

UI

IL

I

Z

U

Z

IZ

RL

a) Stabilisierungsschaltung

Bild 1.4.6: Grundschaltungen mit Z-Diode

(1.4.5)

UZ

R

UI

UA

b) Pegelverschiebung

1. Elektronische Bauelemente

17

%LSRODUWUDQVLVWRUHQ

Bipolartransistoren sind Halbleiterbauelemente mit 2 Sperrschichten, deren Zonenfolge den Typ

festlegt (npn, pnp). Die 3 Zonen heißen (PLWWHU (E), %DVLV (B) und .ROOHNWRU (C). Sie sind mit

Anschlüssen versehen und somit dem Anwender zugänglich (Bild 1.5.1, Schaltsymbol).

^ Bipolartransistoren benötigen für ihre Funktion Ladungsträger beider Polaritäten (Majoritätsund Minoritätsträger), als Halbleitermaterial dient heute meist Silicium. Sie finden eine breite

technische Anwendung und werden allgemein einfach Transistoren genannt.

Transistoren werden oft auch als "aktive" Bauelemente bezeichnet, obwohl sie eigentlich nur

steuerbare passive Elemente sind. Ein sogenanntes "aktives" Verhalten läßt sich grundsätzlich nur

mit Hilfe einer Schaltung erzeugen, die an mindestens eine oder mehrere Energiequellen, typisch

Gleichspannungen, angeschlossen wird (Arbeitspunkteinstellung).

6WDWLVFKH(LJHQVFKDIWHQ(UVDW]VFKDOWXQJHQXQG.HQQZHUWH

Die Strom-Spannungsrelationen (statische Eigenschaften und Kennwerte) am Transistor sind stark

nichtlinear und werden anschaulich durch Kennlinienfelder (Bild 1.5.1) und/oder Ersatzschaltungen

(vgl. Bilder 1.5.2, 1.5.3) beschrieben. Aus den Kennliniengleichungen ist u.a. auch die starke

Temperaturabhängigkeit (UT -Temperaturspannung) der Transistorkenngrößen erkennbar:

^ IC und IB steigen, UBE sinkt mit steigender Temperatur.

Typ

Symbol

Eingangskennlinie

C

I

npn

B

B

UCE

UBE

E IE

US

C

UBE

-I

- IB

-I

C

- IB

pnp

IC

IB

IC

Ausgangskennlinienfeld

B

- UBE

- UCE

E - IE

- US

Bild 1.5.1: Kennlinien von Bipolartransistoren

- UBE

C

100

80

IB

40

20

10 µA

1

UCE

100

80

- IB

40

20

10 µA

1

- U CE

18

1. Elektronische Bauelemente

Im Ausgangskennlinienfeld IC = f {UCE ; IB } können mehrere Bereiche unterschieden werden, von

denen aber nur drei Bereiche technisch genutzt werden (Tafel 1.5.1). Dabei dürfen die zulässigen

Grenzwerte (UBE max , UCB max , UCE max, IC max, IB max , Ptot , ) nicht überschritten werden.

Emitterdiode

Kollektordiode

Arbeitsbereich

Anwendung

1

gesperrt

gesperrt

Sperrbereich

Schalter (OFF)

2

leitend

gesperrt

aktiv normal

Verstärker

3

gesperrt

leitend

aktiv invers

-

4

leitend

leitend

Sättigungsbereich,

Übersteuerung

Schalter (ON)

Tafel 1.5.1: Arbeitsbereiche von Transistoren

(UVDW]VFKDOWXQJ

Das statische Großsignalverhalten von Bipolartransistoren wird häufig mit Hilfe des Ebers-MollErsatzschaltbildes nach Bild 1.5.2 beschrieben.

A I I’C

IE

AN I’E

I’E

B’

E

UEB

UB’E

IB

B

UB’C

r BB’

I’C

für pnp-Typen sind

- die Dioden umzupolen

- alle Ströme und Spannungen

in ihrer Richtung umzukehren

IC

C

UCB

B

Bild 1.5.2: Statisches Ersatzschaltbild für npn-Bipolartransistoren nach EBERS-MOLL

Die Kennliniengleichungen für den inneren Transistor ergeben sich nach dem Knotensatz zu

IC = AN I’E - I’C , IE = I'E - AI I'C

IB = IE - IC ,

(1.5.1)

mit den Diodenströmen

U

U

I'C = ICS (exp UB C − 1) und I'E = IES (exp UB E − 1).

T

T

^ ICS , IES sind Sättigungsströme, deren Werte technologieabhängig sind (vgl. auch Diode).

Es folgt:

−U

IC = AN IE - I'C (1-AN AI ) = AN IE - ICB0 (exp UCB − 1)

T

mit

ICB0 = ICS (1-AN AI ) , Kollektorreststrom für IE = 0.

(1.5.2)

1. Elektronische Bauelemente

A

19

B

N

N

Wegen B N = 1 − A

bzw. A N =

folgt für den Kollektorstrom IC

1 + BN

N

−U

IC = BN IB - ICB0 (1+BN ) ( exp UCB − 1) .

T

(1.5.3)

^ Für UCB’ >> UT folgt daraus für den Kollektorstrom einfacher IC = BN . IB + (1+BN ) . ICBO .

^ An der hEHUVWHXHUXQJVJUHQ]H (Index ü für die Kennwerte) gilt per Definition UCB’ := 0 bzw.

UCEü = UBEü und für IC folgt der einfache Ausdruck IC = BN . IB . Wegen der Steilheit der

Kennlinie der BE-Diode gilt auch UBEü O UBEx .

Zur näherungsweisen Berechnung des statischen Verhaltens von Transistoren im DNWLYHQ Bereich

(gesperrte Kollektor-Basis-Diode, UCB’ >> UT bei npn-Typen) genügen demnnach meist die drei

Kenngrößen IB (bzw. UBE ), BN und ICBO . Entsprechend vereinfacht sich auch die Ersatzschaltung für

diesen Arbeitsbereich (Bild 1.5.3).

C

C

IC

IB

r

IC

BB’

B

B

I

UBE

E

IB

+ U

S

IE

UBE

E

für Silicium:

E

US O (0,6...0,8) V,

IB rBB’ O (0,1 ... 5) mV

Bild 1.5.3: Vereinfachte Ersatzschaltungen für npn-Transistoren bei gesperrter Kollektordiode

6WURPYHUVWlUNXQJVJUXSSHQ

Die Stromverstärkung BN ist wie alle Transistorkennwerte stark exemplarabhängig und wird durch

eine grobe Sortierung nach 6WURPYHUVWlUNXQJVJUXSSHQ gekennzeichnet (Tafel 1.5.2).

^ Innerhalb der Gruppen muß exemplarabhängig mit großen Schwankungen im realisierten

Wert der Stromverstärkung B gerechnet werden.

Stromverstärkungsgruppe

a

b

c

d

e

f

Minimal-Wert Bmin

18

28

56

112

224

450

Maximal-Wert Bmax

35

71

140

280

560

1 120

Tafel 1.5.2: Stromverstärkungsgruppen von Bipolartransistoren

20

1. Elektronische Bauelemente

%LSRODUWUDQVLVWRULQ$QDORJVFKDOWXQJHQ9HUVWlUNHU

Eine analoge Transistorschaltung muß stets so dimensioniert werden, daß RKQH Signalaussteuerung

die Ruhegleichströme ICA und IBA fließen und die Gleichspannungen UCEA und UBEA am Transistor

anliegen. Man spricht auch von $UEHLWVSXQNWHLQVWHOOXQJ.

Das diesen Gleichgrößen überlagerte Wechsel-Signal bewirkt dann eine Aussteuerung um diesen

Arbeitspunkt. Bei OLQHDUHQ Schaltungen muß eine Aussteuerung des Transistors in den Sättigungsund in den Sperrbereich vermieden werden.

Zur Stabilisierung des Arbeitspunktes gegen Parameteränderungen (Temperatur, Betriebsspannung,

Exemplarstreuungen, ...) werden bevorzugt Schaltungen mit *HJHQNRSSOXQJHQ verwendet (RE in

Bild 1.5.4 - Stromgegenkopplung).

^ Zur gleichspannungsunabhängigen Anschaltung des Nutzsignals wird oft eine kapazitive

Einkopplung über Kondensatoren C gewählt (Wechselspannungsverstärkung). Damit ist bei

mehrstufigen Verstärkern die Arbeitspunkteinstellung der einzelnen Stufen unabhängig voneinander. Es können aber nur Wechselsignale übertragen werden.

^ Bei Gleichspannungsverstärkern dagegen beeinflussen sich die Arbeitspunktparameter der

Einzelstufen gegenseitig, die Bemessung der Schaltung ist i.a. schwieriger. Dafür können

sowohl Gleich- als auch Wechselsignale übertragen bzw. verstärkt werden.

+U CC

IC

RC

R1

C

e

RC

IB

C

a

U

CE

Iq

R

E

b)

R2

C

a

e

UCE

UBE

a)

R1

C

IB

+UCC

IC

RE

U

RE

Bild 1.5.4: Lineare Schaltungen zur Arbeitspunkteinstellung und -stabilisierung

a) Konstantstromeinspeisung über Vorwiderstand, b) Basisspannungsteiler

Allgemein gelten folgende Gleichungen für die Kenngrößen in den angegebenen Schaltungen

IC =

RC =

U CC − U CE − U RE

(Arbeitsgerade)

RC

U CC − U CEA − U REA

,

I CA

R1 =

U CC − U BEA − U REA

,

I BA + I q

(1.5.4)

R2 =

U BEA + U REA

Iq

(1.5.5)

Typische Werte sind: Iq = (1...10) . IBA, UREA > 1 V ( O 0,1. UCC ).

^ Die grafische Darstellung von Gl. (1.5.4) im Ausgangskennlinienfeld wird $UEHLWVJHUDGH

genannt. Der Arbeitspunkt ergibt sich dabei als Schnittpunkt dieser Arbeitsgeraden mit der

Ausgangskennlinie für den entsprechenden Basisgleichstrom IBA (Bild 1.5.5).

1. Elektronische Bauelemente

I

UCB = 0

C

21

I Bx

U

I Bü

I Cx

RC

I Cü

IB

AP

I

CA

I

B

P Cmax

Arbeitsgerade

I

I BA

CC

U

I

C

BE

U CE

I By

Cy

U

CEx

UCEü

UCEA

UCEy UCC

UCE

Bild 1.5.5: Arbeitspunktfestlegung im Ausgangskennlinienfeld

$UEHLWVSXQNWHLQVWHOOXQJXQGVWDELOLVLHUXQJ

Das Klemmenverhalten des Transistors in (PLWWHUVFKDOWXQJ (vgl. Bilder 1.5.4, 1.5.5) wird durch die

Ströme IB , IC und die Spannungen UBE , UCE beschrieben. Der Arbeitspunkt AP eines Transistors ist

durch die *OHLFKZHUWH dieser vier Größen festgelegt und liegt normalerweise im DNWLY QRUPDOHQ

Betriebsbereich (vgl. Tafel 1.5.1). Nur eine Größe (oft IC ) kann frei gewählt werden, die anderen

drei Werte sind dann über das Eingangs- und das Ausgangskennlinienfeld bzw. die entsprechenden

Gleichungen miteinander sowie über die Arbeitsgerade (Arbeitsgeradengleichung) mit der äußeren

Schaltung des Transistors verknüpft. Es gelten folgende allgemeine Beziehungen:

IB = f1 {UBE , UCE }

- Eingangskennlinienfeld,

IC = f2 {UCE , IB }

- Ausgangskennlinienfeld,

IC = f3 {UCE , RC }

- I-U-Kennlinie der äußeren Schaltung (Last).

(1.5.6)

Die Werte der Transistorgrößen, also auch die Arbeitspunktgrößen, ergeben sich als Schnittpunkt

der Ausgangskennlinie für den aktuellen Wert des Basisstromes IB mit der Arbeitsgeraden, da der

Kollektorstrom IC stets die beiden funktionellen Abhängigkeiten f2 und f3 gleichzeitig erfüllen muß

IC = f2 {UCE , IB } = f3 {UCE , RC }.

^ Der Arbeitspunkt einer Schaltung muß durch geeignete und entsprechend dimensionierte

Teilschaltungen realisiert und gegen Parameteränderungen stabilisiert werden.

Das 6WDELOLVLHUXQJVSULQ]LS läßt sich anschaulich im Ausgangskennlinienfeld erklären. Dazu werden

die Ausgangskennlinienfelder von zwei Transistoren mit unterschiedlicher Stromverstärkung B bei

gleicher Außenbeschaltung (Arbeitsgerade) verglichen (Bild 1.5.6). Grundsätzlich ergeben sich die

gleichen Aussagen für HLQ Exemplar eines Transistors bei unterschiedlicher Sperrschichttemperatur.

22

1. Elektronische Bauelemente

Ein Vergleich der beiden Darstellungen ergibt:

Wird IBA konstant gehalten, so ändert sich der AP (ICA , UCEA) im AKF erheblich, ggf. bis in den

Übersteuerungsbereich oder in den Sperrbereich.

Wird dagegen ICA konstant gehalten, so bleibt auch der AP im AKF weitgehend konstant. Nur der

Basisgleichstrom IBA ändert sich jetzt. Diese Änderungen sind allerdings um den Wert des

Stromverstärkungsfaktors B kleiner als bei Änderungen des Kollektorstromes. Gleichzeitig wird

somit eine thermische Überlastung des Transistors bei sehr kleinen Lasten vermieden.

^ Eine AP-Stabilisierung ist dann am wirksamsten, wenn dadurch der Kollektorgleichstrom ICA

im Arbeitspunkt konstant gehalten wird.

IC

IC

I CA2

140 µA

AP 1

I CA

I BA

IB

100 µA

140 µA

I BA

AP2

AP1

I CA1

100 µA

I

60 µA

B

20 µA

60 µA

20 µA

UCEA

UCC

UCE

a) Transistor mit Stromverstärkung B1

UCEA2 U

CEA1

UCC

UCE

b) Transistor mit erhöhter

Stromverstärkung B 2 > B 1

Bild 1.5.6: Zum Prinzip der AP-Stabilisierung in Transistorschaltungen

'ULIWYHUKDOWHQ

Außer den exemplarabhängigen Streuungen der Parameter kommt es auch zu zeit- und temperaturabhängigen Abweichungen der Kennwerte, was ebenfalls eine Verschiebung des Arbeitspunktes

bewirkt. Ist für eine Schaltung z.B. die Abhängigkeit IC = IC {IB, B, ICB0 } bekannt, so kann eine

kleine Änderung I C O dI C des Kollektorstromes über das totale Differential bestimmt werden:

I C O

I

I C

I C

U BE + C B +

I .

U BE

B

I CB0 CB0

(1.5.7)

^ Die typisch langsamen Änderungen U BE , B, I CB0 nennt man 'ULIWJU|HQ der Kennwerte.

Für die Temperaturdrift der BE-Spannung eines npn-Bipolartransistors wird z.B. angegeben:

U BE = − (2, 2 ... 2, 5) mV . T (vgl. auch Diodenkennwerte).

K

(1.5.8)

^ Das Ziel jeder AP-Stabilisierung besteht darin, die Auswirkungen der Driftgrößen auf den

Arbeitspunkt möglichst gering zu halten, z.B. die Driftverstärkung einer Verstärkerstufe im

Vergleich zur Signalverstärkung VDrift << VU .

1. Elektronische Bauelemente

23

Ein großer Unterschied im Einfluß der Driftgrößen auf den AP und letztlich auf die Ausgangsgröße

einer Schaltung besteht zwischen gleich- und wechselspannungsgekoppelten Schaltungen.

In ZHFKVHOVSDQQXQJVJHNRSSHOWHQ Schaltungen werden sehr langsame Änderungen typisch nicht

zwischen den einzelnen Stufen übertragen, solange die Signalfrequenz hoch genug ist (außerhalb

des Frequenzbereiches der Driftgrößen liegt) und die .RSSHONDSD]LWlWHQ entsprechend bemessen

sind. So kann die Forderung nach einer geringen Driftverstärkung meist relativ gut erfüllt werden.

In JOHLFKVSDQQXQJVJHNRSSHOWHQ Schaltungen dagegen werden die Driftgrößen mit der gleichen

Verstärkung übertragen wie das Nutzsignal.

6FKDOWXQJHQ]XU$36WDELOLVLHUXQJ

Schaltungstechnisch werden bevorzugt folgende Methoden zur AP-Stabilisierung angewendet

^

^

^

^

Gegenkopplung in linearen Schaltungen (Bilder 1.5.4, 1.5.7),

Einspeisung eines konstanten Emitterstromes (Konstantstromquelle),

Differenzverstärkerprinzip,

nichtlineare Temperatur-Kompensationsschaltungen mit Dioden, Transistoren, ...(Bild 1.5.8).

/LQHDUH6FKDOWXQJHQ]XU$36WDELOLVLHUXQJ

UCC

RB

RC

IB

IC

UBE

UCC

R1

RC

Iq

a) konstanter Basisstrom

R2

R1

A1

IB

UCE

UCC

RE

A2

b) Gleichstromgegenkopplung

IB

RC

IC

U

BE

UCE

c) Gleichspannungsgegenkopplung

Bild 1.5.7: Grundschaltungen zur AP-Einstellung und -stabilisierung

$3(LQVWHOOXQJGXUFKNRQVWDQWHQ%DVLVVWURP (Bild 1.5.7 a)

Wegen der starken Abhängigkeit des Kollektorstromes I C O B . I B von den Schwankungen der

Stromverstärkung B wird diese einfache Form der AP-Einstellung nur selten verwendet. Weiter gilt

IB =

U

U CC − U BE

O CC

RB

RB

für U CC >> U BE .

(1.5.9)

$3(LQVWHOOXQJXQGVWDELOLVLHUXQJGXUFK*OHLFKVWURPJHJHQNRSSOXQJ (Bild 1.5.7 b)

Das Basispotential UB = UBE + URE wird über den Spannungsteiler R1, R2 nahezu konstant gehalten,

solange der Querstrom Iq = (2 ...10) . IB groß gegenüber dem Basisstrom bleibt. Steigt nun IC wegen

einer Parameteränderung, so vergrößert sich auch der Spannungsabfall URE = IE . RE . In der Folge

davon wird UBE und so auch der Basisstrom IB verringert (Eingangskennlinie) und so der Änderung

des Kollektorstromes entgegengewirkt. Dieses Prinzip der 6WURPJHJHQNRSSOXQJ wird sehr oft zur

AP-Stabilisierung angewendet.

24

1. Elektronische Bauelemente

In der angegebenen Schaltung gilt bei ICB0 = 0

I CA =

U CC − U CEA

RE

.

− I BA

RC + RE

RC + RE

(1.5.10)

Nachteilig an dieser Schaltung gegenüber der einfachen Emitterschaltung in Bild 1.5.7 a) sind der

zusätzliche Spannungsverlust über RE (Aussteuerung, Verlustleistung, kleinere Signalverstärkung)

und ggf. der vergleichsweise große Querstrom Iq .

Wird Klemme A2 (meist bei RC = 0) als Ausgang der Schaltung in Bild 1.5.7 b) gewählt, so nennt

man die Schaltung wegen UA2 = Ue - UBE (PLWWHUIROJHU. Sie hat einen großen Eingangswiderstand,

r

einen kleinen Ausgangswiderstand [R ein O r BE + (1 + )R E , R aus O BE || RE ] und überträgt das Nutzsignal mit einer Spannungsverstärkung VU O 1 (Trennverstärker, Impedanzwandler).

$3(LQVWHOOXQJXQGVWDELOLVLHUXQJGXUFK*OHLFKVSDQQXQJVJHJHQNRSSOXQJ (Bild 1.5.7 c)

Bei steigendem IC sinkt zunächst UCE infolge des Spannungsabfalles über RC . Die Gegenkopplung

über Widerstand R1 bewirkt eine Reduktion des Basisstromes IB und damit auch eine Reduktion

des Kollektorstromes IC .

^ Die Gleichspannungsgegenkopplung stabilisiert sowohl die Ausgangsspannung UCE als auch

den Kollektorstrom IC .

1LFKWOLQHDUH6FKDOWXQJHQ]XU$36WDELOLVLHUXQJ

Zur Kompensation des Temperatureinflusses auf den Arbeitspunkt in analogen Schaltungen werden

besonders in integrierten Schaltungen Dioden und Transistoren eingesetzt (Bild 1.5.8). Meist wird

.

T ] von Transistoren

das Temperaturverhalten der BE-Spannung UBE [U BE = − (2, 2 ... 2, 5) mV

K

bzw. der Flußspannung UF von Dioden genutzt. In diskreten Schaltungen finden auch temperaturabhängige Widerstände Anwendung (Thermistor, Varistor).

^ Voraussetzung für eine effektive Wirkung der Schaltungen sind die enge thermische

Kopplung der betroffenen Bauelemente und nahezu gleiche Temperaturabhängigkeit der

entsprechenden Parameter.

UCC

R1

UCC

R1

RC

RC

A

e

A

e

R2

R

UF

D

E

U

R2

F

RE

D

Rv

UEE < 0

a) Kompensation von ∆ UBE

b) Kompensation von ∆ U BE und ∆ UCC

Bild 1.5.8: Nichtlineare Schaltungen zur Kompensation von Temperatureinflüssen

1. Elektronische Bauelemente

25

7UDQVLVWRULQ'LJLWDOVFKDOWXQJHQ

6WDWLVFKHV9HUKDOWHQ

Eine der wichtigsten Anwendungen von Transistoren ist die Realisierung HOHNWURQLVFKHU6FKDOWHU in

logischen Schaltungen (vgl. auch Abschnitt 2). Bei Schalterbetrieb des Transistors gibt es genau

zwei statisch stabile Zustände der Schaltung:

^ Schalter$86 (OFF)

^ Schalter(,1 (ON)

-

Transistor ist gesperrt,

Transistor ist leitend (übersteuert, gesättigt).

Das statische Verhalten des Transistors im Schalterbetrieb kann aus dem Ausgangskennlinienfeld

mit Widerstandsgerade (Bild 1.5.9) und/oder aus den Kennliniengleichungen abgeleitet werden.

^ Entsprechend den beiden Schaltzuständen gibt es zwei Arbeitspunkte X und Y (Bild 1.5.9).

Zur Kennzeichnung des Schaltzustandes werden nachfolgend die Kennwerte mit dem Index x

für gesättigten (leitenden) und mit dem Index y für gesperrten Transistor versehen.

IC

UCB= 0

X

I Cx

I Cü

UCC

I Bx

I Bü

RC

RB I

e

Ü

IB

Ue

PCmax

Y

I Cy

UCEx

UCEü

I

Iv

U

BE

IC

UCE

Rv

-U v

By

U

UCEy CC

IB

UCE

Bild 1.5.9: Transistorkenngrößen bei Schalterbetrieb, einfache Schaltstufe

7UDQVLVWRUJHVSHUUW (Arbeitspunkt Y)

Bei gesperrtem Transistor fließt per Definition kein Emitterstrom (IE = 0). An der6SHUUJUHQ]H fließt

wegen UCB’ >> UT der Kollektorreststrom ICB0 durch die Basis-Kollektor-Diode. Wird durch offenen

Basisanschluß oder anderweitig schaltungstechnisch IB = 0 erreicht, so kann dieser Reststrom ICB0

nicht über die Basis abfließen. Er fließt über die BE-Strecke des Transistors und bewirkt einen

Emitterstrom ICE0 = (1+BN ) . ICB0. Die Basis-Emitterstrecke ist also für IB = 0 nicht gesperrt!

Trotzdem wird die Kennlinie IB = 0 im Ausgangskennlinienfeld meist als Grenzkennlinie zwischen

aktivem Bereich und Sperrbereich angegeben (es existiert kein externes Steuersignal).

^ Im Arbeitspunkt Y (UCEy , ICy ; IBy ) für Schalterzustand AUS bzw. gesperrten Transistor gilt:

UCEy = U CC − R C ICy O UCC , ICy = ICE0 ( ICB0 < 20 nA ).

(1.5.11)

26

1. Elektronische Bauelemente

7UDQVLVWRUOHLWHQG (Arbeitspunkt X)

An der 6lWWLJXQJVbzwhEHUVWHXHUXQJVJUHQ]H (Punkt Ü in Bild 1.5.9) gilt UCB’ = 0 bzw. UCE = UBE

und aus Gl. (1.5.3) folgt ICsat = ICü = BN IBü , d.h. der Kollektorstrom ICü wird nur vom Basisstrom IB

bestimmt. Bei großen Werten des Basisstromes muß dazu noch der Spannungsabfall am inneren

Bahnwiderstand rBB’ berücksichtigt werden, es gilt dann UCB’ = - IB rBB’ .

Bei Erhöhung des Basisstromes auf IB = IBX > IBü kommt es zurhEHUVWHXHUXQJ des Transistors. Die

in die Basiszone transportierten Ladungsträger können nicht mehr linear in einen Kollektorstrom ICx

I

umgesetzt werden, d.h., die wirksame Stromverstärkung sinkt (B sat = B x = I Cx < B N ). Es stellt sich

Bx

der .ROOHNWRUVlWWLJXQJVVWURP ICx ein

U CC − U CEx

> I Cü .

RC

I Cx =

(1.5.12)

Es gilt

I Cx = I Cü + (I Cx − I Cü ) > I Cü

mit

U CC − U CEx

U − U CEü

, I Cü = CC

, U CEü > U CEx .

RC

RC

I Cx =

Zur Erzeugung dieses Sättigungszustandes muß im Basiskreis ein Strom IBx = m . IBü angeboten

werden. Der Faktor mwird hEHUVWHXHUXQJVIDNWRU genannt und praktisch zwischen m = 2 ... 10 frei

gewählt

m=

I Bx

I

= B N Bx .

I Bü

I Cü

(1.5.13)

^ Bei Übersteuerung sinkt die Ausgangsspannung von UCEü = UBEx ≈ (0,6 ... 0,8) V auf die

Rest- bzw. 6lWWLJXQJVVSDQQXQJ UCEx < 100 mV ... 300 mV.

^ Der Kollektorstrom dagegen ändert sich nur wenig (ICx ≈ ICü ), seine Größe wird fast nur noch

von der äußeren Beschaltung bestimmt (UCEx << UCC ):

I Cx =

U CC − U CEx

U

− U CEx

= I Cü + CEü

.

RC

RC

(1.5.14)

^ Damit ist der Arbeitspunkt X (ICx , UCEx ; IBx ) für den Schalterzustand EIN bzw. übersteuerten

Transistor bestimmt.

6FKDOWHUZLGHUVWlQGH

Für einen Transistorschalter können damit Ersatz-Schaltwiderstände RON und ROFF in den beiden

statischen Schaltzuständen definiert werden. Insbesondere das Verhältnis der beiden Werte ist ein

Gütemaß für einen elektronischen Schalter.

U

(,1

rCEx = R ON = I CEx

Cx

$86

rCEy = R OFF = I

O CC

I CE0

Cy

U CEy

U

(1 Ω ... 100 Ω) ,

(1.5.15)

( P 10 M).

(1.5.16)

1. Elektronische Bauelemente

27

=XUVWDWLVFKHQ%HPHVVXQJYRQ7UDQVLVWRU6FKDOWVWXIHQ