Dokument 1 - Dokumentenserverhosting der SUB

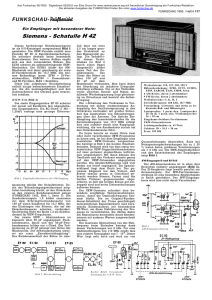

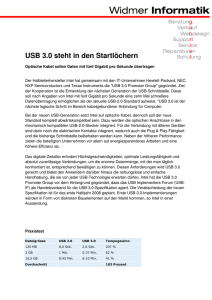

Werbung