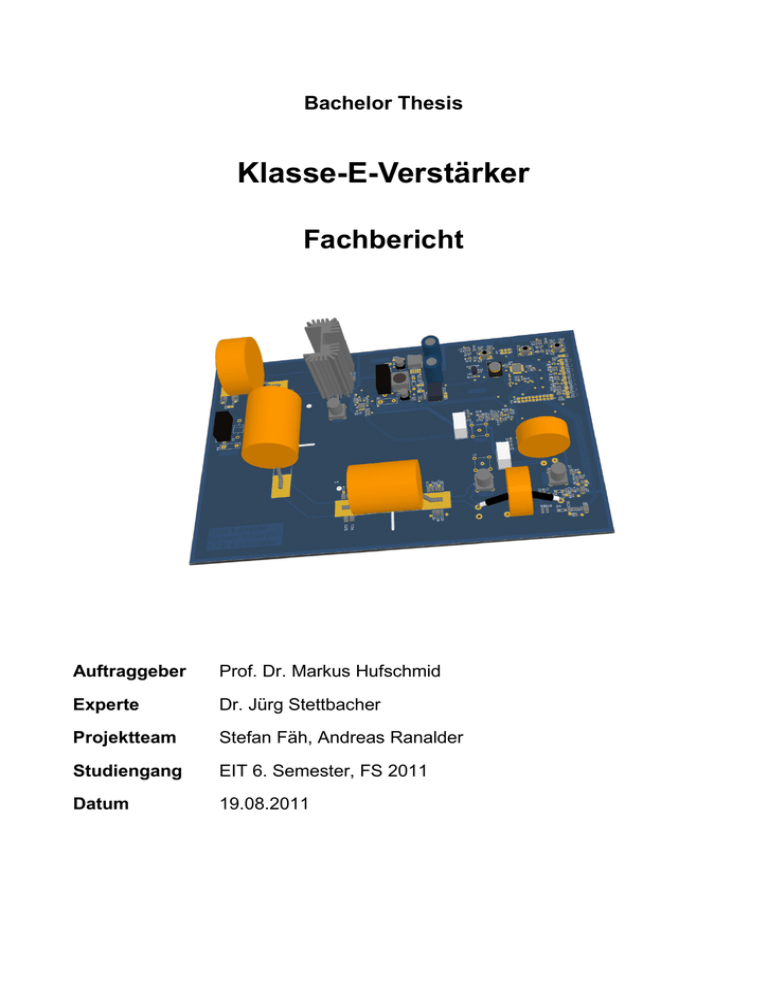

Klasse-E-Verstärker

Werbung