Slide 1 Vorlesung 9 Flynn`sche Klassifikation (vgl. Vorlesung 3

Werbung

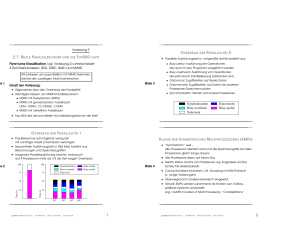

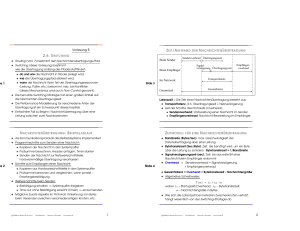

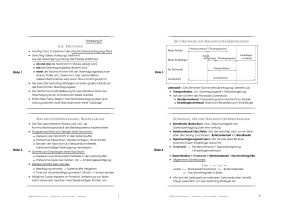

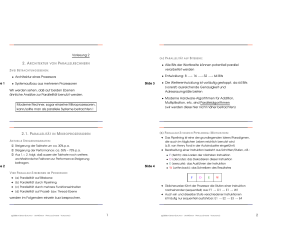

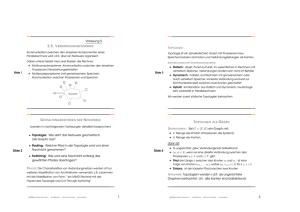

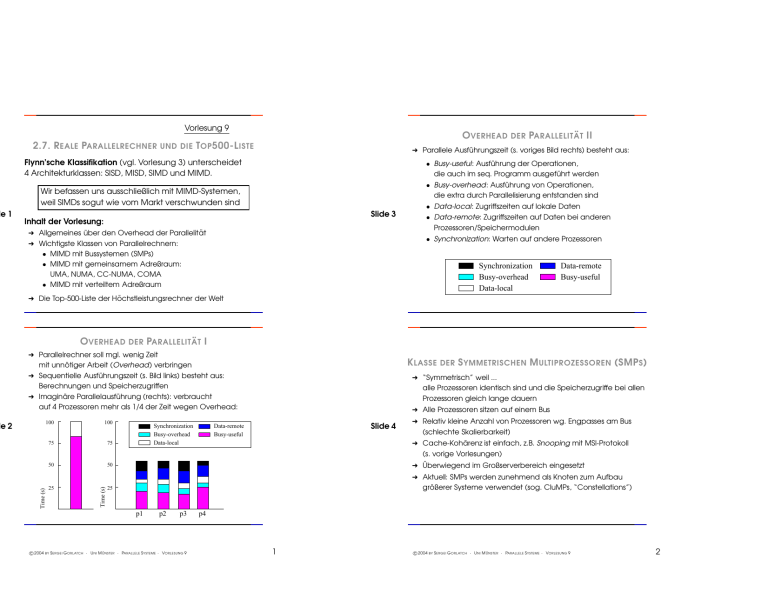

2.7. R EALE PARALLELRECHNER OVERHEAD UND DIE T OP 500-L ISTE DER PARALLELIT ÄT II ➜ Parallele Ausführungszeit (s. voriges Bild rechts) besteht aus: Flynn’sche Klassifikation (vgl. Vorlesung 3) unterscheidet 4 Architekturklassen: SISD, MISD, SIMD und MIMD. • Busy-useful: Ausführung der Operationen, die auch im seq. Programm ausgeführt werden • Busy-overhead: Ausführung von Operationen, die extra durch Parallelisierung entstanden sind Wir befassen uns ausschließlich mit MIMD-Systemen, weil SIMDs sogut wie vom Markt verschwunden sind Slide 3 Inhalt der Vorlesung: ➜ Allgemeines über den Overhead der Parallelität ➜ Wichtigste Klassen von Parallelrechnern: • MIMD mit Bussystemen (SMPs) • MIMD mit gemeinsamem Adreßraum: UMA, NUMA, CC-NUMA, COMA • MIMD mit verteiltem Adreßraum • Data-local: Zugriffszeiten auf lokale Daten • Data-remote: Zugriffszeiten auf Daten bei anderen Prozessoren/Speichermodulen • Synchronization: Warten auf andere Prozessoren Synchronization Busy-overhead Data-local Data-remote Busy-useful ➜ Die Top-500-Liste der Höchstleistungsrechner der Welt OVERHEAD DER PARALLELIT ÄT I ➜ Parallelrechner soll mgl. wenig Zeit mit unnötiger Arbeit (Overhead) verbringen ➜ Sequentielle Ausführungszeit (s. Bild links) besteht aus: Berechnungen und Speicherzugriffen ➜ Imaginäre Parallelausführung (rechts): verbraucht auf 4 Prozessoren mehr als 1/4 der Zeit wegen Overhead: Time (s) de 2 DER S YMMETRISCHEN M ULTIPROZESSOREN (SMP S ) ➜ “Symmetrisch” weil ... alle Prozessoren identisch sind und die Speicherzugriffe bei allen Prozessoren gleich lange dauern ➜ Alle Prozessoren sitzen auf einem Bus ➜ Relativ kleine Anzahl von Prozessoren wg. Engpasses am Bus (schlechte Skalierbarkeit) 100 75 75 50 50 ➜ Überwiegend im Großserverbereich eingesetzt 25 ➜ Aktuell: SMPs werden zunehmend als Knoten zum Aufbau größerer Systeme verwendet (sog. CluMPs, “Constellations”) 25 Synchronization Busy-overhead Data-local p1 c 2004 K LASSE 100 Time (s) de 1 Vorlesung 9 BY p2 p3 S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 9 Slide 4 Data-remote Busy-useful ➜ Cache-Kohärenz ist einfach, z.B. Snooping mit MSI-Protokoll (s. vorige Vorlesungen) p4 1 c 2004 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 9 2 FALLSTUDIE SMP: S UN E NTERPRISE 6000 Bus interface/switch ➜ Grobkörnig = block multithreading ➜ Kontextwechsel passiert erst bei einem Lange-Latenz-Ereignis (z.B. Cache-Miss mit Latenz 10 Taktzyklen) ➜ Miss festgestellt ⇒ mehrere nachstende Instruktionen müssen aus der Pipeline entfernt werden ⇒ contextswitch overhead 2 FiberChannel Mem ctrl SBUS $2 SBUS $2 SBUS P $ 100bT, SCSI P $ Bus interface I/O cards de 5 de 6 G ROBK ÖRNIGER KONTEXTWECHSEL CPU/mem cards Slide 7 Gigaplane bus ( 256 data, 41 address, 83 MHz ) MIT Busy cycle from threads A-D, respectively Thread B Context switch overhead Idle (stall) cycle Thread C ➜ Bis zu 30 Ultra-SPARC-Prozessoren ➜ Auch Board-lokale Zugriffe laufen über den Bus (UMA = Uniform Memory Access) ➜ In jedem Prozessor: 16KB L1-Cache und 512KB L2-Cache ➜ Cache-Kohärenz: eine Variante des MSI-Protokolls ➜ Zugriff auf den Cache ist um ca. eine Größenordnung schneller als Zugriff über den Bus (40 ns vs. 300 ns) G EMEINSAMER A DRESSRAUM : UMA Thread A Abbreviation for four ... = context switch cycles = Thread D Memory latency Pipeline latency Four context switch cycles ... ➜ Feinkörniger Kontextwechsel: interleaved multithreading ➜ Nach jeder Instruktion wird aus einem Thread-Pool gewählt ➜ Es gibt keinen Kontextswitch-Overhead wie beim grobkörnigen ➜ Wachsender Abstand zwischen Prozessor- und Speicherleistung ⇒ mehr Threads pro Prozessor nötig Memory latency Pipeline latency Thread D Thread A ➜ Kontextwechsel in Hardware ⇒ spezielle Prozessoren nötig (kleine Stückzahlen, teuer) Memory latency Memory latency Slide 8 ➜ Herausforderung für Programmierer: nicht die Lokalität der Zugriffe, sondern genügend Parallelität zu identifizieren ➜ Keine Software-Unterstützung nötig Thread E Thread B Thread C ➜ Ist dynamisch, d.h. gut für unvorhersehbare Situationen (Cache-Misses etc.) Thread F Memory latency Pipeline latency ➜ Zwei Arten – Grobkörniger und Feinkörniger Kontextwechsel: • Grob: Wechsel erst nach Bedarf S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 9 Busy cycles from threads A−F, respectively Idle (stall) cycle • Fein: Wechsel in jedem Taktzyklus BY ... F EINK ÖRNIGER KONTEXTWECHSEL M ULTITHREADING ➜ Idee: Kommunikationslatenz und andere Wartezeiten durch Kontextwechsel verbergen c 2004 ... 3 c 2004 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 9 4 de 9 e 10 FALLSTUDIE NUMA: C RAY T3E ➜ Eine 24-Knoten Cray T3E ist z.B. an der TU Berlin vorhanden FALLSTUDIE M ULTITHREADED -A RCHITEKTUR – Tera MTA ➜ Ein Knoten beinhaltet: Prozessor, Kontrollchip, lokalen Speicher, Netzwerk-Interface ➜ Prozessor unterstützt 128 aktive Threads in Hardware ➜ Caches: ➜ Interleaved Multithreading ➜ VLIW-Prozessor = ... mehrere FUs mit statischem Scheduling Slide 11 ➜ Verbindungstopologie: 3D-Torus ➜ Keine Caches ⇒ bis zu 8 ausstehende Speicherzugriffe je Thread erlaubt ➜ Sehr spezielle Prozessoren ➜ Der Programmierer oder der Compiler muß viele Threads produzieren • Je ein 8K direct-mapped Instruktions- und Datencache • Ein 96K on-chip L2-Cache – drei-Wege-assoziativ, mit 64-Byte-Blöcken • In Caches können nur lokale Daten abgelegt werden (kein Hardware-Mechanismus für ihre Kohärenz) • Bei nicht-lokalem Zugriff von außen werden Daten im Cache als ungültig markiert • Alle lokalen Speicher sind zwar für alle Prozessoren zugänglich, ihre Zugehörigkeit sollte für effizientes Programmieren jedoch berücksichtigt werden ➜ Netztopologie: 3D-Torus (Knotengrad?) Gemeinsamer Adreßraum: NUMA FALLSTUDIE NUMA: C RAY T3E – B ILD ➜ Physikalisch sind die Speichermodule auf die Knoten verteilt ➜ Die Zugriffszeit hängt vom zugreifenden Prozessor und von der zugegriffenen Speicheradresse ab External I/O P ➜ Logisch sind alle Speichermodule für alle Prozessoren direkt zugreifbar, ohne Mitwirken des Inhaber-Prozessors Mem $ ➜ Cache-Kohärenz wird nicht in Hardware unterstützt ⇒ nur lokale Daten sind cacheable Slide 12 Mem ctrl and NI Beispiel: Cray T3E X Switch Y Z c 2004 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 9 5 c 2004 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 9 6 e 13 CC-NUMA R ECHNER ➜ CC-NUMA = cache-coherent non-uniform memory access MIT VER TEILTEM A DRESSRAUM ➜ Cache-Kohärenz wird per Hardware sichergestellt ➜ Anwendungsgebiet: überwiegend wissenschaftlich-technische Simulationen (Wettervorhersage, Crash-Verhalten, GAUs, etc.) ➜ Erste CC-NUMA Maschine war DASH in Stanford (1992) ➜ + : Gutes Preis-Leistungs-Verhältnis, Skalierbarkeit ➜ – : Wegen verteiltem Adreßraum aufwendiges Programmieren FALLSTUDIE SGI O RIGIN 2000: Fallstudie: IBM SP2 ➜ Bis zu 1024 Prozessoren ➜ Knoten = zwei Prozessoren, bis zu 4 GB Speicher, ein Cache-Controller, sowie Router (“R” im Bild) R Topologie bis zu 16 Knoten – Hypercube; danach Fattree mit Meta-Routers Slide 15 ➜ Weiterentwicklung von SP2: mit SMP-Knoten je 4/8 Prozessoren ⇒ ASCI Blue, sowie SP3 mit Power3-Prozessoren R R ➜ Topologie, Routing und Switching: R R • Einzelne Switches sind Crossbars R R ➜ SP2 = Scalable Power, mit superscalaren Prozessoren (d.h. mehrere FUs mit dynamischem Scheduling) • Quellenbasiertes, tabellengetriebenes Routing • Paketbasiertes, cut-through Switching R • Pakete bis 255 Byte lang, Phit = 1 Byte, Flit = 2 Byte SGI O RIGIN 2000: G R ÖSSERE T OPLOGIEN R R R R R R R R R R R R R R C LUSTERMASCHINEN R M Slide 16 M M M R R R R c 2004 R R R R BY ➜ Anwendungsgebiete: Server, Webserver ➜ Cluster können sowohl zu (CC-)NUMA als auch zu Maschinen mit verteiltem Adressraum gehören M R ➜ Netze: ursprünglich LAN oder WAN, langsam ➜ Aktuell: schnellere Netze wie ATM, Myrinet, SCI, etc. M R W ORKSTATIONNETZE ➜ Cluster = Ansammlung (fast) eigenständiger Rechner, verbunden über ein Netzwerk R M M e 14 UND R R R R S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 9 R R 7 c 2004 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 9 8 D IE T OP 500 L ISTE ➜ Wird seit 1993 erstellt ➜ Leistungskriterium – Performance in Mflops auf Linpack, d.h. Lineares Gleichungssystem Ax = b mit vollbesetzter Matrix ➜ Das Problem welches 1980 etwa 1 Jahr Rechenzeit brauchte, hat später soviel Zeit verbraucht: • 1992 - 1 Monat • 1997 - 4 Stunden • 2000 - 1 Stunde e 17 Slide 19 ➜ Momentan stärkster Rechner: Earth Simulator (Japan), 640 Knoten mit je 8 Vektorprozessoren. Kabellänge: 1800 Meilen, 4 Tennisplätze, 3 Stockwerke ➜ Auch selbstgebaute Cluster dabei, darunter mit bestem Preis-Lestungsverhältnis Virginia Tech auf Platz 3: 2200 Prozessoren, Rmax = 10280 Gflops ➜ Probleme mit Linpack: kommerzielle DB-Systeme – kein Interesse an Gflops; neue Architekturen sind nicht dazu entwickelt e 18 Slide 20 ... c 2004 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 9 9 c 2004 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 9 10 e 21 Slide 23 e 22 Slide 24 c 2004 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 9 11 c 2004 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 9 12 e 25 e 26 c 2004 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 9 13