Vorlesung 2 • Architektur eines Prozessors • Systemaufbau aus

Werbung

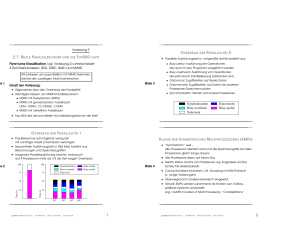

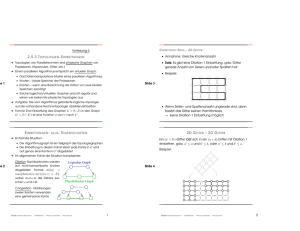

Vorlesung 2 2. A RCHITEKTUR VON PARALLELRECHNERN Z WEI B ETRACHTUNGSEBENEN SIND M ÖGLICH :: • Architektur eines Prozessors • Systemaufbau aus mehreren Prozessoren Wir werden sehen, daß auf beiden Ebenen ähnliche Ansätze zur Parallelität benutzt werden. Moderne Rechner, sogar einzelne Mikroprozessoren, kann/sollte man als parallele Systeme betrachten ! c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 1 2.1. PARALLELIT ÄT IN M IKROPROZESSOREN A KTUELLE S TEIGERUNGSRATEN : ➀ Steigerung der Taktrate um ca. 30% p.a. ➁ Steigerung der Performance: ca. 55% – 75% p.a. ➂ Aus 1.< 2. folgt, daß ausser der Taktrate noch weitere, architektonische Faktoren zur Performance-Steigerung beitragen. V IER PARALLELIT ÄTSEBENEN IM P ROZESSOR : ➜ (a) Parallelität auf Bitebene ➜ (b) Parallelität durch Pipelining ➜ (c) Parallelität durch mehrere Funktionseinheiten ➜ (d) Parallelität auf Prozeß- bzw. Thread-Ebene werden im Folgenden einzeln kurz besprochen. c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 2 ( A ) PARALLELIT ÄT AUF B ITEBENE : • Alle Bits der Wortbreite können potentiell parallel verarbeitet werden • Entwicklung: 8 −→ 16 −→ 32 −→ 64 Bits • Die Weiterentwicklung ist vorläufig gestoppt, da 64 Bits (vorerst) ausreichende Genauigkeit und Adressraumgröße bieten • Moderne Hardware-Algortihmen für Addition, Multiplikation, etc. sind Parallelalgorithmen (wir werden diese hier nicht näher betrachten) c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 3 ( B ) PARALLELIT ÄT DURCH P IPELINING : M OTIVATION : ➜ Das Pipelining ist eine der grundlegenden Ideen/Paradigmen, die auch im täglichen Leben reichlich benutzt wird (z.B. von Henry Ford in der Autoindustrie eingeführt) ➜ Bearbeitung einer Instruktion besteht aus Schritten/Stufen, z.B.: • • • • F (fetch): das Laden der nächsten Instruktion D (decode): das Dekodieren dieser Instruktion E (execute): das Ausführen der Instruktion W (write-back): das Schreiben des Resultates F D E W ➜ Üblicherweise führt der Prozessor die Stufen einer Instruktion nacheinander (sequentiell) aus: F1 → D1 → E1 → W1 ➜ Auch ein und dieselbe Stufe verschiedener Instruktionen ist häufig nur sequentiell ausführbar: E1 → E2 → E3 → E4 c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 4 P IPELINING : D IE I DEE ➜ Möglichkeit der Parallelität bei diesen Abhängigkeiten zwischen den Stufen: gleichzeitig unterschiedliche Stufen mehrerer Instruktionen, z.B.: W1 || E2 || D3 || F4 ➜ Dies erreicht man durch Pipelining ≈ verzahnt-parallele Ausführung, z.B. wie folgt: Instruktionen F4 D4 E4 F3 D3 E3 W3 F2 D2 E2 W2 D1 E1 W1 4 3 2 1 F1 W4 Zeit 4 Instruktionen brauchen anstatt 4*4=16 lediglich 7 Zeitschritte c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 5 P IPELINING : B EOBACHTUNGEN ➜ Der Speedup wächst mit der Anzahl der Instruktionen ➜ Pipelining ist effizient, wenn verschiedene Pipelinestufen etwa gleich lange dauern ➜ Die Anzahl der Stufen (in der Praxis: zwischen 2 und 20) bestimmt den Parallelitätsgrad ➜ Prozessoren mit vielen Stufen heißen super-pipelined. ➜ Grenzen für die Stufenanzahl/Parallelitätsgrad: • Instruktionen nicht beliebig in gleich große Stufen zerlegbar • Datenabhängigkeiten zwischen Instruktionen • ... und viele andere c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 6 ( C ) PARALLELIT ÄT DURCH MEHRERE F UNKTIONSEINHEITEN ➜ Abkürzung FU = Functional Unit ➜ ALUs, FPUs, etc. können parallel zueinander arbeiten ➜ Zwei Prozessorarten, die mehrere FUs benutzen: ➀ VLIW-Prozessoren (z.B. IA 64) • Beim Übersetzen wird Maschinencode erzeugt, der die zeitliche Verteilung von Instruktionen auf FUs angibt • Die Instruktionsworte werden dadurch lang =⇒ Very Long Instruction Word = VLIW • Das ist statisches Scheduling, d.h. vor der Ausführung, im Gegensatz zum Scheduling zur Laufzeit (dynamisch) ➁ Superscalare Prozessoren (z.B. Pentium) • Teile des Maschinencodes werden per Hardware während der Ausführung den FUs zugeteilt, d.h. zur Laufzeit • Dies ist dynamisches Scheduling durch Analyse der bestehenden Datenabhängigkeiten! ➜ Moderne Prozessoren: 2 bis 6 gleichzeitige Instruktionen c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 7 S UPERSCALARE P ROZESSOREN UND I NSTRUKTIONSFENSTER ➜ Dynamisches Scheduling kostet viel Overhead (Chipfläche), trotzdem werden z.Zt. superscalare Prozessoren bevorzugt ➜ Kosten vs. Nutzen: bei ca. 4 absetzbaren Instruktionen ist die Grenze in etwa erreicht (z.B. in Pentium maximal 3) ➜ Dekodierte Instruktionen werden im sog. Instruktionsfenster abgelegt und, sobald Operanden verfügbar sind, an FU weitergegeben (dispatch) ➜ Korrektheit: Die (funktionale) Semantik des Programms darf durch die parallele Abarbeitung nicht geändert werden ➜ Dies wird vom reorder buffer garantiert: die Ergebnisse werden erst dann in die Register geschrieben, wenn alle vorherige Instruktionen ihre Ergebnisse reingeschrieben haben. c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 8 ( D ) PARALLELIT ÄT AUF P ROZESS - BZW. T HREADEBENE ➜ Bisher sind wir immer von einem Kontrollfluß ausgegangen ➜ Zusätzliche Möglichkeit: Erhöhung des Parallelitätsgrades durch mehrere Kontrollflüsse ➜ Heutzutage auf Prozessorebene noch selten benutzt, ist Gegenstand aktueller Forschung & Entwicklung ➜ Einschlägige Techniken aus der Parallelprogrammierung (siehe später) werden zunehmend in einzelnen Prozessoren eingesetzt, z.B. HTT - Hyper-Threading Technology von Intel ➜ Siehe “Multithreading” in späteren Kapiteln Drei allgemeine Informatik-Aspekte spielen hier eine Rolle: ➜ Statisch vs. Dynamisch (zur Compile- vs. zur Laufzeit) ➜ Nutzen/Optimierung vs. Kosten/Overhead ➜ Korrektheit: Semantik-erhaltende Transformationen c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 9 2.2. K LASSIFIZIERUNG VON PARALLELRECHNERN Wir widmen uns nun dem Aufbau von Parallelrechnern durch das Verbinden mehrerer Prozessoren Eine (noch intuitive und vage) Definition: Ein Parallelrechner ist eine Ansammlung von Recheneinheiten (Prozessoren), die durch koordinierte Zusammenarbeit komplexe Anwendungen schneller lösen können Viele Details in dieser Definition bleiben offen: ➜ ➜ ➜ ➜ Anzahl und Komplexität der Recheneinheiten Struktur der Verbindungen zwischen den Prozessoren Art der Koordination ... und vieles mehr Diese Details werden durch Klassifizierungen festgelegt c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 10 K LASSIFIZIERUNG NACH M. F LYNN [1972] ➜ ➜ ➜ ➜ Eine der ersten Klassifizierungen überhaupt Ist immer noch die meistbenutzte Vorteil: sehr einfach Klassifiziert wird nach zwei Merkmalen: ➀ I ( Instruction): Organisation des Kontrollflusses ➁ D ( Data): Organisation des Datenflusses ➜ Jedes Merkmal kann einen der zwei Werte annehmen: ➀ S: für Single ➁ M: für Multiple ➜ Somit erhält man 4 mögliche Kombinationen: Instruction Data c 2006 BY S M S SISD MISD M SIMD MIMD S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 11 F LYNNSCHE K LASSIFIKATION : SISD Ein Verarbeitungsschritt besteht aus: ➜ Laden einer Instruktion aus dem Programmspeicher ➜ Laden angesprochener Daten aus dem Datenspeicher ➜ Anwendung der Instruktion auf die Daten ➜ Zurückspeichern des Resultates Datenspeicher Prozessor Programmspeicher SISD ≈ Klassisches Von-Neumann-Rechnermodell c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 12 F LYNNSCHE K LASSIFIKATION : MISD Ein Verarbeitungsschritt besteht aus: ➜ Laden einer Instruktion aus eigenem Programmspeicher ➜ Laden derselben Daten aus dem Datenspeicher ➜ Anwendung verschiedener Instruktionen auf dasselbe Datum Datenspeicher Prozessor 1 Programmspeicher 1 . . . . . . Prozessor n Programmspeicher n Keine der gegenwärtigen Architekturen entspricht genau dem MISD-Modell ⇒ bisher keine praktische Bedeutung c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 13 F LYNNSCHE K LASSIFIKATION : SIMD Verarbeitungsschritt: ➜ Laden derselben Instruktion aus (globalem) Programmspeicher ➜ Laden separater Daten aus (gemeinsamem oder verteiltem) Datenspeicher ➜ Synchrone Ausführung der Instruktion auf allen Daten ➜ Beispielanwendung: Seismologie Prozessor 1 Daten speicher .. . Programmspeicher Prozessor n Mehrere realisierte SIMD-Rechner: z.B. Connection Machine (bis ca. 65K Prozessoren), MasPar, etc. bis zur Mitte der 90er c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 14 F LYNNSCHE K LASSIFIKATION : MIMD Ein Verarbeitungsschritt besteht aus: ➜ Laden einer Instruktion aus eigenem Programmspeicher ➜ Laden separater Daten ➜ Asynchrone Abarbeitung der jeweiligen Instruktionen Daten speicher Prozessor 1 Programmspeicher 1 . .. . .. Prozessor n Programmspeicher n MIMD ist das z.Zt. populärste Parallelrechnermodell. Die meisten Parallelrechner sind MIMD-Architekturen, bzw. Hybride, z.B.: MIMD-Maschinen mit SIMD-Knoten c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 15 V ERGLEICH : SIMD VS . MIMD • Vorteil SIMD: nur ein Kontrollfluß =⇒ einfach zu programmieren, da alle Prozessoren gleichzeitig nur ein Kommando ausführen (oder setzen durch Maskierung aus) • Nachteile SIMD: ➜ Streng synchrone Abarbeitung bremst die Geschwindigkeit ⇒ Statement if (b==0) c=a; else c=a/b; benötigt zur Ausführung zwei Schritte: (1) Ein Teil der Prozessoren berechnet c=a; (2) Anderer Teil berechnet c=a/b. ➜ SIMD-Rechner benötigen spezialisierte Prozessoren • Renaissance von SIMD – PlayStation 3 von Sony! Verwendet den Cell-Prozessor von IBM (s. nächste Folie) c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 16 C ELL -P ROZESSOR VON IBM Hohe Leistung durch 8 Synergistic Processor Elements (SPEs) erreicht: ➜ SPE – vollständiger SIMD-Processor mit 128 Registern je 128 Bit ➜ 4 Floating-point Units + 4 Integer Units, insg. 32 GFlops/GOps ➜ Peak Performance des Prozessors: 32 X 8 SPEs = 256 GFLOPS ➜ Die Parallelisierung für PPEs wird vom Compiler gemacht, Prozessor selbst ändert die Reihenfolge der Instruktionen nicht. c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 17 K LASSIFIKATION NACH DER O RGANISATION DES S PEICHERS ➀ Physisch (aus der Sicht des Systemarchitekten) : Parallele und verteilte MIMD-Rechnersysteme Multicomputer Speicher ist physisch verteilt Rechner mit virtuell (durch Hardware) gemeinsamem Speicher Multiprozessoren Speicher ist physisch gemeinsam ➁ Logisch (aus der Sicht des Programmierers) : ➜ verteilter Adreßraum ➜ gemeinsamer Adreßraum Physische und logische Sicht sind zueinander orthogonal ! c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 18 R ECHNER MIT PHYSISCH VER TEILTEM S PEICHER I AUFBAU : ➜ Mehrere Recheneinheiten (Knoten) bestehend aus: Prozessor, lokalem bzw. privatem Speicher, I/O ➜ Verbindungsnetzwerk, das die Knoten durch physische Leitungen verbindet Verbindungsnetzwerk P = Prozessor M = lokaler Speicher P P M M ... P M DATENSPEICHERUNG : ➜ Speicherung und direkter Zugriff auf lokalen Speicher ➜ Zugriff auf Speicher anderer Knoten nur über das Netzwerk, mit “Einverständnis” des Eigentümers c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 19 R ECHNER MIT PHYSISCH VER TEILTEM S PEICHER II P ROGRAMMIERMODELL : ➜ Entspricht dem physischen Aufbau ➜ Expliziter Nachrichtenaustausch (message passing) über das Verbindungsnetzwerk ➜ Komplementäre Sende- und Empfangsbefehle (Send – Receive) • Sendebefehl: PA sendet Nachricht m an PB • Empfangsbefehl: PB empfängt Nachricht von PA in Puffer b und bearbeitet den Puffer anschließend H ERAUSFORDERUNG F ÜR P ROGRAMMIERER : Das Programmieren vom expliziten Nachrichtenaustausch ist aufwendig und fehleranfällig, insb. müssen einzelne Sende- und Empfangsbefehle aufeinander abgestimmt werden. Details dazu – später. c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 20 H ISTORISCHE E NTWICKLUNG VON VER TEILTEM S PEICHER I P UNKT- ZU -P UNKT V ERBINDUNG ( IN ERSTEN PARALLELRECHNERN ): ➜ Ein Knoten ist mit einer festen Menge von anderen Knoten durch physische Leitungen (Links) verbunden ➜ Kommunikation nur mit direkten Nachbarn, entfernte Kommunikation durch die Nachbar-Verbindungen realisiert ➜ Gleichzeitiges Senden und Empfangen evtl. möglich ➜ Die Kommunikation wird vom Programmierer explizit organisiert Computer with distributed memory and a hypercube network c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 21 E NTWICKLUNG VON VER TEILTEM S PEICHER II: DMA-C ONTROLLER ➜ DMA = direct memory access ➜ Direkter Datentransfer zwischen lokalem Speicher und I/O-Anschluß: entkoppelt Kommunikation vom Prozessor ➜ Kommunikation zwischen Nachbar-Knoten ist nicht-blockierend: • Sender initiiert die Kommunikation (und arbeitet weiter) • Die Nachricht wird vom DMA im Empfänger gepuffert • Empfänger entnimmt die Nachricht aus dem Puffer ➜ Entfernte Kommunikation wird durch Software über Nachbar-Links aufgebaut und dauert relativ lange Parallelrechner mit DMA−Verbindungen zum Netzwerk Verbindungsnetzwerk .. . DMA M c 2006 BY P DMA M P S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 22 E NTWICKLUNG VON VER TEILTEM S PEICHER III: H ARDWARE -R OUTER ➜ Entfernte Kommunikation wird von Routern (einer pro Knoten) realisiert, was die Zwischenknoten zusätzlich entlastet ➜ Folge: Entfernungen im Netzerk spielen immer geringere Rolle ➜ Router und Leitungen bilden das eigentliche Netzwerk ➜ Aufgaben des Routers: Pipelining von Nachrichten, Vermeidung von Konflikten und Verklemmungen im Netz ➜ So werden hierarchische Systeme (Cluster) aufgebaut N N R R N R R N N R R c 2006 R BY N = Knoten bestehend aus Prozessor und lokalem Speicher N R M R = Router N N R P N .. ... ... Router externe Eingabekanaele S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 .. . externe Ausgabekanaele 23 R ECHNER MIT PHYSISCH GEMEINSAMEM S PEICHER I AUFBAU : ➜ mehrere Prozessoren ➜ gemeinsamer bzw. globaler Speicher, evtl. in Speichermodulen aufgeteilt, siehe b) ➜ Verbindungsnetzwerk, das die Prozessoren und gemeinsamen Speicher verbindet a) b) P . . . P P M c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 P Verbindungsnetzwerk Verbindungsnetzwerk Gemeinsamer Speicher . . . . . . M Speichermodule 24 R ECHNER MIT PHYSISCH GEMEINSAMEM S PEICHER II P ROGRAMMIERMODELL : ➜ Gemeinsame Variablen (shared variables) ➜ Verwendung von Multithreading: mehrere leichtgewichtige Prozesse arbeiten gleichzeitig (mehr dazu später) ➜ Prozessoren greifen auf gemeinsamen Speicher zu ⇒ Lese- und Schreibkonflikte möglich B EWER TUNG : + relativ einfache Programmierung (Diskussionsfrage, da Konflikte und Synchronisierungsprobleme möglich) + gute Speicherausnutzung: keine Datenreplizierung nötig – Speicherzugriffe aller Prozessoren erfolgen über ein Netzwerk: ⇒ hohe Hardware-Anforderung ⇒ Skalierbarkeit/Erweiterbarkeit des Systems problematisch c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 25 SMP – SYMMETRISCHE M ULTIPROZESSOREN I “Symmetrisch” bedeutet: Alle Prozessoren haben gleiche Funktionalität und gleiche Sicht auf den Gesamtspeicher, insb. gleiche Zugriffsdauer AUFBAU : ➜ Speicherzugriff über einen Bus (potentieller Flaschenhals) ➜ Kein zusätzlicher privater Speicher, evtl. Prozessor-Caches P1 Cache P2 . . . P3 Cache Cache Bus Speicher c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 26 SMP – SYMMETRISCHE M ULTIPROZESSOREN II E INSATZ VON SMP S : • Quasi Industrie-Standard seit mehr als 20 Jahren für Hochleistungsserver, z.B. bei Großbanken. • Werden auch als UMA-Maschinen bezeichnet UMA = Uniform Memory Access • Beispiele: SUN Enterprise und SGI Challenge Systeme • Relativ niedrige Anzahl von Prozessoren wegen Skalierbarkeit (Flaschenhals s.o.!), i.d.R.: bis 30-60 c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 27 R ECHNER MIT VIR TUELL GEMEINSAMEM S PEICHER ➜ Physisch: verteilter Speicher, i.d.R. hierarchisch ➜ Logisch: gemeinsamer Adreßraum durch Kohärenzprotokolle (mehr dazu später) ➜ Unterschiedliche Speicherzugriffszeiten in Abhängigkeit von der Speicheradresse ➜ Bezeichnung: NUMA-Maschinen = Non-Uniform Memory Access p p 1 ... 2 p n schnell M1 M2 Mn langsam Verbindungsnetzwerk c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 28 M ETHODEN ZUR R EDUKTION DER S PEICHERZUGRIFFSZEITEN ➜ Multithreading: jeder physische Prozessor simuliert eine feste Anzahl von virtuellen Prozessoren (abwechselnd) ⇒ verbirgt die Latenz der Speicherzugriffe ➜ Cache: kleiner, sehr schneller Speicher zwischen Prozessor und Hauptspeicher; mehr dazu nächste Vorlesung ⇒ Reduktion der transportierten Daten durch Speicherung häufig genutzter Daten im Cache ➜ Beachte: Cache 6= Cash :–) es wird jedoch manchmal Zeichen $ für Cache verwendet. c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 29 CC-NUMA ➜ CC-NUMA – Cache-Coherent NUMA (siehe Bild) ➜ Der Cache kann Daten aus lokalem und aus virtuell gemeinsamem Speicher aufnehmen ➜ Die “Richtigkeit” von Daten (Cache-Kohärenz) wird von Hardware gewährleistet ➜ Beispiele: SGI Origin 2000, Cray T3E P1 P2 C1 C2 M1 ... Pn Cn M2 Mn Verbindungsnetzwerk c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 30 NC-NUMA UND COMA ➜ NC-NUMA = Non-Coherent NUMA: Hardware gewährleistet keine Kohärenz, deshalb enthält der Cache nur Daten der lokalen Speicher oder Variablen, die nur gelesen werden können ➜ Beispiel: Cray T3D – Vorgänger von Cray T3E ➜ COMA = Cache Only Memory Access (z.B. KSR 1/2): der ganze Speicher besteht aus individuellen Caches Prozessor P1 P2 Cache C1 C2 . . . Pn Cn Verbindungsnetzwerk ➜ Dynamische Speicherzuordnung, hoher Hardwareaufwand c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 31 WAS HABEN WIR HEUTE GELERNT ➜ Bereits im Prozessor gibt es 4 Ebenen der Parallelität ➜ Viele Ideen (Pipelining, Multithreading, etc.) sind an mehreren Ebenen der Parallelität einsetzbar ➜ Moderne Prozessoren sind i.d.R. super-pipelined, sowie superscalar oder VLIW ➜ Flynnsche Klassifizierung unterscheidet 4 Architekturklassen: SISD, MISD, SIMD, MIMD ➜ Speicher kann gemeinsam, verteilt oder virtuell gemeinsam sein ➜ DMA und Router befreien den Programmierer von expliziter Kommunikations-Organisation ➜ Beim (virtuell) gemeinsamen Speicher spielt die Daten-Kohärenz eine entscheidende Rolle Nächste Vorlesungen: Caches, Kohärenz, Konsistenz, etc. c 2006 BY S ERGEI G ORLATCH · U NI M ÜNSTER · PARALLELE S YSTEME · VORLESUNG 2 32