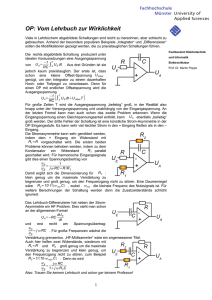

Schaltungstechnik Vorlesungsbegleitende

Werbung