Arithmetik

Werbung

Arithmetik

Einführung in die Technische Informatik

Falko Dressler, Stefan Podlipnig

Universität Innsbruck

Übersicht

•

•

•

•

•

Zahlendarstellung

Addition und Subtraktion

Multiplikation

Division

Fest- und Gleitkommazahlen

Einführung in die Technische Informatik - WS 11/12

Arithmetik

2

Lernziele

• Realisierung von Rechenwerken für alle vier arithmetischen

Grundoperationen (+, –, *, /) auf ganzen Zahlen mit

Implementierung als Schaltnetz bzw. Schaltwerk

Abschätzung des Zeitbedarfs für eine Operation

Möglichkeiten der Beschleunigung

Behandlung negativer Zahlen.

• Darstellung und Rechnen von/mit Festkommazahlen

• Verständnis von Gleitkommazahlen

Aufbau gemäß IEEE 754 Standard

Algorithmen für Grundoperationen

Realisierung von Rechenwerken

Einführung in die Technische Informatik - WS 11/12

Arithmetik

3

ZAHLENDARSTELLUNG

Einführung in die Technische Informatik - WS 11/12

Arithmetik

4

Zahlendarstellungen im Rechner

• Ausschließliche Verwendung von Binärzahlen, die auf Worte einer

Breite von n Bit abgebildet werden.

• Im Prozessor stehen zur Speicherung ganzer Zahlen mehrere n-Bit

Register (realisiert durch n Flip-Flops) zur Verfügung.

• Typische Wortbreiten:

n = 8:

n = 16:

n = 32:

n = 64:

Byte, in Mikroprozessoren der ersten Generation, wie

z.B. Intel 8080 oder Z80.

Halbwort (bei Intel: Wort) in Minicomputern und

Mikroprozessoren der zweiten Generation, wie z.B.

PDP-11, Intel 8086, Motorola 68000.

Wort (bei Intel: Doppelwort) in Mikroprozessoren der

dritten Generation, z.B. Intel Pentium, Motorola 68040.

Doppelwort (bei Intel: Quadwort) in aktuellen

Hochleistungsprozessoren, z.B. PowerPC, AMD Opteron.

Einführung in die Technische Informatik - WS 11/12

Arithmetik

5

Darstellung von Zahlen (Wiederholung)

• Darstellung positiver ganzer Zahlen in positionaler Notation (auch

als Stellenwertsystem bezeichnet).

• Jede natürliche Zahl z mit 0 z bn –1 ist eindeutig als n-stellige

Zahl zur Basis b darstellbar.

• Darstellung negativer ganzer Zahlen:

Vorzeichen und Betrag

(b-1)-Komplement (Bei Binärzahlen: Einerkomplement)

b-Komplement (Bei Binärzahlen: Zweierkomplement)

• Details: Siehe Vorlesung Praktische Informatik!

Einführung in die Technische Informatik - WS 11/12

Arithmetik

6

ADDITION UND SUBTRAKTION

Einführung in die Technische Informatik - WS 11/12

Arithmetik

7

Addition (1)

• Addition zweier positiver n-stelliger Binärzahlen a und b kann

stellenweise von rechts nach links durchgeführt werden.

Der handschriftlichen Addition zweier Dezimalzahlen entsprechend!

• In jeder Stelle i kann ein Übertrag ci = 1 auftreten (Carry).

• Gilt für die Summe s = a + b 2n, so kann das Ergebnis nicht mehr

als n-Bit Zahl dargestellt werden.

Es entsteht ein (n+1)-tes Summenbit, das als Überlauf (Overflow) bezeichnet

wird.

Einführung in die Technische Informatik - WS 11/12

Arithmetik

8

Addition (2)

• Addition der niedrigstwertigen Bits von a und b erfordert einen

Halbaddierer, der aus a0 und b0 sowohl die Summe s0 als auch den

Übertrag (Carry) c0 ermittelt.

• Verzögerung für c0: (mit = Laufzeit eines elementaren Gatters)

Verzögerung für s0: 2

Einführung in die Technische Informatik - WS 11/12

Arithmetik

9

Addition (3)

• Addition von ai, bi und ci–1 an den Bitpositionen i = 1, ... , n–1

erfordert einen Volladdierer (FA = Full Adder), der die Summe si

und den Übertrag ci bestimmt:

• Verzögerung je nach Pfad und Realisierung: 2 bis 4

Einführung in die Technische Informatik - WS 11/12

Arithmetik

10

Einfache Addierwerke (1)

• Serielles binäres Addierwerk:

Benötigt nur einen Volladdierer, ein Flip-Flop und drei n-Bit Schieberegister

(für Summanden a, b und Ergebnis s):

Synchrones Schaltwerk

Flip-Flop muss jedoch zuvor initialisiert werden.

In Takt i wird Ergebnisbit si aus ai, bi und ci–1 bestimmt.

Addition von zwei n-Bit Zahlen benötigt n Taktzyklen.

Einführung in die Technische Informatik - WS 11/12

Arithmetik

11

Einfache Addierwerke (2)

• Paralleles binäres Addierwerk:

n Volladdierer ermöglichen Addition zweier n-Bit Zahlen:

An Bitposition 0 genügt bei der Addition zweier positiver Zahlen auch ein

Halbaddierer.

Im ungünstigen Fall kann ein an Position 0 entstehender Übertrag die

Bitstellen 1 bis n –1 durchlaufen und s1 bis sn–1 verändern.

Wird daher auch als „Ripple Carry“ - Addierer (RCA) bezeichnet.

Resultierende maximale Verzögerung: 2 + (n –1) 2 = 2n

Einführung in die Technische Informatik - WS 11/12

Arithmetik

12

Carry Look-Ahead Addierwerk (1)

• Für eine schnelle Addition ist RCA mit einer maximalen

Verzögerung von 2n ungeeignet.

Gibt es auch eine schnellere Möglichkeit, zwei n-Bit Zahlen zu addieren?

• Idee: Ersetzung des sequentiellen Übertragdurchlaufs durch eine

parallele Vorausberechnung aller Überträge ci.

• Ansatz: Betrachte i-ten Volladdierer eines RCA.

Es gilt: ci = ai bi + (ai + bi) ci–1 Gi + Pi ci–1

„Generate“: Gi = ai bi gibt an, ob in Stelle i ein Übertrag erzeugt wird.

„Propagate“: Pi = ai + bi gibt an, ob in Stelle i ein Übertrag propagiert wird (Pi

= 1) oder nicht (Pi = 0).

Einführung in die Technische Informatik - WS 11/12

Arithmetik

13

Carry Look-Ahead Addierwerk (2)

• Für die Überträge ci ergibt sich somit:

c0 = a0b0 G0

c1 = a1b1 + (a1 + b1)c0 G1 + P1G0

c2 = G2 + P2G1 + P2P1G0

c3 = G3 + P3G2 + P3P2G1 + P3P2P1G0

c4 = G4 + P4G3 + P4P3G2 + P4P3P2G1 + P4P3P2P1G0

c5 = ...

• Verzögerung

Zur Bestimmung aller Pi und Gi :

Zur Bestimmung aller Signale ci bei gegebenen Pi und Gi : 2

Jedoch werden zur Bestimmung von ci mehrere große UND-Gatter mit max. i + 1

Eingängen und ein großes ODER-Gatter mit i + 1 Eingängen benötigt.

Annahme eines einheitlichen ist unrealistisch!

Einführung in die Technische Informatik - WS 11/12

Arithmetik

14

Carry Look-Ahead Addierwerk (3)

• Aufbau eines Carry Look-Ahead Addierers (CLA) für n = 4 Bit:

hier mit Pi = ai bi

anstatt Pi = ai + bi

Einführung in die Technische Informatik - WS 11/12

Arithmetik

15

Carry Look-Ahead Addierwerk (4)

• Ein vollständiger n-Bit CLA benötigt zur Addition zweier n-Bit

Zahlen die Zeit 5τ (unabhängig von n)!

• Probleme des vollständigen n-Bit CLA

Hoher Aufwand für große n

Gatter mit bis zu n + 1 Eingängen erforderlich.

Hoher „fan-in“

Gatterausgänge Pi und Gi sind mit bis zu (n +1)2 / 4 Gattereingängen

verschaltet.

Hoher „fan-out“

Vollständiger CLA ist nicht praktikabel !

• Kombination von RCA und CLA als Alternative:

Einführung in die Technische Informatik - WS 11/12

Arithmetik

16

Subtraktion (1)

• Statt der Entwicklung eines eigenen Subtrahierwerkes kann bei

Verwendung des Zweierkomplements jedes Addierwerk auch zur

Subtraktion verwendet werden.

• Ansatz: a – b = a + (–b)

• Realisierung für zwei n-stellige Zahlen a und b:

Invertierung aller Bits bi

Addition von 1 zur Bildung des Zweierkomplements –b

Kann z.B. in den zuvor besprochenen Addierwerken durch Setzen von cin = 1 ohne

zusätzlichen Hardwareaufwand erreicht werden!

Addition von a und (b)

Summe ist korrekt, wenn Überlaufbit cn–1 ignoriert wird.

• Überlauf v tritt nur dann ein, wenn gilt: cn–1 cn–2

Einführung in die Technische Informatik - WS 11/12

Arithmetik

17

Subtraktion (2)

• Realisierung eines n-Bit Addier-/Subtrahierwerkes

• Addition a + b bei S = 0, Subtraktion a – b bei S = 1

• Invertieren der Bits bi bei S = 1 durch XOR-Gatter

• Intern ist jedes beliebige n-Bit Addierwerk verwendbar!

Einführung in die Technische Informatik - WS 11/12

Arithmetik

18

Subtraktion (3)

• Einige Beispiele zur Addition von im Zweierkomplement kodierten

positiven und negativen 8-Bit Zahlen:

Einführung in die Technische Informatik - WS 11/12

Arithmetik

19

Subtraktion (4)

•

Drei Fälle bei der Addition im Zweierkomplement:

1) Zahlen a und b positiv (d.h. an-1= bn-1= 0)

Überlauf bei sn-1 = 1 (tritt auf bei cn-1 = 0, cn-2 = 1)

2) Zahlen a und b negativ (d.h. an-1= bn-1= 1)

nun sind a´= a und b´= b positiv, somit gilt:

sum = a + b = (2n – a´) + (2n – b´) = 2 2n – (a´+ b´)

korrektes Ergebnis wäre jedoch: s = 2n – (a´+ b´) = sum – 2n

erforderliche Korrektur: Überlaufbit cn-1 ignorieren

Überlauf bei sn-1 = 0 (tritt auf bei cn-1 = 1, cn-2 = 0)

3) Vorzeichen von a und b unterschiedlich (b sei negativ):

sum = a + b = a + (2n – b´) = 2n – (b´ a) ist korrekt für |b| > |a|, korrektes

Ergebnis für |b| < |a| wäre jedoch: s = a b´ = sum – 2n

erforderliche Korrektur: Überlaufbit cn-1 ignorieren

kein Überlauf möglich!

Einführung in die Technische Informatik - WS 11/12

Arithmetik

20

ALU (1)

• ALU = Arithmetic Logic Unit

• Realisiert die Elementaroperationen eines Rechners (arithmetische

Operationen wie Addition und Subtraktion als auch logische

Operationen wie AND und OR).

• Aus zwei Eingangswerten X und Y wird ein Ergebniswert Z gebildet.

X, Y und Z sind meist Register.

Typische Registerbreiten sind 8, 16, 32, 64 Bits.

Dementsprechend spricht man von 8-, 16-, 32- und 64-Bit-Rechner.

• Bei der Ausführung von Operationen können bestimmte

Zusatzinformationen anfallen.

Deshalb gibt es noch ein Flag-Register, in dem entsprechende Bits gesetzt

werden, wenn bei der ausgeführten Operation ein entsprechendes Ergebnis

aufgetreten ist.

Einführung in die Technische Informatik - WS 11/12

Arithmetik

21

ALU (2)

Einführung in die Technische Informatik - WS 11/12

Arithmetik

22

ALU (3)

• s2 unterscheidet zwischen arithmetischen und logischen

Operationen bzw. zwischen Konstanten 0 und 1.

• s1 und s0 wählen konkrete Operation (arithmetisch bzw. logisch).

Einführung in die Technische Informatik - WS 11/12

Arithmetik

23

Schaltungsrealisierung einer n-Bit-ALU

Einführung in die Technische Informatik - WS 11/12

Arithmetik

24

MULTIPLIKATION

Einführung in die Technische Informatik - WS 11/12

Arithmetik

25

Multiplikation (1)

• Algorithmus zur Multiplikation zweier positiver Binärzahlen a und

b entspricht der handschriftlichen Multiplikation zweier positiver

Dezimalzahlen.

• Produkt p zweier positiver n-Bit Binärzahlen hat 2n Bitstellen.

• Algorithmus ist zurückführbar auf wiederholte bedingte

Additionen und Schiebeoperationen.

Einführung in die Technische Informatik - WS 11/12

Arithmetik

26

Multiplikation (2)

• Modifizierter

Algorithmus:

• Beispiel für n = 5 (vgl.

letzte Folie):

• In der 2n-Bit Variablen p

werden n partielle

Produkte addiert.

• Rechtsschieben von p

ersetzt das Linksschieben

von a.

Einführung in die Technische Informatik - WS 11/12

Arithmetik

27

Multiplizierwerke (1)

• Implementierung A: Serielles Schaltwerk

Direkte Umsetzung des modifizierten Algorithmus in digitaler Logik

Bedingte Addition mittels UND

Steuerwerk muss Signale erzeugen:

clear p: setze p = 0

shift right: schiebe b um eine Position nach rechts

load and shift right: schiebe p um eine Position nach rechts und

lade p2n-1 ... pn parallel

• Zur Berechnung von p sind n Taktzyklen erforderlich!

Einführung in die Technische Informatik - WS 11/12

Arithmetik

28

Multiplizierwerke (2)

• Implementierung B: Feldmultiplizierer („array multiplier“)

Direkte Realisierung des handschriftlichen Multiplikationsschemas für

Binärzahlen a und b in digitaler Logik.

Es werden zunächst alle Bitprodukte aj bi ermittelt.

Für jedes Multiplikatorbit bi wird hieraus ein partielles Produkt qi = (an–1bi

an–2bi ... a1bi a0bi)2 = a bi gebildet.

Die n partiellen Produkte qi werden jeweils um i Bitpositionen nach links

verschoben und aufaddiert.

Beispiel für n = 4:

Einführung in die Technische Informatik - WS 11/12

Arithmetik

29

Multiplizierwerke (3)

• Einfache Implementierung mittels Multipliziererzellen aus jeweils

einem Volladdierer und einem UND-Gatter:

• Maximale Zeit zur Multiplikation zweier 4-Bit Zahlen: 21

• Maximale Zeit zur Multiplikation zweier n-Bit Zahlen: (6n – 3)

Einführung in die Technische Informatik - WS 11/12

Arithmetik

30

Multiplizierwerke (4)

• Implementierung C: CSA-Kette / CSA-Baum

Zur Bildung des Produktes p zweier n-Bit Zahlen müssen n partielle Produkte

qi = a bi aufaddiert werden.

Zur schnellen Addition vieler Zahlen bieten sich Carry Save Addierer (CSA)

an, bei denen entstehende Überträge erst bei der Addition des nächsten

Summanden berücksichtigt werden.

Ein m-Bit CSA-Baustein ermöglicht eine partielle Addition von drei m-Bit

Zahlen.

Für eine Addition von k Zahlen werden k – 2 CSA-Bausteine benötigt.

Ein zusätzlicher RCA oder CLA dient der Addition der am Ende noch

verbleibenden Überträge.

Einführung in die Technische Informatik - WS 11/12

Arithmetik

31

Multiplizierwerke (5)

• Beispiel: 4-Bit CSA zur Addition von fünf 4-Bit Zahlen u, v, w, x, y

Einführung in die Technische Informatik - WS 11/12

Arithmetik

32

Multiplizierwerke (6)

• Zur Addition der n partiellen

Produkte qi = a bi werden n–2

schnelle CSA-Addierer benötigt.

• Anordnung der Addierer z.B. als

CSA-Kette, hier für n = 6.

• In jeder Stufe sind einige Bits des

Produkts p berechnet.

• Zeit zur Multiplikation zweier n-Bit

Zahlen: (2n – 3) + tAdd

• Für einen CLA gilt z.B. tAdd = 5

• Weitere Beschleunigung durch

Anordnung als CSA-Baum.

Einführung in die Technische Informatik - WS 11/12

Arithmetik

33

Multiplizierwerke (7)

• Implementierung D: Zweistufiges Schaltnetz

Idee: Realisierung eines n n Bit Multiplizierers als zweistufiges Schaltnetz

mit 2n Eingängen und 2n Ausgängen.

Sehr geringe Zeitverzögerung: nur 2.

Implementierung z.B. durch ein ROM oder PROM mit 22n Zeilen aus 2n-Bit

Worten.

Jedoch sehr hoher Speicheraufwand:

n

Produkt

2n

Zeilen

22n

PROM

Größe

2

4

16

64 Bit

4

8

256

256 Byte

8

16

65536

128 KByte

16

32

4.3 109

1.6 GByte

Einführung in die Technische Informatik - WS 11/12

Arithmetik

34

Multiplikation negativer Zahlen (1)

• Bislang Betrachtung ausschließlich positiver Multiplikatoren und

Multiplikanden.

• Was passiert bei negativen im Zweierkomplement kodierten n-Bit

Multiplikatoren bzw. n-Bit Multiplikanden?

a (– b) = a (2n – b) = a 2n – a b

(– a) b = (2n – a) b = b 2n – a b

(– a) (– b) = (2n – a) (2n – b) = 22n – a 2n – b 2n + a b

(statt 22n – a b)

(statt 22n – a b)

(statt a b)

• Ohne besondere Maßnahme liefert binärer Multiplizierer falsche

Ergebnisse!

• Jedoch aufwendige Addition von Korrekturtermen möglich.

Man addiert Term um auf das gewünschte Ergebnis zu kommen.

• Alternative: Trennung von Vorzeichen und Betrag.

Hoher Aufwand für Umwandlung von Zahlen vor/nach der Multiplikation.

Einführung in die Technische Informatik - WS 11/12

Arithmetik

35

Multiplikation negativer Zahlen (2)

• Idee: Vereinfachung der Multiplikation, wenn Multiplikator eine 1Folge repräsentiert: a 111 = a 1000 – a 0001

Auch innerhalb längerer Bitfolgen möglich.

z.B. a 0011100 = a 0100000 – a 0000100

Multiplikation mit einer 1-Folge lässt sich stets durch eine Addition und eine

Subtraktion ersetzen.

• Der Algorithmus nach Booth analysiert zwei benachbarte Bits bi

und bi–1 des Multiplikators:

(bibi–1)2 = 012 : Addition von a 2i

(bibi–1)2 = 102 : Subtraktion von a 2i

(bibi–1)2 = 002 oder (bibi–1)2 = 112 : keine Addition

• Ergänzung von b–1 = 0 erforderlich.

Einführung in die Technische Informatik - WS 11/12

Arithmetik

36

Multiplikation negativer Zahlen (3)

• Realisierung der Subtraktion von a 2i durch Addition des

Zweierkomplements (vorzeichenrichtig ergänzt).

• Beispiele (mit n = 5):

• Funktioniert für beliebige positive und negative Multiplikanden

und Multiplikatoren!

Einführung in die Technische Informatik - WS 11/12

Arithmetik

37

DIVISION

Einführung in die Technische Informatik - WS 11/12

Arithmetik

38

Division (1)

• Umkehrung der Multiplikation: Berechnung von q = a / b durch

wiederholte bedingte Subtraktionen und Schiebeoperationen.

• In jedem Schritt wird Divisor b testweise vom Dividenden a

subtrahiert: qi = 1, falls a – b > 0

qi = 0 und Korrektur durch a = a + b, falls a – b < 0

• Dieses Verfahren wird auch als „Restoring“- Division bezeichnet.

• Allgemein gilt: Dividend / Divisor = Quotient + Rest / Divisor bzw.:

Dividend = Divisor Quotient + Rest

Einführung in die Technische Informatik - WS 11/12

Arithmetik

39

Division (2)

• Beispiel: 2910 / 510 = 510 mit Rest 410

Einführung in die Technische Informatik - WS 11/12

Arithmetik

40

Division (3)

• Aufgabenstellung hier: n-Bit Dividend a, n-Bit Divisor b

Ergebnis: n-Bit Quotient q, n-Bit Rest r

• Es wird intern eine 2n-Bit Variable q = (q2n-1,...,q0) verwendet.

• Algorithmus zur Restoring-Division (für positive Zahlen a und b).

(q2n-1,...,qn) = 0, (qn-1,...,q0) = a

for i=0 to n-1 {

shift left q by 1

(q2n-1,...,qn) = (q2n-1,...,qn) - b

if (q2n-1 == 0)

q0 = 1

else {

q0 = 0

(q2n-1,...,qn)=(q2n-1,...,qn) + b

}

}

• Variable q enthält dann nach n Schritten sowohl den Rest r in den

Bits 2n – 1, ... , n als auch den Quotienten in Bits n –1, ... , 0.

Einführung in die Technische Informatik - WS 11/12

Arithmetik

41

Dividierwerk

• Direkte Implementierung

in digitaler Logik

ergibt serielles Dividierwerk:

• Steuerwerk muss entsprechende Signale generieren:

load q:

add/sub:

lade q mit Dividenden a in (qn–1,...,q0)

addiere/subtrahiere b zu/von (q2n–1,...,qn)

in Abhängigkeit von q2n-1

shift left: schiebe q um eine Stelle nach links

• Effizientere Dividierwerke arbeiten ohne Korrektur („NonRestoring“) und bestimmen je Schritt mehrere Quotientenbits.

Einführung in die Technische Informatik - WS 11/12

Arithmetik

42

FEST- UND GLEITKOMMAZAHLEN

Einführung in die Technische Informatik - WS 11/12

Arithmetik

43

Fest- und Gleitkommazahlen

• Sollen rationale oder reelle Zahlen auf einem Rechner bearbeitet

werden, so hat der Rechnerarchitekt oder Programmierer zwei

Möglichkeiten zur Auswahl:

• Festkommazahlen

Jede Kommazahl z wird durch Skalierung auf ganze Zahl z' abgebildet;

Rechner arbeitet nur auf ganzer Zahl.

• Gleitkommazahlen

Darstellung der Kommazahl durch Mantisse und Exponent; spezielle

Rechenwerke erforderlich!

Einführung in die Technische Informatik - WS 11/12

Arithmetik

44

Festkommazahlen (Wiederholung)

• Zahl zur Basis b mit einer festen Zahl von k Nachkommastellen:

z

= (zn– k–1 zn– k–2 ... z1 z0 , z–1 z–2 ... z–k+1 z–k )b

= zn– k–1 bn– k–1 + zn– k–2 bn– k–2 + ... + b1 z1 + b0 z0

n k 1

+ b–1 z–1 + b2 z2 + ... + bk +1 zk +1 + bk zk zi b i

i k

Die Ziffern zn– k–1 zn– k–2 ... z1 z0 stellen den ganzzahligen Teil, die Ziffern z1

z2 ... zk stellen den gebrochenen Teil von z dar.

Die feste Kommaposition k kennt nur der Anwender, der Rechner arbeitet

mit skalierten ganzen Binärzahlen z´ = z 2k.

• Beispiel: Ein 8-Bit Register enthält die Binärzahl z´ = 01101110; für

k = 3 gilt: z = 01101,1102 = 23 + 22 + 20 + 2–1 +2–2 = 13,7510.

• Alle bislang betrachteten Rechenwerke sind somit auch für

Operationen auf Festkommazahlen geeignet!

Einführung in die Technische Informatik - WS 11/12

Arithmetik

45

Gleitkommazahlen (Wiederholung)

• In vielen technischen und wissenschaftlichen Anwendungen wird

bei Zahlen eine große Dynamik benötigt.

Sehr kleine und sehr große Zahlen sollen einheitlich dargestellt werden.

Dies wird möglich durch die Verwendung von Gleitkommazahlen.

• Allgemeine Gleitkommazahl zur Basis r („radix“) ist definiert durch

x = a re mit:

Argument oder Mantisse a

Exponent oder Charakteristik e

• Eine Gleitkommazahl zur Basis r heißt normalisiert, wenn für die

Mantisse a gilt: 1 a < r.

• Beispiele (für r = 10):

Die Zahl 0,0000002345 kann dargestellt werden als 2,345 10–7.

Die Zahl 1024500000,0 kann dargestellt werden als 1,0245 109.

Einführung in die Technische Informatik - WS 11/12

Arithmetik

46

Gleitkommazahlen (Wiederholung)

• Eine binäre Gleitkommazahl x ist definiert durch x = a 2e

mit m-stelliger Mantisse a

und p-stelligem Exponent e

• Eine binäre Gleitkommazahl x 0 heißt normalisiert, wenn für die

Mantisse a gilt: 1 a < 2

• Häufig Darstellung des Exponenten mit Bias b: x = a 2eb

Wahl von b = 2 p–1 – 1 bewirkt Transformation des Bereiches für den

Exponenten e von 0 ... 2 p – 1 in –(2p–1 –1) ... 2p–1.

einfache Kodierung positiver und negativer Exponenten!

• Früher unterschiedliches Gleitkommaformat in jedem Prozessor,

heute überwiegend Verwendung des IEEE 754 Standard.

Einführung in die Technische Informatik - WS 11/12

Arithmetik

47

IEEE 754 Standard (1)

• Allgemeine Definition: x = (–1)s 1.f 2e–b

• Mantisse aus Vorzeichen s und normalisiertem Betrag a = 1.f im

Bereich 1.00..00 bis 1.11..11

1 vor dem Komma wird jedoch nicht kodiert erhöhte Präzision

• Aufbau einer n-Bit IEEE Gleitkommazahl:

p-stelliger Exponent mit Bias b = 2p–1–1, gültiger Exponent e nur im Bereich

emin= 0 e emax = 2p–1 = 2b+1

Darstellbarer Zahlenbereich: 21–b ... (2–2–m) 2b

Zwischen 2e–b und 2eb+1 gibt es stets 2m Gleitkommazahlen:

Abstand benachbarter Gleitkommazahlen ist abhängig von e.

Einführung in die Technische Informatik - WS 11/12

Arithmetik

48

IEEE 754 Standard (2)

• Drei verschiedene Formate spezifiziert:

single precision

double precision

quad precision

n

32

64

128

m

23

52

112

s

1

1

1

p

8

11

15

emin

0

0

0

emax

255

2047

32767

b

127

1023

16383

| xmin |

2–126 10–38

2–1022 10–308

2–16382 10–4932

| xmax | (2–2–23)2127 1038 (2–2–52)21023 10308

Einführung in die Technische Informatik - WS 11/12

Arithmetik

(2–2–112)216383 104932

49

IEEE 754 Standard (3)

• e = emin = (00..00)2 = 0 und e = emax = (11..11)2 werden zur

Kodierung besonderer Zahlen verwendet:

x = +0 („positive Zero“): e = 0, f = 0, s = 0

x = 0 („negative Zero“): e = 0, f = 0, s = 1

x = + („positive Infinity“): e = emax , f = 0, s = 0

x = („negative Infinity“): e = emax , f = 0, s = 1

x = NaN („Not a Number“): e = emax , f 0, s beliebig

x = (–1)s 0.f 21b („Denormalized Number“): e = 0, f 0

• Denormalisierte Gleitkommazahlen ermöglichen die Darstellung

sehr kleiner Werte im Bereich 21bm ... 21b.

Einführung in die Technische Informatik - WS 11/12

Arithmetik

50

IEEE 754 Standard (4)

• Behandlung von Ausnahmesituationen:

Überlauf tritt ein, wenn nach Normalisierung für x gilt: e emax

Generierung von + , falls x > 0

Generierung von , falls x < 0

Einige Rechenregeln für :

+ x (falls x ), x (falls x ),

x / 0 (falls x 0), x (falls x 0)

Einige Operationen liefern ein unbestimmtes Ergebnis, z.B.:

0 NaN, 0 / 0 NaN, NaN,

Ferner gilt für alle Operationen: f (x, NaN) NaN

Unterlauf tritt ein, wenn nach Normalisierung für x gilt: e = 0

Generierung von x = 0 („flushing to zero“)

Generierung einer denormalisierten Darstellung von x

Einführung in die Technische Informatik - WS 11/12

Arithmetik

51

Gleitkomma-Multiplikation

• Algorithmus zur Multiplikation zweier IEEE-Gleitkommazahlen

x = (–1)s a 2bias und y = (–1)t b 2–bias :

1) Multipliziere Mantissen als Festkommazahlen: c = a b

a = 1.fa und b = 1.fb haben m + 1 Stellen c hat 2m + 2 Stellen!

2) Addiere Exponenten: = + – bias

3) Berechne Vorzeichen des Produktes: u = s t

4) Normalisiere Ergebnis: z = (–1)u c 2-bias

a) Falls c 2, schiebe c um 1 nach rechts und inkrementiere .

b) Setze c = 1.fc = 1.(c2m–1 c2m–2 ... cm)2 mit Rundung.

5) Behandlung von Ausnahmesituationen:

a) Überlauf, falls emax = 2p – 1 z := (abhängig von u).

b) Unterlauf, falls emin = 0 Denormalisierung durchführen!

c) Zero, falls c = 0 z := 0 (abhängig von u).

Einführung in die Technische Informatik - WS 11/12

Arithmetik

52

Gleitkomma-Addition (1)

• Algorithmus zur Addition zweier IEEE-Gleitkommazahlen

x = (–1)s a 2bias und y = (–1)t b 2bias :

1) Sortiere x und y, so dass x die Zahl mit kleinerem Exponenten ist.

2) Anpassung der Exponenten: Bestimme x´ = (– 1)s a´ 2bias

durch Rechtsschieben von a um Bitpositionen.

3) Addiere Mantissen:

a) Falls nötig, bilde Zweierkomplement von a´ oder b.

b) Führe Festkomma-Addition c = a´ + b aus.

c) Falls c 0, setze u = 1 und bilde Zweierkomplement von c.

4) Normalisiere Ergebnis: z = (– 1)u c 2–bias

a) Falls c 2, schiebe c nach rechts und inkrementiere .

b) Falls c 1, schiebe c nach links und dekrementiere .

ggf. wiederhole b), bis 1 c 2.

5) Behandlung von Ausnahmesituationen: Überlauf, Unterlauf, c = 0

Einführung in die Technische Informatik - WS 11/12

Arithmetik

53

Gleitkomma-Addition (2)

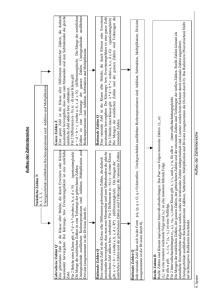

• Möglicher Aufbau eines Gleitkomma-Addierwerks:

Einführung in die Technische Informatik - WS 11/12

Arithmetik

54