Rechnerarchitektur und Rechnertechnik

Werbung

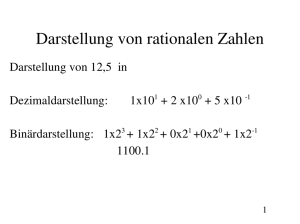

Computerarithmetik (1)

Fragen:

• Wie werden Zahlen repräsentiert und konvertiert?

• Wie werden negative Zahlen und Brüche repräsentiert?

• Wie werden die Grundrechenarten ausgeführt?

• Was ist, wenn das Ergebnis einer Operation größer ist als die größte darzustellende

Zahl?

Hauptunterschied zwischen Computer- und menschlicher Arithmetik:

• Genauigkeit der sowie Platzbedarf für die Darstellung von Zahlen sind beim Computer

endlich und begrenzt.

• Computer arbeiten mit einer anderen Zahlendarstellung

Rechner speichern die Information (Zahlen) in Einheiten festgesetzter Bitlänge,

genannt Worte.

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (2)

Mikroprozessor

Wortlänge (Bits

8085, Z80, 6809

8

8086, 68000

16

80386, 68020

32

Pentium, PowerPC

(Sun SPARC, IBM AIX)

32

typischer Mikrocontroller

(4), 8, 16, (32)

Cray-1 Supercomputer,

Intel Itanium, AMD Opteron

64

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (3)

Beispiel: Rechnung mit Menge aller dreistelligen positiven Zahlen

Zahlenbereich: 000, 001, ... 998, 999

•

•

•

•

600 + 600 = 1200

002 − 005 = −2

050 ⋅ 800 = 2500

Ergebnis zu groß, Überlauf

Ergebnis zu klein, Unterlauf

Ergebnis zu groß, Überlauf

Folglich: bei Zahlen mit endlicher Genauigkeit gilt die Abgeschlossenheit nicht

Aus Sicht der klassischen Mathematik können Ergebnisse entstehen, die falsch sind

Allerdings werden sie völlig korrekt vom Rechner ermittelt

Ursache: endliche Natur des Gerätes

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (4)

Beispiel: Assoziativgesetz

Zahlenbereich: 000, 001, ... 998, 999

•

Reihenfolge der Berechnung hängt ab, ob von rechts nach links oder links nach rechts

ausgewertet wird

𝑎+ 𝑏−𝑐 = 𝑎+𝑏 −𝑐

700 + 400 − 300 = 700 + 400 − 300

700 + 100 = 1100 − 300

800 = ?

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

mit a = 700, b = 400, c = 300

Ergebnis zu groß, Überlauf

T. Ihme

Computerarithmetik (5)

Beispiel: Distributivgesetz

Zahlenbereich: 000, 001, ... 998, 999

•

Obwohl mathematisch gleichwertig, hängt das Einhalten des Zahlenbereiches von der

konkreten Umsetzung der Rechnung ab

𝑎⋅ 𝑏−𝑐 =𝑎⋅𝑏−𝑎⋅𝑐

5 ⋅ 210 − 192 = 5 ⋅ 210 − 5 ⋅ 192

5 ⋅ 18 = 1050 − 960

90 = ?

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

mit 𝑎 = 5, 𝑏 = 210, 𝑐 = 192

Ergebnis zu groß, Überlauf

T. Ihme

Computerarithmetik (6)

Beispiel für Zahlendarstellung mit unterschiedlichen Basen:

binär

1

1

1

1

1

0

1

0

0

0

1

1 • 210 + 1 • 29 + 1 • 28 + 1 • 27 + 1 • 26 + 0 • 25 + 1 • 24 + 0 • 23 + 0 • 22 + 0 • 21 + 1 • 20

1024 + 512 + 256 + 128 + 64 + 0 + 16 +

0 +

0 +

0 +

1

oktal

3

7

2

1

3

2

1

3 • 8 + 7 • 8 + 2 • 8 + 1 • 80

1536 + 448 + 16 +

1

dezimal

2

0

0

1

3

2

1

2 • 10 + 0 • 10 + 0 • 10 + 1 • 100

2000 +

0 +

0 +

1

hexadezimal

7

D

1

7 • 162 + 13 • 161 + 1 • 160

1792 +

208 +

1

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (7)

Kollektion von Zahlendarstellungen mit den 4 verschiedenen Basen:

dezimal

0

1

2

3

7

8

10

11

12

15

16

20

50

60

80

100

1000

2989

binär

0

1

10

11

111

1000

1010

1011

1100

1111

10000

10100

110010

111100

1010000

1100100

1111101000

101110101101

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

oktal

hexadezimal

0

1

2

3

7

8

A

B

C

F

10

14

32

3C

50

64

3E8

BAD

0

1

2

3

7

10

12

13

14

17

20

24

62

74

120

144

1750

5655

T. Ihme

Computerarithmetik (8)

Beispiel für Konversion einer

Dezimalzahl in eine Binärzahl:

Tabelle für Umwandlung

binär - hexadezimal:

Hexabinär

dezimal

0

1

2

3

4

5

6

7

0000

0001

0010

0011

0100

0101

0110

0111

Hexabinär

dezimal

8

9

a

b

c

d

e

f

1000

1001

1010

1011

1100

1101

1110

1111

Quotient

1492

746

373

186

93

46

23

11

5

2

1

0

Rest

0

0

1

0

1

0

1

1

1

0

1

1 0 1 1 1 0 1 0 1 0 0

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (9)

Beispiel: Umwandlung Dezimal zu Binär

Variante 1: Subtraktion der nächsten passenden Zweierpotenz

1500

476

220

92

28

12

4

-

1024

256

128

64

16

8

4

(210)

(28)

(27)

(26)

(24)

(23)

(22)

=

=

=

=

=

=

=

476

220

92

28

12

4

2

150010 = 101110111002

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (10)

Beispiel: Umwandlung Dezimal zu Binär

Variante 2: Divisionsmethode

1500 : 2 = 750 R

750 : 2 = 375 R

375 : 2 = 187 R

187 : 2 = 93 R

93 : 2 = 46 R

46 : 2 = 23 R

23 : 2 = 11 R

11 : 2 = 5 R

5:2= 2R

2:2= 1R

1:2= 0R

0

0

1

1

1

0

1

1

1

0

1

10111011100

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (11)

Beispiel: Umwandlung Dezimal zu Hexadezimal

Divisionsmethode

1500 : 16 = 93 R 12 → C

93 : 16 = 5 R 13 → D

5 : 16 = 0 R 5 → 5

5 D C 16

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (12)

Beispiel: Umwandlung Binär zu Hexadezimal

Bilden von Tetraden

0101 1101 11002

5

D

C16

Beispiel: Umwandlung Binär zu Oktal

Bildung von Triaden

010 111 011 1002

2 7

3

88

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (13)

Beispiel: Umwandlung Binär zu Dezimal

2

((((( 1 ) 2 + 0) 2 + 1) 2 + 1) 2 + 0)

=2

=5

= 11

= 2210

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (14)

Beispiel: Umwandlung Binär zu Dezimal

8

(((( 2 ) 8 + 7) 8 + 3) 8 + 4)

= 23

= 187

= 150010

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (15)

Beispiel: Umwandlung Binär zu Dezimal

16

((( 5 ) 16 + 13) 16 + 12)

= 93

= 150010

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (16)

BCD (Binary Coded Decimal):

•

•

•

weitere Möglichkeit der Zahlendarstellung auf der Basis von 2 Ziffern

Es wird mit 4 Binärstellen jeweils eine Dezimalstelle codiert

Eine reine Binärrechnung führt nicht zum korrekten Ergebnis, wie folgende

Rechnung zeigt:

473910

+ 128710

602610

0100 0111 0011 1001

+ 0001 0010 1000 0111

0101 1001 1100 0000 =59?010

510 910 1210 010

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (17)

BCD (Binary Coded Decimal):

•

Da von den 16 möglichen Binärcodierungen nur 10 genutzt werden, müssen die

nicht genutzten Codes durch eine zusätzliche Korrekturrechnung übersprungen

werden, sobald diese bei der Rechnung erreicht oder übersprungen werden

Bisheriges falsches Ergebnis:

Richtiges Ergebnis 602610

•

0101 1001 1100 0000

0110

0101 1001 1100 0110

1 0110

0101 1010 0010 0110

1 0110

0110 0000 0010 0110

Übertrag

Ungültige BCD-Ziffer

Ungültige BCD-Ziffer

Viele Prozessoren und Mikrocontroller besitzen Spezialbefehle für BCDRechnungen

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (18)

BCD (Binary Coded Decimal):

weitere Möglichkeit der Zahlendarstellung auf der Basis von 2 Ziffern

Prinzip:

Jede Dezimalziffer wird für sich in die entsprechende Binärzahl konvertiert.

Vorteil:

sehr einfache Konvertierung von dezimaler zu binärer Darstellung

Nachteile:

– komplexere Arithmetik

– verschwenderische (ineffiziente) Ausnutzung der zur Verfügung stehenden

Wortbreite und damit des gesamten Speichers

Konsequenz:

Einsatz nur in Applikationen mit sehr geringem Speicherbedarf

Beispiele:

Taschenrechner, Digitaluhr

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (19)

Darstellung ganzer Zahlen (signed numbers)

1. Die Vorzeichen/Betrags - Darstellung (sign and magnitude):

Das höchstgewichtete Bit wird exklusiv für die Angabe des Vorzeichens genutzt.

Sei 𝑆 das Vorzeichenbit und 𝑀 der Betrag (Größe) einer ganzen Zahl 𝑍,

dann ist ihr Wert gegeben durch: 𝑍 ≔ −1 𝑆 ⋅ 𝑀

Der Wertebereich bei einem gegebenen 𝑛-bit-Wort liegt im Intervall

−(2−1 − 1), + 2𝑛−1 − 1

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (20)

Darstellung ganzer Zahlen (signed numbers)

1. Die Vorzeichen/Betrags - Darstellung (sign and magnitude):

Fall

1

2

3

4

Operanden

+x,+y

-x,-y

+x,-y mit x ≥ y oder

Auszuführende Operationen

+(x+y)

Addition

-(x+y)

Addition

Subtraktion

+ ( x − y)

-x,+y mit y ≥ x

+ ( y − x)

+x,-y mit x < y oder

− ( x − y)

-x,+y mit y < x

− ( y − x)

Subtraktion

Nachteile:

–

keine eindeutige Darstellung der Null (-0, +0)

–

erfordert separates Subtrahierwerk

–

erfordert zusätzliche Logik, um zu entscheiden, ob eine Addition oder eine

Subtraktion durchzuführen ist

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (21)

2. Die Komplement - Darstellung

Komplement: „Ergänzung“

Der negative Wert einer Zahl ist in der Zahl selbst enthalten

• Das Vorzeichenbit ist Teil des Summanden und wird somit in eine

arithmetische Operation mit eingeschlossen

• Subtraktion wird auf die Addition zurückgeführt

• Keine Notwendigkeit für ein zusätzliches Subtrahierwerk

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (22)

2a. Einer - Komplement

b-1 - Komplement: 𝑧 + 𝑧𝐸𝐸 = 𝑏 𝑛 − 1 mit 𝑧𝐸𝐾 = −𝑧

𝑛 = Länge der Darstellung von 𝑧

𝑏 = Basis

Das Einer - Komplement −𝑧 = 𝑧𝐸𝐸 einer binären Zahl 𝑧 ∈ 0, 2𝑛−1 − 1 erreicht man

durch bitweises Invertieren von 𝑧

•

•

•

•

𝑧 ∈ 0, 2𝑛−1 − 1

𝑧𝐸𝐸 ∈ − 2𝑛−1 − 1 , 0

𝑧𝐸𝐸 = 2𝑛 − 𝑧 − 1

Der Wertebereich des Zweier - Komplements ist − 2𝑛−1 − 1 , + 2𝑛−1 − 1

Subtraktion:= Addition + end-around-carry, d.h. zu der Summe wird das „linke“ Bit

der Summe aufaddiert.

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (23)

2a. Einer - Komplement

Fall 1: x–y mit x>y

x = +9 = +010012 = 01001

y = −4 = −001002 = 11011

01001 + 11011=1 00100

00100 +1 = 00101 = 510

Das Carry-out ist bei x>y immer 1. x − y = x + (2n − y − 1) = 2n + ( x − y ) − 1 . Dies

ist aber genau x-y, wenn man das Carry-out streicht und den Wert Eins dazuaddiert.

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (24)

2a. Einer - Komplement

Fall 2: x–y mit x<y

x = +4 = +00100 2 = 00100

y = −9 = − 0 1 0 0 12 = 10110

00100+ 0 10110 = 11010

11010+ 0 = 11010 = −00101 = −510

Das Carry-out ist bei x<y immer 0.Wir haben eben gesehen, dass

x − y = 2 n + ( x − y ) − 1 . Wegen x<y ist die rechte Seite negativ, also

− ( x − y ) = 2 n − (2 n − ( x − y ) + 1) − 1 = −( x − y ) . Daraus folgt, dass die Addition ohne

weitere Korrektur immer das richtige Ergebnis ergibt, nachdem man bitweise invertiert hat.

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (25)

2a. Einer - Komplement

Fall 3: Addition zweier negativer Zahlen

x = −4 = − − 00100 2 = 11011

y = −9 = − 0 1 0 0 12 = 10110

11011 + 10110=1 10001

10001+1 = 10010 = −01101 = −1310

Das Carry-out ist bei zwei negativen Zahlen immer 1.

− x + ( − y ) = ( 2 n − x − 1) + ( 2 n − y − 1)

= 2n − 1 + 2n − 1 − ( x + y)

= 2 n − 1 + 2 n − 1 − ( 2 n − ( x + y ) − 1)

= 2n − 1 + 2n − 1 − 2n − ( x + y) − 1

= 2n − ( x + y) − 1

= −( x + y )

Hier hat man die Rechnung auf obigen Fall 1. zurückgeführt, es muss nur noch

invertiert werden.

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (26)

2a. Einer - Komplement

Vorteil:

• zusätzliches Subtrahierwerk überflüssig

Nachteile: • keine eindeutige Darstellung der Null (+0, −0)

• kein echtes Komplement, da −𝑥 + 𝑥 = 0

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (27)

2b. Zweier - Komplement

b - Komplement: 𝑧 + 𝑧𝑍𝐾 = 𝑏 𝑛 mit 𝑧𝑍𝑍 = −𝑧

𝑛 = Länge der Darstellung von 𝑧

𝑏 = Basis

Das Zweier - Komplement ist ein echtes Komplement

I:

𝑧 + 𝑧𝑍𝑍 = 𝑏 𝑛

• 𝑧𝑍𝑍 = 2𝑛 − 𝑧

II:

𝑧 + 𝑧𝐸𝐸 = 𝑏 𝑛 − 1

• 𝑧𝑍𝑍 = 𝑧𝐸𝐸 + 1

I-II:

𝑧𝑍𝑍 = 𝑧𝐸𝐸 + 1

• 𝑧𝑍𝑍 = (bitweises Invertieren von 𝑁) +1

• 𝑧𝑍𝑍 ∈ −2𝑛

• Es gibt eine eindeutige Darstellung der Null

• Der Wertebereich des Zweier - Komplements ist −2𝑛−1 , +2𝑛−1 − 1

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (28)

2b. Zweier - Komplement

1. x–y mit x>y

x = 5 = 0101

y = −3 = 1101 = −(0011 + 1)

0101 + 1101=1 0010 = 2

Wie man sieht, kann man das Carry-out einfach ignorieren, es ist keine Korrekturaddition mehr notwendig.

2. –x–y

x = −3 = 1101

y = −4 = 1100

1101 + 1100 =1 1001 = −7

Auch hier ist die Berücksichtigung des Carry-Out nicht notwendig.

Vorteil:

• zusätzliches Subtrahierwerk überflüssig

• eindeutige Null

• keine Korrekturrecvhnung

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (29)

Visualisierung des Zweier - Komplements sowie der Addition

0000

1111

1110

-1

0001

-2

1101

0010

0 +1

+2

+3

-3

-4

1100

1011

0011

+4

0100

+5

-5

-6

+6

-7 -8 +7

1010

1001 1000

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

0101

0110

0111

T. Ihme

Computerarithmetik (30)

Einfache Additions- (Subtraktions-) Regeln

𝑥 + 𝑦:

Addition der entsprechenden 2er - Komplemente ergibt korrekte Summe im

2er - Komplement, solange der Wertebereich nicht überschritten wird.

𝑥 − 𝑦:

Bilde das 2er - Komplement von y und führe Addition wie oben aus.

Konsequenz:

Die logische Einfachheit und die daraus resultierende Geschwindigkeit (arithm.

Operation erfolgt immer in einem Schritt) führt dazu, dass das Zweier - Komplement in

den ALU´s moderner Rechner eingesetzt wird.

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (31)

Overflow (Summe liegt außerhalb des Wertebereiches):

Wichtig: Erkennung des Overflows

• Bei vorzeichenloser Integer-Addition dient das carry-out-bit als Überlauf-Indikator.

mit der Wortbreite nicht mehr darstellbarer Überrag

• Bei Addition ganzer Zahlen (signed numbers) gilt dies nicht

• Addition von Summanden mit unterschiedlichem Vorzeichen ergibt nie einen

Overflow (Absoluter Wert ihrer Summe ist immer kleiner als der absolute Wert von

einem der beiden Summanden)

Folgerung: Overflow tritt auf, wenn beide Summanden das gleiche Vorzeichen haben

Prüfung auf Overflow:

𝑉 = 𝑎𝑛−1 𝑏𝑛−1 𝑠𝑛−1 + 𝑎𝑛−1 𝑏𝑛−1 𝑠𝑛−1

(Die Faktoren repräsentieren die Vorzeichenbits der Summanden 𝑎 und 𝑏 sowie der

Summe 𝑠)

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (32)

Symbol:

Wahrheitstabelle Halbaddierer:

A

B

S

C

0

0

1

1

0

1

0

1

0

1

1

0

0

0

0

1

𝑆 =𝐴𝐵+𝐴𝐵

(Exklusiv-Oder)

B

1

1

HA

Carry:

𝐶 =𝐴𝐵

Implementierung:

A

&

A

≥1

B

S

≥1

&

&

&

S

1

&

S

&

B

C

1

C

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

Cout

&

A

S

&

&

B

A

Summe:

T. Ihme

C

Computerarithmetik (34)

Wahrheitstabelle Volladdierer:

Cin

A

B

S

Cout

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

1

0

1

0

0

1

0

0

0

1

0

1

1

1

A B Cin

Symbol:

FA

S

Cout

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

Implementierung eines

Volladdierers mittels

zweier Halbaddierer

T. Ihme

Computerarithmetik (35)

Schaltung für einen Volladdierers:

B

A

C

1

1

1

&

&

C

B

&

≥1

&

A

S

&

&

&

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

≥1

C

Computerarithmetik (36)

Serieller Addierer (SA):

A Shift-Register

Summen-Shift-Register

B Shift-Register

A

S

B FA

Cin

Q

Carry

Flip Flop

Shift Takt

Cout

D

C

n Pulse pro Addition

Paralleladdierer (RCA):

A B Cin

A B Cin

A B Cin

A B Cin

Übertrag

1. Ebene

FA

FA

FA

FA

Übertrag

Cout

Sm-1

Cout

Sm-2

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

Cout

S1

Cout

T. Ihme

S0

Computerarithmetik (37)

Implementierung eines 4-Bit-Carry-Lookahead-Addierers

g2 p2

p3

x0 y0

x1y1

x2 y2

x3 y3

g0 p0

g1 p1

c0 / cin

c3

c4

c2

2 GLZ

c1

c4 / cout

FA

FA

FA

FA

s3

s2

s1

s0

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

1 GLZ

T. Ihme

3 GLZ

Computerarithmetik (38)

Implementierung eines 4-Bit-Carry-Lookahead-Addierers

Verkettung mehrerer

Teiladdierer

x31 y31 … x28 y28

x7 y7 … x4 y4

x3 y3 … x0 y0

s31 … s28

s7 … s4

s3 … s0

Resultierende Laufzeit

s0 … s3

…

…

s4 … s7

…

s28 … s31

…

0 1 2 3 4 5 6 7 8

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

15

T. Ihme

17

20

GLZ

Computerarithmetik (39)

Rechenzeit zur Addition zweier 32 Bit-Zahlen

B) Ripple Carry Adder (RCA)

A) Serial Addier

3 GLZ pro Additionsschritt

(Mindestzeit, da Taktung entscheidend)

31 * 2 GLZ (Ripple Carry)

1 * 3 GLZ (letzte Addition)

65 GLZ

32 ⋅ 3 𝐺𝐺𝐺 = 96 𝐺𝐺𝐺

C) 4-Bit Carry-Lookahead Adder (CLA)

= 62 GLZ

= 3 GLZ

D) hierarchical Carry-Lookahead Adder

Zusammenschaltung von 8 4-Bit CLA

CLA mit 8x 4-Bit CLA

1 ⋅ 1 𝐺𝐺𝐺 (𝑔𝑖 𝑢𝑢𝑢 𝑝𝑖)

8 ⋅ 2 𝐺𝐺𝐺 (𝑐1 … 𝑐4)

1 ⋅ 3 𝐺𝐺𝐺 letzte Addition

1 * 1 GLZ (gi und pi)

1 * 2 GLZ (Gi und Pi)

2 * 2 GLZ (C1 ... C4)

1 * 2 GLZ (c31)

1 * 3 GLZ (letzte Addition)

= 1 𝐺𝐺𝐺

= 16 𝐺𝐺𝐺

= 3 𝐺𝐺𝐺

20 𝐺𝐺𝐺

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

=

=

=

=

=

1 GLZ

2 GLZ

4 GLZ

2 GLZ

3 GLZ

12 GLZ

T. Ihme

Computerarithmetik (40)

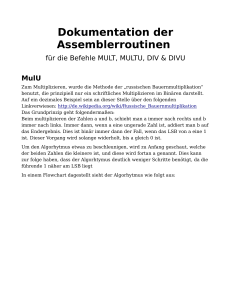

Multiplikation

1. Version einer Multiplikationshardware:

64 Bit Multiplikand

64-Bit ALU

Linksshift

Kontroll Test

Write

64 Bit Produkt

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

32 Bit Multiplikator

T. Ihme

Rechtsshift

Computerarithmetik (41)

Dazugehöriger Algorithmus:

Start

Nein

1. Test

Multiplikator = 0?

Ja

1a. Addiere den Multiplikand zum Produkt speichere das

Ergebnis im Produktregister

2. Das Multiplikandenregister um 1 Bit nach links shiften

3. Das Multiplikatorregister um 1 Bit nach rechts shiften

32. Wiederholung?

Nein

Ja

Stop

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (42)

Dazugehöriges Beispiel:

Schleife

Schritt

0

Anfangswerte

1

1a: 1 Produkt += Multiplikator

2: Shifte Multiplikand nach links

3: Shifte Multiplikator nach rechts

2

1a: 1 Produkt += Multiplikator

2: Shifte Multiplikand nach links

3: Shifte Multiplikator nach rechts

3

1: 0 Keine Operation nötig

2: Shifte Multiplikand nach links

3: Shifte Multiplikator nach rechts

4

1: 0 Keine Operation nötig

2: Shifte Multiplikand nach links

3: Shifte Multiplikator nach rechts

Multiplikator Multiplikand

0011

0000 0010

0011

0000 0010

0011

0000 0100

0001

0000 0100

0001

0000 0100

0001

0000 1000

0000

0000 1000

0000

0000 1000

0000

0001 0000

0000

0001 0000

0000

0001 0000

0000

0010 0000

0000

0010 0000

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Produkt

0000 0000

0000 0010

0000 0010

0000 0010

0000 0110

0000 0110

0000 0110

0000 0110

0000 0110

0000 0110

0000 0110

0000 0110

0000 0110

Computerarithmetik (43)

2. Version einer Multiplikationshardware:

32 Bit Multiplikand

32 Bit Multiplikator

32-Bit ALU

Kontroll Test

Write

64 Bit Produkt

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

Rechtsshift

T. Ihme

Rechtsshift

Computerarithmetik (44)

Dazugehöriger Algorithmus:

Start

Nein

1. Test

Multiplikator = 0?

Ja

1a. Addiere den Multiplikand auf die linke Hälfte des

Produktes und schreibe das Ergebnis in die linke

Hälfte des Produktregisters

2. Das Produktregister um 1 Bit nach rechts shiften

3. Das Multiplikatorregister um 1 Bit nach rechts shiften

32. Wiederholung?

Nein

Ja

Stop

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (45)

Dazugehöriges Beispiel:

Schleife

Schritt

0

Anfangswerte

1

1a: 1 Produkt += Multiplikand

2: Shifte Produkt nach rechts

3: Shifte Multiplikator nach rechts

2

1a: 1 Produkt += Multiplikand

2: Shifte Produkt nach rechts

3: Shifte Multiplikator nach rechts

3

1: 0 Keine Operation nötig

2: Shifte Produkt nach rechts

3: Shifte Multiplikator nach rechts

4

1: 0 Keine Operation nötig

2: Shifte Produkt nach rechts

3: Shifte Multiplikator nach rechts

Multiplikator Multiplikand

0011

0010

0011

0010

0011

0010

0001

0010

0001

0010

0001

0010

0000

0010

0000

0010

0000

0010

0000

0010

0000

0010

0000

0010

0000

0010

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Produkt

0000 0000

0010 0000

0001 0000

0001 0000

0011 0000

0001 1000

0001 1000

0001 1000

0000 1100

0000 1100

0000 1100

0000 0110

0000 0110

Computerarithmetik (46)

3. Version einer Multiplikationshardware:

32 Bit Multiplikand

32-Bit ALU

Write

64 Bit

Produkt

Kontroll Test

Rechtsshift

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (47)

Dazugehöriger Algorithmus:

Start

Nein

1. Test

Produkt = 0?

Ja

1a. Addiere den Multiplikand auf die linke Hälfte des

Produktes und schreibe das Ergebnis in die linke

Hälfte des Produktregisters

2. Das Produktregister um 1 Bit nach rechts shiften

32. Wiederholung?

Nein

Ja

Stop

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (48)

Dazugehöriges Beispiel:

Schleife

Schritt

0

Anfangswerte

1

1a: 1 Produkt += Multiplikand

2: Shifte Produkt nach rechts

2

1a: 1 Produkt += Multiplikand

2: Shifte Produkt nach rechts

3

1: 0 Keine Operation nötig

2: Shifte Produkt nach rechts

4

1: 0 Keine Operation nötig

2: Shifte Produkt nach rechts

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

Multiplikand

0010

0010

0010

0010

0010

0010

0010

0010

0010

T. Ihme

Produkt

0000 0011

0010 0011

0001 0001

0011 0001

0001 1000

0001 1000

0000 1100

0000 1100

0000 0110

Computerarithmetik (49)

Signed multiplication (Multiplikation mit Vorzeichen)

Prinzip der Multiplikation mit Vorzeichen:

a) Fallunterscheidung entsprechend der Vorzeichen der Faktoren.

+𝑎

(+𝑎)

(−𝑎)

(−𝑎)

·

·

·

·

(+𝑏)

(−𝑏)

(+𝑏)

(−𝑏)

Ergebnis hat positives Vorzeichen

Ergebnis hat negatives Vorzeichen

Ergebnis hat negatives Vorzeichen

Ergebnis hat positives Vorzeichen

b) Nutzung eines Algorithmus, der vorzeichenbehaftete Zahlen verarbeitet

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (50)

Der Booth-Algorithmus

• Darstellung einer Zahl durch eine größere Zahl abzüglich einer Differenz

• Größere Zahl wird so gewählt, dass möglichst wenig Einsen

• Differenz zwischen darzustellender Zahl und größerer Zahl

7

8

-1

0

1

0

+1

1

0

0

0

1 1

0 0

0 -1

0 -1

Merkhilfe:

Zahlen werden von rechts beginnend umcodiert:

• Bei Wechsel von 0 auf 1 schreibe -1 unter die 1

• Bei Wechsel von 1 auf 0 schreibe +1 unter die 0

• Erfolgt kein Wechsel, so schreibe 0

0 0

0 +1

1

0

1

0

1 1

0 –1

0

0

0

0

0 1

+1

„0 +1 = 1“

1 0

-1

„1 -1 = 0“

0 0

0

„0 +0 = 0“

1 1

0

„1 +0 = 1“

(0)

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (51)

Multiplikation mit Vorzeichen

Beispiel für normale Multiplikation:

0

0 0

0 0 0

0 0 0 1

0

1

0

0

0

0

1

0

0

0

1

0

1

0

1

0

0

0

0

0

0

1

0

1

1

0

0

1

1 0 1 1 0 1

0+1+1+1+1 0

0 0 0 0 0 0

0 1 1 0 1

1 1 0 1

1 0 1

0 1

0

0 0 0 1 1 0

Das gleiche Beispiel mit Booth-Algorithmus:

0

1

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

1

0

0

0

1

0

1

0

1

0

0

0

0

0

0

0

1

0

0

0

1

0

1

0

1

0

0

0

1

0

0

0 1

0+1

0 0

0 1

0 0

0 0

0 0

0 1

0

1 0

0

0

0

0

0

0

0

1

0

0

0

0

0

1 0 1

0-1 0

0 0 0

1 1

0

0 0 1 1 0

Beobachtung:

• Es sind wesentlich weniger Teiladditionen notwendig.

• Tatsächliche Anzahl ist nicht bekannt.

• Es können positive und negative Faktoren verarbeitet werden.

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (52)

Vergleich am Beispiel 2 x 6:

0

1

2

3

4

Multiplikand

0010

0010

0010

0010

0010

0010

0010

0010

0010

Ursprünglicher Algorithmus

Schritt

Produkt

Anfangswerte

0000 0110

1: 0 Keine Operation nötig

0000 0110

2: Shifte Produkt nach rechts

0000 0011

1a: 1 Produkt += Multiplikand

0010 0001

2: Shifte Produkt nach rechts

0001 0001

1a: 1 Produkt += Multiplikand

0011 0001

2: Shifte Produkt nach rechts

0001 1000

1: 0 Keine Operation nötig

0001 1000

2: Shifte Produkt nach rechts

0000 1100

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

Booth-Algorithmus

Schritt

Produkt

Anfangswerte

0000 0110 0

1a: 00 keine Operation nötig

0000 0110 0

2: Shifte Produkt nach rechts

0000 0011 0

1c: 10 Produkt –= Multiplikand

1110 0011 0

2: Shifte Produkt nach rechts

1111 0001 1

1d: 11 keine Operation nötig

1111 0001 1

2: Shifte Produkt nach rechts

1111 1000 1

1b: 01 Produkt += Multiplikand

0001 1000 1

2: Shifte Produkt nach rechts

0000 1100 0

T. Ihme

Computerarithmetik (53)

Beispiel 2 x (-3):

Schleife

Schritt

0

Anfangswerte

1

1c: 10 Produkt –= Multiplikand

2: Shifte Produkt nach rechts

2

1b: 01 Produkt += Multiplikand

2: Shifte Produkt nach rechts

3

1c: 10 Produkt –= Multiplikand

2: Shifte Produkt nach rechts

4

1d: 11 keine Operation nötig

2: Shifte Produkt nach rechts

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

Multiplikand

0010

0010

0010

0010

0010

0010

0010

0010

0010

T. Ihme

Produkt

0000 1101 0

1110 1101 0

1111 0110 1

0001 0110 1

0000 1011 0

1110 1011 0

1111 0101 1

1111 0101 1

1111 1010 1

Computerarithmetik (54)

Schnelle Multiplikation

A) Beschleunigung der Berechnung durch Verringerung der Anzahl von Teilprodukten

Bit Pair Recoding

Ausgangspunkt: Codierung nach Booth-Algorithmus

Folgende Bit-Kombinationen treten auf und können umcodiert werden:

+2𝑛 – 𝑛 = +𝑛

+1 -1

0 +1

– 2𝑛 + 𝑛 = −𝑛

-1 +1

0 -1

+2𝑛 + 0 = +2𝑛

+1 0

0 +2

– 2𝑛 + 0 = – 2𝑛

-1 0

0 -2

+0 + 𝑛 = +𝑛

0 +1

0 +1

+0 – 𝑛 = – 𝑛

0

0

0

0

0 -1

0 -1

Ergebnis:

1 Stelle ist stets 0

5 Fallunterscheidungen: +2, +1, 0, -1, -2

somit Halbierung der Summandenanzahl

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

0 + 0 = 0

Verarbeitung:

„2“ entspricht einem Linksschift

Fälle +1, 0, -1 wie bei Booth

T. Ihme

Computerarithmetik (55)

Schnelle Multiplikation

B) Beschleunigung der Berechnung schnelle Addition

Ripple-Carry-Adder:

wn-1 xn-1

FA

0

an

FA

zn+1

zn

yn-1

an-1

FA

zn-1

w1 x1

w0 x0

FA

FA

y1

a1

0

a0

y0

FA

FA

z1

z0

0

Nachteil: Carry-Bit muss durch alle Stellen „durchgereicht“ werden

Dadurch lange Rechenzeit

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (56)

Schnelle Multiplikation

B) Beschleunigung der Berechnung schnelle Addition

Prinzip Carry Save Adder (CSA)

Volladdierer addiert eigentlich 3 Bits , erzeugt 2 Ergebnisbits (S + 2C)

somit Reduzierung der Operanden von 3 auf 2

Vermeidung des „Durchreichens“ des Carry-Bits

Carry-Vektor

wird Summand

1

2

Addition

mit Carry

8

Σ

3

C 8

S 7

C10

n

4

5

…

Carry-Vektor

wird Summand

Σ

C n+1

C 8n

Σ

S 9

C 10

S 11

C 12

Σ

Σ

Ergebnis

C12

n

C12

n+1

6

Beispiel zur Addition

mehrerer Summanden

der Stellen

10

C n+1

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (57)

Schnelle Multiplikation

B) Beschleunigung der Berechnung schnelle Addition

Beispiel für eine Implementierung mit CSA:

wn-1 xn-1 yn-1

carry-save

addition

FA

cn

0

FA

zn+1

zn

w 1 x1

zn-1

FA

s1

c2

FA

s0

c1

FA

FA

z2

z1

z=w+x+y

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

w 0 x0

y1

FA

s2

sn-1

cn-1

FA

y2

x2

w2

T. Ihme

0

z0

y0

Computerarithmetik (58)

Division

a)

Beispiel Schriftliche

Division im Dezimalsystem

274

26

14

13

1

: 13 = 21

b) Beispiel Division im

Binärsystem

Testsubtraktion

Testsubtraktion

Wiederherstellen

Testsubtraktion

Testsubtraktion

Wiederherstellen

Testsubtraktion

Rest

ZK(01101)= 10011

100010010

10011

001000

10011

11011

01101

010000

10011

000111

10011

11010

01101

001110

10011

00001

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

: 01101 = 10101

(>0)

Q= 1

(<0)

Q=

(>0)

Q=

(<0)

Q=

(>0)

Q=

T. Ihme

0

1

0

1

Computerarithmetik (59)

1. Version einer Divisionshardware:

64 Bit Divisor

Rechtsshift

32 Bit Quotient

64-Bit ALU

Linksshift

64 Bit Rest

Schreiben

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

Kontroll Test

T. Ihme

Computerarithmetik (60)

Dazugehöriger Algorithmus:

Start

1. Subtrahiere das Divisorregister vom Restregister und

speichere das Ergebnis im Restregister

Nein

1. Test

Rest < 0?

2a. Linksshift des Quotientenregisters um 1 Bit, setze das

neue rechte Bit auf 1

Ja

2b. Restauriere den ursprünglichen Wert durch Addition

des Divisorregisters zum Restregister und speichere das

Ergebnis im Restregister. Shifte dann das

Quotientenregister nach links um 1 Bit und setze das

neue rechte Bit auf 0.

3. Shifte das Divisorregister 1 Bit nach rechts

33. Wiederholung?

Nein

Ja

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (61)

Dazugehöriges Beispiel:

Schleife

Schritt

0

Anfangswerte

1

1: Rest –= Divisor

2b: wenn Rest < 0 +Divisor

Shifte Quotient nach links, Q0=0

3: Shifte Divisor nach rechts

2

1: Rest –= Divisor

2b: wenn Rest < 0 +Divisor

Shifte Quotient nach links, Q0=0

3: Shifte Divisor nach rechts

3

1: Rest –= Divisor

2b: wenn Rest < 0 +Divisor

Shifte Quotient nach links, Q0=0

3: Shifte Divisor nach rechts

4

1: Rest –= Divisor

2a: wenn Rest = 0

Shifte Quotient nach links, Q0=1

3: Shifte Divisor nach rechts

5

1: Rest –= Divisor

2a: wenn Rest = 0

Shifte Quotient nach links, Q0=1

3: Shifte Divisor nach rechts

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

Quotient

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0001

0001

0001

0011

0011

Divisor

0010 0000

0010 0000

0010 0000

0001 0000

0001 0000

0001 0000

0000 1000

0000 1000

0000 1000

0000 0100

0000 0100

0000 0100

0000 0010

0000 0010

0000 0010

0000 0001

T. Ihme

Rest

0000 0111

1110 0111

0000 0111

0000 0111

1111 0111

0000 0111

0000 0111

1111 1111

0000 0111

0000 0111

0000 0011

0000 0011

0000 0011

0000 0001

0000 0001

0000 0001

Computerarithmetik (62)

Dazugehöriges Beispiel:

Schleife

Schritt

0

Anfangswerte

1

1: Rest –= Divisor

2b: wenn Rest < 0 +Divisor

Shifte Quotient nach links, Q0=0

3: Shifte Divisor nach rechts

2

1: Rest –= Divisor

2b: wenn Rest < 0 +Divisor

Shifte Quotient nach links, Q0=0

3: Shifte Divisor nach rechts

3

1: Rest –= Divisor

2b: wenn Rest < 0 +Divisor

Shifte Quotient nach links, Q0=0

3: Shifte Divisor nach rechts

4

1: Rest –= Divisor

2a: wenn Rest ≥ 0

Shifte Quotient nach links, Q0=1

3: Shifte Divisor nach rechts

5

1: Rest –= Divisor

2a: wenn Rest ≥ 0

Shifte Quotient nach links, Q0=1

3: Shifte Divisor nach rechts

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

Quotient

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0001

0001

0001

0011

0011

Divisor

0010 0000

0010 0000

0010 0000

0001 0000

0001 0000

0001 0000

0000 1000

0000 1000

0000 1000

0000 0100

0000 0100

0000 0100

0000 0010

0000 0010

0000 0010

0000 0001

T. Ihme

Rest

0000 0111

1110 0111

0000 0111

0000 0111

1111 0111

0000 0111

0000 0111

1111 1111

0000 0111

0000 0111

0000 0011

0000 0011

0000 0011

0000 0001

0000 0001

0000 0001

Computerarithmetik (63)

2. Version einer Divisionshardware:

32 Bit Divisor

Linksshift

32 Bit Quotient

32-Bit ALU

64 Bit Rest

Linksshift

Schreiben

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

Kontroll Test

T. Ihme

Computerarithmetik (64)

3. Version einer Divisionshardware:

32 Bit Divisor

32-Bit ALU

64 Bit Rest

Links-/Rechtsshift

Schreiben

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

Kontroll Test

T. Ihme

Computerarithmetik (65)

Start

Dazugehöriger

Algorithmus:

1. Das Restregister um 1 Bit nach links shiften

2. Subtrahiere das Divisorregister von der linken Hälfte

des Restregisters und speichere das Ergebnis in der

linken Hälfte des Restregisters

3. Test

Rest < 0?

Nein

3a. Linksshift des Restregisters um 1 Bit, setze das neue

rechte Bit auf 1

Ja

3b. Restauriere den ursprünglichen Wert durch Addition

des Divisorregisters zur linken Hälfte des Restregisters

und speichere das Ergebnis in der linken Hälfte des

Restregisters. Shifte dann das Restregister nach links um

1 Bit und setze das neue rechte Bit auf 0.

31. Wiederholung?

Nein

Ja

Shifte die linke Hälfte des Restregisters 1 Bit nach rechts

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (66)

Dazugehöriges Beispiel:

Schleife

0

Schritt

Anfangswerte

Rest nach links shiften

1

2: Rest –= Divisor

3b: wenn Rest < 0 +Divisor

Shifte Rest nach links, R0=0

2

2: Rest –= Divisor

3b: wenn Rest < 0 +Divisor

Shifte Rest nach links, R0=0

3

2: Rest –= Divisor

3b: wenn Rest ≥ 0

Shifte Rest nach links, R0=1

4

2: Rest –= Divisor

3b: wenn Rest ≥ 0

Shifte Rest nach links, R0=1

5

Shifte linke Hälfte des Restes nach links

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

Divisor

0010

0010

0010

0010

0010

0010

0010

0010

0010

0010

0010

Rest

0000 0111

0000 1110

1110 1110

0001 1100

1111 1100

0011 1000

0001 1000

0011 0001

0001 0001

0010 0011

0001 0011

T. Ihme

Computerarithmetik (67)

Nichtwiederherstellender (non restoring) Algorithmus zur Division:

Prinzip: Ersetze 𝑟 + 𝑑 ⋅ 2 − 𝑑 durch 2𝑟 + 𝑑 auf Basis folgender Überlegung:

•

•

Falls Ergebnis der Testsubtraktion negativ, also 𝑟 − 𝑑 < 0, erfolgt eine

Wiederherstellung des ursprünglichen Restes durch Addition von 𝑑, daraus

ergibt sich

𝑟+𝑑

Bei Übergang zur nächsten Stelle erfolgt Verschiebung des Restes eine Stelle

nach links, das entspricht einer Multiplikation mit 2

𝑟+𝑑 ⋅2

•

Nun erfolgt die nächste Testsubtraktion

•

𝑟+𝑑 ⋅2−𝑑

•

Vereinfachung:

𝑟 + 𝑑 ⋅ 2 − 𝑑 = 2𝑟 + 2𝑑 − 𝑑 = 2𝑟 + 𝑑

Folglich kann die Wiederherstellung mit folgender Testsubtraktion durch eine

Testaddition in der nächsten Stelle mit 𝑟 + 𝑑 ersetzt werden

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (68)

Beispiel zum nichtwiederherstellenden Algorithmus zur Division:

ZK(01101)= 10011

Testsubtraktion

Testsubtraktion

Testaddition

Testsubtraktion

Testaddition

Rest

100010010

10011

001000

10011

110110

01101

0000111

10011

110100

01101

00001

: 01101 = 10101

(>0)

Q= 1

(<0)

Q=

(>0)

Q=

(<0)

Q=

(>0)

Q=

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

0

1

0

1

T. Ihme

Computerarithmetik (69)

Kriterien für die Qualität der Zahlendarstellung:

• Größe des darstellbaren Zahlenbereichs (range)

• Genauigkeit (precision) der Zahlendarstellung

Diese beiden Kriterien sind prinzipiell unabhängig voneinander.

Wissenschaftliche Notation: 𝑛 = 𝑎 ⋅ 𝑟𝐸

𝑎 - Mantisse (Argument)

𝑟 - Radix (Basis)

𝐸 - Exponent (Charakteristik)

Floating point - Zahlen in normierter Form:

𝑛 = −1𝑠 ⋅ 𝑎 ⋅ 2𝐸 mit 𝑠 als Vorzeichenbit und 1 ≤ 𝑎 < 2

Parameter für mögliche Darstellungen von Floating point - Zahlen:

• Anzahl der insgesamt verfügbaren Bits (Worte)

• jeweils für Mantisse bzw. Exponent:

– Darstellung

– Anzahl der verfügbaren Bits (Trade-off!)

– Lokalisierung

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (70)

Darstellung im IEEE Standard 754:

32 Bits

Einfache Genauigkeit:

S

Vorzeichen

der Zahl

0 = “+”

1 = “-”

M

E’

23 Bit Mantisse

8 Bit vorzeichenbehafteter

Exponent

Excess-127

Darstellung

±1,M · 2

Darstellung entspricht:

Beispiel mit

Einfacher Genauigkeit:

E’-127

0 00101000 001010…

Darstellung entspricht: 1,001010...0 · 2

64 Bits

Doppelte Genauigkeit:

S

Vorzeichen 11 Bit

Excess-1023

Exponent

Darstellung entspricht:

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

M

E’

52 Bit Mantisse

±1,M · 2

T. Ihme

E’-1023

-87

Computerarithmetik (71)

Truncation: Kappung überzähliger Bits durch

• chopping

• von Neuman - Runden

• runden

Kappung überzähliger Bits - Chopping

Prinzip

• Abschneiden der zu rundenden Stellen

Beispiel: 0, b1 b2 b3 b4 b5 b6 Rundung auf 3 Nachkommastellen

0, b1 b2 b3 b4 b5 b6 0, b1 b2 b3

Fehler:

• Zwischen 0 ≤ e < 1 der letzten verbleibenden Stelle (hier b3)

• unsymmetrischer Fehler

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (72)

Kappung überzähliger Bits – Von-Neumann-Runden

Prinzip

• Wenn zu rundende Stellen ungleich 0 letzte verbleibende Stelle = 1

• Wenn alle zu rundende Stellen gleich 0 letzte verbleibende Stelle = 0

Beispiel: 0, b1 b2 b3 b4 b5 b6 Rundung auf 3 Nachkommastellen

a) 0, b1 b2 b3 1 0 1 0, b1 b2 1

b) 0, b1 b2 b3 0 0 0 0, b1 b2 0

Fehler

• -1 < e < +1 der letzten verbleibenden Stelle, (hier b3)

• symmetrischer Fehler

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (73)

Kappung überzähliger Bits – Runden

Prinzip

• Unverzerrte oder mathematische Rundung

• Runden zur nächstgelegenen gekürzten Darstellung

• Falls eindeutige Bestimmung der nächstgelegenen gekürzten Darstellung

nicht möglich, d.h. erste zu rundende Stelle = 1 und alle anderen zu

rundenden Stellen = 0 Runden zur nächsten „geraden“ Zahl

Beispiel: 0, b1 b2 b3 b4 b5 b6 Rundung auf 3 Nachkommastellen

a) 0, b1 b2 b3 1 0 1 0, b1 b2 b3 + 0, 0 0 1

0, b1 b2 b3 0 1 1 0, b1 b2 b3

b) 0, b1 b2 b3 1 0 0 Fallunterscheidung

b1) falls b3 = 0 0, b1 b2 0

b2) falls b3 = 1 0, b1 b2 1 + 0, 0 0 1

Fehler:

• -0,5 < e < +0,5 der letzten verbleibenden Stelle (hier b3)

• symmetrischer Fehler

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Wiederholung Mathematik 4. Klasse:

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (74)

Verallgemeinerter Additions/Subtraktions - Algorithmus:

• Rechtsshift auf der Mantisse des kleineren Operanden zur Angleichung der

Exponenten

• Exponent der Summe/Differenz := Exponent des größten Operanden

• Addition/Subtraktion der Mantissen und Bestimmung des Vorzeichens

• Wenn nötig, Normalisierung des Ergebnisses

Verallgemeinerter Multiplikations/Divisions- Algorithmus:

• Addiere/Subtrahiere die Exponenten und subtrahiere/addiere 12710

• Multipliziere/Dividiere die Mantissen und bestimme das Vorzeichen

• Wenn nötig, normalisiere das Ergebnis

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme

Computerarithmetik (75)

Beispiel für die HW - Implementierung einer Addition/Subtraktion:

32 Bit Operanden

A: SA , E’A , MA

B: SB , E’B , MB

{

E’A

}

MA

E’B

8 Bit

Subtrahierer

Vorzeichen

SA SB

Vertauscher

n = [E’A - E’ B]

Addition /

Subtraktion

Addition

Subtraktion

kombinatorisches

SteuerungsNetzwerk

E’A

MB

Vorzeichen

Schieberegister

n Bit nach rechts

M von Zahlen

mit kleinerem E’

M von Zahlen

mit größerem E’

Mantisse

add. / sub.

E’B

Größe M

VornullenErkennung

Multiplexer

X

E’

Normalisieren

und Runden

8 Bit

Subtrahierer

E’ - X

{

R:

SR

E’R

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

MR

}

T. Ihme

32 Bit Ergebnis:

R=A+B

Computerarithmetik (76)

Zusammenfassung:

•

Computerarithmetik ist endlich und kann folglich nicht übereinstimmen mit der

natürlichen Arithmetik

•

Selbst der IEEE 754 - Standard für die floating point - Darstellung, wie jede andere

auch, ist fast immer eine Approximation der realen Zahlen.

•

Rechnersysteme müssen dafür sorgen, den daraus resultierenden Unterschied

zwischen Computerarithmetik und Arithmetik in der realen Welt möglichst zu

minimieren, so etwa im einzelnen durch folgende Techniken:

– Carry-lookahead - Techniken für Addierer mit hoher Performanz

– Für schnelle Multiplizierer: Booth-Algorithmus und Bit-pair recoding zur

Reduzierung der Anzahl der benötigten Operationen für die Erzeugung des

Produkts, Carry-save - Addition zur nochmaligen substantiellen Reduzierung auf

letztlich zwei zu addierende Summanden nach der carry-lookahead - Technik.

•

Programmierer sollten sich dieser Zusammenhänge bewusst sein.

Vorlesung Rechnerarchitektur und Rechnertechnik WS 2017

T. Ihme