Computerarithmetik

Werbung

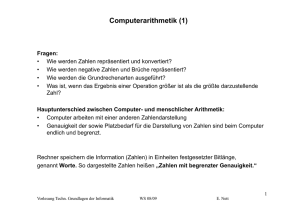

Computerarithmetik (1)

Fragen:

• Wie werden Zahlen repräsentiert und konvertiert?

• Wie werden negative Zahlen und Brüche repräsentiert?

• Wie werden die Grundrechenarten ausgeführt?

• Was ist, wenn das Ergebnis einer Operation größer ist als die größte darzustellende

Zahl?

Hauptunterschied zwischen Computer- und menschlicher Arithmetik:

• Genauigkeit der sowie Platzbedarf für die Darstellung von Zahlen sind beim Computer

endlich und begrenzt.

• Computer arbeiten mit einer anderen Zahlendarstellung

Rechner speichern die Information (Zahlen) in Einheiten festgesetzter Bitlänge,

genannt Worte.

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (1a)

Mikroprozessor

Wortlänge (Bits

8085, Z80, 6809

8

8086, 68000

16

80386, 68020

32

Pentium, PowerPC

(Sun SPARC, IBM AIX)

32

typischer Mikrocontroller

4

Cray-1 Supercomputer

64

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (2)

Beispiel für Zahlendarstellung mit unterschiedlichen Basen:

binär

1

1

1

1

1

0

1

0

0

0

1

1 • 210 + 1 • 29 + 1 • 28 + 1 • 27 + 1 • 26 + 1 • 25 + 1 • 24 + 1 • 23 + 1 • 22 + 1 • 21 + 1 • 20

1024 + 512 + 256 + 128 + 64 + 0 + 16 +

0 +

0 +

0 +

1

oktal

3

7

2

1

3

2

1

3 • 8 + 7 • 8 + 2 • 8 + 1 • 80

1536 + 448 + 16 +

1

dezimal

2

0

0

1

3

2

1

2 • 10 + 0 • 10 + 0 • 10 + 1 • 100

2000 +

0 +

0 +

1

hexadezimal

7

D

1

7 • 163 + 13 • 162 + 1 • 16 1

1792 +

208 +

1

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (3)

Kollektion von Zahlendarstellungen mit den 4 verschiedenen Basen:

dezimal

0

1

2

3

7

8

10

11

12

15

16

20

50

60

80

100

1000

2989

binär

oktal

hexadezimal

0

1

10

11

111

1000

1010

1011

1100

1111

10000

10100

110010

111100

1010000

11001000

1111101000

101110101101

0

1

2

3

7

10

12

13

14

17

20

24

62

74

120

144

1750

5655

0

1

2

3

7

8

A

B

C

F

10

14

32

3C

50

64

3E8

BAD

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (4)

Beispiel für Konversion einer

Dezimalzahl in eine Binärzahl:

Tabelle für Umwandlung

binär - hexadezimal:

Hexabinär

dezimal

0

1

2

3

4

5

6

7

0000

0001

0010

0011

0100

0101

0110

0111

Quotient

Hexabinär

dezimal

8

9

a

b

c

d

e

f

1492

746

373

186

93

46

23

11

5

2

1

0

1000

1001

1010

1011

1100

1101

1110

1111

Rest

0

0

1

0

1

0

1

1

1

0

1

1 0 1 1 1 0 1 0 1 0 0

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (5)

BCD (Binary Coded Decimal):

weitere Möglichkeit der Zahlendarstellung auf der Basis von 2 Ziffern

Prinzip:

Jede Dezimalziffer wird für sich in die entsprechende Binärzahl konvertiert.

Vorteil:

sehr einfache Konvertierung von dezimaler zu binärer Darstellung

Nachteile:

– komplexere Arithmetik

– verschwenderische (ineffiziente) Ausnutzung der zur Verfügung stehenden

Wortbreite und damit des gesamten Speichers

Konsequenz:

Einsatz nur in Applikationen mit sehr geringem Speicherbedarf

Beispiele:

Taschenrechner, Digitaluhr

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (6)

Darstellung ganzer Zahlen (signed numbers)

1. Die Vorzeichen/Betrags - Darstellung (sign and magnitude):

Das höchstgewichtete Bit wird exklusiv für die Angabe des Vorzeichens genutzt.

Sei S das Vorzeichenbit und M der Betrag (Größe) einer ganzen Zahl Z,

dann ist ihr Wert gegeben durch: Z =: (-1) S M

Der Wertebereich bei einem gegebenen n-bit-Wort liegt im Intervall

[-(2n-1-1), 2n-1 -1]

Nachteile:

– keine eindeutige Darstellung der Null (-0, +0)

– erfordert separates Subtrahierwerk

– erfordert zusätzliche Logik, um zu entscheiden, ob eine Addition oder eine

Subtraktion durchzuführen ist

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (7)

2. Die Komplement - Darstellung

Der negative Wert einer Zahl ist in der Zahl selbst enthalten

• Das Vorzeichenbit ist Teil des Summanden und wird somit in eine

arithmetische Operation mit eingeschlossen

• Subtraktion wird auf die Addition zurückgeführt

• Keine Notwendigkeit für ein zusätzliches Subtrahierwerk

2a.

Einer - Komplement

Das Einer - Komplement -N einer binären Zahl N aus [0 , 2n-1-1] erreicht man durch

bitweises Invertieren von N

---> -N aus [-0, -2n-1-1]

---> -N = 2n - N - 1

Subtraktion:= Addition + end-around-carry, d.h. zu der Summe wird das „linke“ Bit

der Summe aufaddiert.

Vorteil:

zusätzliches Subtrahierwerk überflüssig

Nachteile:

• keine eindeutige Darstellung der Null

• kein echtes Komplement, da -x + x ? 0

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (7b)

2b.

Zweier - Komplement

Das Zweier - Komplement ist ein echtes Komplement

• -N = 2n - N

• -N = Einer - Komplement + 1

• -N = (bitweises Invertieren von N ) + 1

• -N aus [-1, -2n-1]

• Es gibt eine eindeutige Darstellung der Null

• Der Wertebereich des Zweier - Komplements ist [-2n-1, 2n-1-1]

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (8)

Visualisierung des Zweier - Komplements sowie der Addition

0000

1111

1110

-1

0001

-2

1101

0010

0 +1

+2

+3

-3

-4

1100

+4

+6

-6

-7 -8 +7

1010

1001 1000

Vorlesung Techn. Informatik II(1) SS 2001

0100

+5

-5

1011

0011

E. Nett

0111

0101

0110

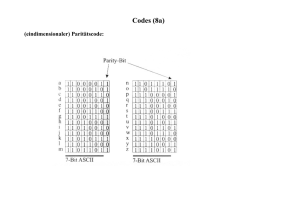

Computerarithmetik (8a)

Einfache Additions (Subtraktions-) Regeln

x+y:

Addition der entsprechenden 2er - Komplemente ergibt korrekte Summe im

2er - Komplement, solange der Wertebereich nicht überschritten wird.

x-y:

Bilde das 2er - Komplement von y und führe Addition wie oben aus.

Konsequenz:

Die logische Einfachheit und die daraus resultierende Geschwindigkeit (arithm.

Operation erfolgt immer in einem Schritt) führt dazu, dass das Zweier - Komplement in

den ALU´s moderner Rechner eingesetzt wird.

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (9)

Overflow (Summe liegt außerhalb des Wertebereiches):

Wichtig: Erkennung des Overflows

• Bei Integer-Addition dient das carry-out-Bit als Overflow-Indikator.

• Bei Addition ganzer Zahlen (signed numbers) gilt dies nicht

• Addition von Summanden mit unterschiedlichem Vorzeichen ergibt nie einen

Overflow (Absoluter Wert ihrer Summe ist immer kleiner als der absolute Wert von

einem der beiden Summanden)

Folgerung: Overflow tritt auf, wenn beide Summanden das gleiche Vorzeichen haben

Prüfung auf Overflow:

O = an−1 bn −1 sn−1 + an−1 bn−1 sn−1

(Die Faktoren repräsentieren die Vorzeichenbits der Summanden

a und b sowie der Summe s)

Gilt O = 1

Es existiert ein Overflow!

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (10)

Symbol:

Wahrheitstabelle Halbaddierer:

A

B

S

C

0

0

1

1

0

1

0

1

0

1

1

0

0

0

0

1

A

Summe:

B

S = AB + AB = A ⊕ B

(Exklusiv-Oder)

HA

Carry:

C = AB

S

Cout

Implementierung:

A

A

A

B

S

B

S

S

C

C

C

Vorlesung Techn. Informatik II(1) SS 2001

B

E. Nett

Computerarithmetik (11)

Wahrheitstabelle Volladdierer:

Cin

A

B

S

Cout

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

1

0

1

0

0

1

0

0

0

1

0

1

1

1

A

B

Cin

HA 1

C1

S1

HA 2

C2

S2

A B Cin

Cout

Symbol:

S

FA

S

Implementierung eines

Volladdierers mittels

zweier Halbaddierer

Cout

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (12)

Schaltung für einen Volladdierers:

A

B

Cin

Cin

A

Cout

B

S

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (13)

Serieller Addierer:

A Shift-Register

Summen-Shift-Register

B Shift-Register

A

S

B FA

C in

Q

Carry

Flip Flop

Shift Takt

Cout

D

C

n Pulse pro Addition

Paralleladdierer:

A B Cin

A B Cin

A B Cin

A B Cin

Übertrag

1. Ebene

FA

FA

FA

FA

Übertrag

Cout

Sm-1

Vorlesung Techn. Informatik II(1) SS 2001

Cout

Sm-2

E. Nett

Cout

S1

Cout

S0

Computerarithmetik (14)

Rohrleitungsanalogie für Carry-lookahead:

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (14a)

Rechenzeit zur Addition zweier 32 Bit-Zahlen

A) serieller Addierer

3 GLZ pro Additionsschritt

(Mindestzeit, da Taktung entscheidend)

32 * 3 GLZ = 96 GLZ

B) Ripple Carry Adder (RCA)

31 * 2 GLZ (Ripple Carry)

1 * 3 GLZ (letzte Addition)

= 62 GLZ

= 3 GLZ

65 GLZ

C) Carry-Lookahead Adder (CLA)

Zusammenschaltung von 8 4-Bit CLA

1 * 1 GLZ (gi und pi)

8 * 2 GLZ (c1 ... C4)

1 * 3 GLZ (letzte Addition)

Vorlesung Techn. Informatik II(1) SS 2001

= 1 GLZ

= 16 GLZ

= 3 GLZ

20 GLZ

E. Nett

Computerarithmetik (15)

Multiplikation

„Multiplication is vexation, Division is as bad.

The rule of three doth puzzle me, And practice drives me mad.“

Anonymus, Elizabethan manuscript, 1570

1. Version einer Multiplikationshardware:

64 Bit Multiplikand

64-Bit ALU

Linksshift

Kontroll Test

Write

32 Bit Multiplikator

64 Bit Produkt

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Rechtsshift

Computerarithmetik (15a)

Dazugehöriger Algorithmus:

Start

Nein

1. Test

Multiplikator = 0?

Ja

1a. Addiere den Multiplikand zum Produkt speichere das

Ergebnis im Produktregister

2. Das Multiplikandenregister um 1 Bit nach links shiften

3. Das Multiplikatorregister um 1 Bit nach rechts shiften

32. Wiederholung?

Ja

Stop

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Nein

Computerarithmetik (15b)

Dazugehöriges Beispiel:

Schleife

Schritt

0

Anfangswerte

1

1a: 1 -> Produkt += Multiplikand

2: Shifte Multiplikand nach links

3: Shifte Multiplikator nach rechts

2

1a: 1 -> Produkt += Multiplikand

2: Shifte Multiplikand nach links

3: Shifte Multiplikator nach rechts

3

1: 0 -> Keine Operation nötig

2: Shifte Multiplikand nach links

3: Shifte Multiplikator nach rechts

4

1: 0 -> Keine Operation nötig

2: Shifte Multiplikand nach links

3: Shifte Multiplikator nach rechts

Vorlesung Techn. Informatik II(1) SS 2001

Multiplikator Multiplikand

0011

0000 0010

0011

0000 0010

0011

0000 0100

0001

0000 0100

0001

0000 0100

0001

0000 1000

0000

0000 1000

0000

0000 1000

0000

0001 0000

0000

0001 0000

0000

0001 0000

0000

0010 0000

0000

0010 0000

E. Nett

Produkt

0000 0000

0000 0010

0000 0010

0000 0010

0000 0110

0000 0110

0000 0110

0000 0110

0000 0110

0000 0110

0000 0110

0000 0110

0000 0110

Computerarithmetik (16)

2. Version einer Multiplikationshardware:

32 Bit Multiplikand

32 Bit Multiplikator

32-Bit ALU

Kontroll Test

Write

64 Bit Produkt

Vorlesung Techn. Informatik II(1) SS 2001

Rechtsshift

E. Nett

Rechtsshift

Computerarithmetik (16a)

Dazugehöriger Algorithmus:

Start

Nein

1. Test

Multiplikator = 0?

Ja

1a. Addiere den Multiplikand auf die linke Hälfte des

Produktes und schreibe das Ergebnis in die linke

Hälfte des Produktregisters

2. Das Produktregister um 1 Bit nach rechts shiften

3. Das Multiplikatorregister um 1 Bit nach rechts shiften

32. Wiederholung?

Ja

Stop

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Nein

Computerarithmetik (17)

Dazugehöriges Beispiel:

Schleife

Schritt

0

Anfangswerte

1

1a: 1 -> Produkt += Multiplikand

2: Shifte Produkt nach rechts

3: Shifte Multiplikator nach rechts

2

1a: 1 -> Produkt += Multiplikand

2: Shifte Produkt nach rechts

3: Shifte Multiplikator nach rechts

3

1: 0 -> Keine Operation nötig

2: Shifte Produkt nach rechts

3: Shifte Multiplikator nach rechts

4

1: 0 -> Keine Operation nötig

2: Shifte Produkt nach rechts

3: Shifte Multiplikator nach rechts

Vorlesung Techn. Informatik II(1) SS 2001

Multiplikator Multiplikand

0011

0010

0011

0010

0011

0010

0001

0010

0001

0010

0001

0010

0000

0010

0000

0010

0000

0010

0000

0010

0000

0010

0000

0010

0000

0010

E. Nett

Produkt

0000 0000

0010 0000

0001 0000

0001 0000

0011 0000

0001 1000

0001 1000

0001 1000

0000 1100

0000 1100

0000 1100

0000 0110

0000 0110

Computerarithmetik (18)

3. Version einer Multiplikationshardware:

32 Bit Multiplikand

32-Bit ALU

Write

64 Bit

Produkt

Kontroll Test

Rechtsshift

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (18a)

Dazugehöriger Algorithmus:

Start

Nein

1. Test

Produkt = 0?

Ja

1a. Addiere den Multiplikand auf die linke Hälfte des

Produktes und schreibe das Ergebnis in die linke

Hälfte des Produktregisters

2. Das Produktregister um 1 Bit nach rechts shiften

32. Wiederholung?

Ja

Stop

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Nein

Computerarithmetik (18b)

Dazugehöriges Beispiel:

Schleife

Schritt

0

Anfangswerte

1

1a: 1 -> Produkt += Multiplikand

2: Shifte Produkt nach rechts

2

1a: 1 -> Produkt += Multiplikand

2: Shifte Produkt nach rechts

3

1: 0 -> Keine Operation nötig

2: Shifte Produkt nach rechts

4

1: 0 -> Keine Operation nötig

2: Shifte Produkt nach rechts

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Multiplikand

0010

0010

0010

0010

0010

0010

0010

0010

0010

Produkt

0000 0011

0010 0011

0001 0001

0011 0001

0001 1000

0001 1000

0000 1100

0000 1100

0000 0110

Computerarithmetik (19)

Signed multiplication (Multiplikation mit Vorzeichen)

Beispiel für normale Multiplikation:

0

0 0

0 0 0

0 0 0 1

0

1

0

0

0

0

1

0

0

0

1

0

1

0

1

0

0

0

0

0

0

1

0

1

1

0

0

1

1 0 1 1 0 1

0+1+1+1+1 0

0 0 0 0 0 0

0 1 1 0 1

1 1 0 1

1 0 1

0 1

0

0 0 0 1 1 0

Das gleiche Beispiel mit Booth-Algorithmus:

0

1

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

1

0

0

0

1

0

1

0

1

0

0

0

0

0

0

0

1

0

0

0

1

0

1

0

1

0

0

0

1

0

0

0 1

0+1

0 0

0 1

0 0

0 0

0 0

0 0

0

1 0

0

0

0

0

0

0

0

1

0

0

0

0

0

1 0 1

0-1 0

0 0 0

1 1

0

0 0 1 1 0

Beobachtung:

• Es sind wesentlich weniger Teiladditionen notwendig.

• Es können positive und negative Faktoren verarbeitet werden.

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (19a)

Der Booth-Algorithmus

Idee:

• Darstellung des Multiplikators durch eine größere Zahl abzüglich einer Differenz

• Größere Zahl wird so gewählt, dass möglichst wenig Einsen, d.h. 2er Potenz

• Größere Zahl und Differenz zum Multiplikator sind neue Multiplikatoren

7

8

-1

0

1

0

+1

1

0

0

0

1 1

0 0

0 -1

0 -1

Zahlen werden von rechts beginnend umcodiert:

• Bei Wechsel von 0 auf 1 schreibe -1 unter die 1

• Bei Wechsel von 1 auf 0 schreibe +1 unter die 0

• Erfolgt kein Wechsel, so schreibe 0

0 0

0 +1

1

0

1

0

1 1

0 –1

Vorlesung Techn. Informatik II(1) SS 2001

0

0

0

0

(0)

E. Nett

0 1

+1

„0 +1 = 1“

1 0

-1

„1 -1 = 0“

0 0

0

„0 +0 = 0“

1 1

0

„1 +0 = 1“

Computerarithmetik (20)

Vergleich am Beispiel 2 x 6:

0

1

2

3

4

Multiplikand

0010

0010

0010

0010

0010

0010

0010

0010

0010

Ursprünglicher Algorithmus

Schritt

Produkt

Anfangswerte

0000 0110

1: 0 -> keine Operation nötig

0000 0110

2: Shifte Produkt nach rechts

0000 0011

1a: 1 -> Produkt +=

0010 0001

Multiplikand

2: Shifte Produkt nach rechts

0001 0001

1a: 1 ->Produkt += Multiplikand

0011 0001

2: Shifte Produkt nach rechts

0001 1000

1: 0 -> Keine Operation nötig

0001 1000

2: Shifte Produkt nach rechts

0000 1100

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Booth-Algorithmus

Schritt

Produkt

Anfangswerte

0000 0110 0

1a: 00 -> keine Operation nötig

0000 0110 0

2: Shifte Produkt nach rechts

0000 0011 0

1c: 10 -> Produkt -= Multiplikand

1110 0011 0

2: Shifte Produkt nach rechts

1111 0001 1

1d: 11 -> keine Operation nötig

1111 0001 1

2: Shifte Produkt nach rechts

1111 1000 1

1b: 01 -> Produkt += Multiplikand

0001 1000 1

2: Shifte Produkt nach rechts

0000 1100 0

Computerarithmetik (20a)

Beispiel 2 x (-3):

Schleife

Schritt

Multiplikand

Produkt

0

Anfangswerte

0010

0000 1101 0

1

1c: 10 -> Produkt -=

Multiplikand

0010

1110 1101 0

2: Shifte Produkt nach rechts

0010

1111 0110 1

1b: 01 -> Produkt +=

Multiplikand

0010

0001 0110 1

2: Shifte Produkt nach rechts

0010

0000 1011 0

1c: 10 -> Produkt -=

Multiplikand

0010

1110 1011 0

2: Shifte Produkt nach rechts

0010

1111 0101 1

0010

1111 0101 1

0010

1111 1010 1

2

3

4

1d: 11

->

keine Operation nötig

2: Shifte Produkt nach rechts

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

1

Computerarithmetik (20b)

Schnelle Multiplikation

A) Beschleunigung der Berechnung durch Verringerung der Anzahl von Teilprodukten

Bit Pair Recoding

Ausgabgspunkt: Codierung nach Booth-Algorithmus

Folgende Bit-Kombinationen treten auf und können umcodiert werden:

+2n –n = +n

+2n +0 = +2n

+1 -1

0 +1

-2n +1 = -n

+1

0

+0 +1 = +1

0 +1

0+0= 0

0

-2n +0 = -2n

-1 +1

0 -1

-1

0

0

+0 -1 = -1

0 -1

Ergebnis:

1 Stelle ist stets 0 ----->somit Halbierung der maximalen Summandenanzahl

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (20c)

Schnelle Multiplikation

B) Beschleunigung der Berechnung schnelle Addition

Ripple-Carry-Adder:

0

an

FA

zn+1

zn

wn-1 x n-1

w1 x1

w0 x 0

FA

FA

FA

yn-1

an-1

FA

z n-1

y1

a1

y0

0

a0

FA

FA

z1

z0

0

Nachteil: Carry-Bit muss durch alle Stellen „durchgereicht“ werden

Dadurch lange Rechenzeit

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (20d)

Schnelle Multiplikation

B) Beschleunigung der Berechnung schnelle Addition

Beispiel für eine Implementierung mit CSA:

wn-1 xn-1 yn-1

carry-save

addition

w1 x1

FA

cn

0

FA

s2

sn-1

cn-1

FA

zn+1

zn

w0 x0

w0 x0

FA

FA

s1

c2

FA

zn-1

E. Nett

s0

c1

FA

FA

z2

z1

z=w+x+y

Vorlesung Techn. Informatik II(1) SS 2001

y 21

0

z0

y0

Computerarithmetik (21)

Division

Beispiel:

13

21

274

26

14

13

1

1101

10101

100010010

1101

10000

1101

1110

1101

1

1. Version einer Divisionshardware:

64 Bit Divisor

Rechtsshift

32 Bit Quotient

64-Bit ALU

Linksshift

64 Bit Rest

Vorlesung Techn. Informatik II(1) SS 2001

Schreiben

E. Nett

Kontroll Test

Computerarithmetik (22)

Dazugehöriger Algorithmus:

Start

1. Subtrahiere das Divisorregister vom Restregister und

speichere das Ergebnis im Restregister

Nein

1. Test

Rest < 0?

2a. Linksshift des Quotientenregisters um 1 Bit, setze das

neue rechte Bit auf 1

Ja

2b. Restauriere den ursprünglichen Wert durch Addition

des Divisorregisters zum Restregister und speichere das

Ergebnis im Restregister. Shifte dann das

Quotientenregister nach links um 1 Bit und setze das

neue rechte Bit auf 0.

3. Shifte das Divisorregister 1 Bit nach rechts

33. Wiederholung?

Ja

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Nein

Computerarithmetik (22a)

Dazugehöriges Beispiel:

Schleife

Schritt

0

Anfangswerte

1

1: Rest -= Divisor

2b: wenn Rest < 0 -> +Divisor

Shifte Quotient nach links, Q0=0

3: Shifte Divisor nach rechts

2

1: Rest -= Divisor

2b: wenn Rest < 0 -> +Divisor

Shifte Quotient nach links, Q0=0

3: Shifte Divisor nach rechts

3

1: Rest -= Divisor

2b: wenn Rest < 0 -> +Divisor

Shifte Quotient nach links, Q0=0

3: Shifte Divisor nach rechts

4

1: Rest -= Divisor

2a: wenn Rest = 0 ->

Shifte Quotient nach links, Q0=1

3: Shifte Divisor nach rechts

5

1: Rest -= Divisor

2a: wenn Rest = 0 ->

Shifte Quotient nach links, Q0=1

3: Shifte Divisor nach rechts

Vorlesung Techn. Informatik II(1) SS 2001

Quotient

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0001

0001

0001

0011

0011

E. Nett

Divisor

0010 0000

0010 0000

0010 0000

0001 0000

0001 0000

0001 0000

0000 1000

0000 1000

0000 1000

0000 0100

0000 0100

0000 0100

0000 0010

0000 0010

0000 0010

0000 0001

Rest

0000 0111

1110 0111

0000 0111

0000 0111

1111 0111

0000 0111

0000 0111

1111 1111

0000 0111

0000 0111

0000 0011

0000 0011

0000 0011

0000 0001

0000 0001

0000 0001

Computerarithmetik (23)

2. Version einer Divisionshardware:

Linksshift

32 Bit Divisor

Linksshift

Linksshift

32 Bit Quotient

32-Bit ALU

64 Bit Rest

Vorlesung Techn. Informatik II(1) SS 2001

Linksshift

Schreiben

E. Nett

Kontroll Test

Computerarithmetik (24)

3. Version einer Divisionshardware:

32 Bit Divisor

Linksshift

32-Bit ALU

64 Bit Rest

Vorlesung Techn. Informatik II(1) SS 2001

Links-/Rechtsshift

Schreiben

E. Nett

Kontroll Test

Computerarithmetik (25)

Start

Dazugehöriger Algorithmus:

1. Das Restregister um 1 Bit nach links shiften

2. Subtrahiere das Divisorregister von der linken Hälfte

des Restregisters und speichere das Ergebnis in der

linken Hälfte des Restregisters

Nein

1. Test

Rest <= 0?

3a. Linksshift des Restregisters um 1 Bit, setze das neue

rechte Bit auf 1

Ja

3b. Restauriere den ursprünglichen Wert durch Addition

des Divisorregisters zur linken Hälfte des Restregisters

und speichere das Ergebnis in der linken Hälfte des

Restregisters. Shifte dann das Restregister nach links um

1 Bit und setze das neue rechte Bit auf 0.

32. Wiederholung?

Nein

Ja

Shifte die linke Hälfte des Restregisters 1 Bit nach rechts

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (25)

Dazugehöriges Beispiel:

Schleife

0

Schritt

Anfangswerte

Rest nach links shiften

1

2: Rest -= Divisor

3b: wenn Rest < 0 -> +Divisor

Shifte Rest nach links, R0= 0

2

2: Rest -= Divisor

3b: wenn Rest < 0 -> +Divisor

Shifte Rest nach links, R0= 0

3

2: Rest -= Divisor

3a: wenn Rest = 0 ->

Shifte Rest nach links, R0= 1

4

2: Rest -= Divisor

3a: wenn Rest < 0 ->

Shifte Rest nach links, R0= 1

5

Shifte linke Hälfte des Restes 1 nach rechts

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Divisor

0010

0010

0010

0010

0010

0010

0010

0010

0010

0010

0010

Rest

0000 0111

0000 111 0

1110 111 0

0001 11 0 0

1111 11 00

0011 1 00 0

0001 1 000

0011 000 1

0001 0001

001 0 001 1

0001 0011

Computerarithmetik (26)

Nichtwiederherstellender (nonrestoring) Algorithmus:

Prinzip: Ersetze (r+d) x 2 - d durch r x 2 + d

Division mit Vorzeichen (signed division):

• Operanden werden mit positiven Vorzeichen dargestellt

• Division wird durchgeführt

• Hatten Operanden unterschiedliche Vorzeichen

– Quotient wird mit negativem Vorzeichen dargestellt

– Vorzeichen des Restes:= Vorzeichen des Dividenden

Kriterien für die Qualität der Zahlendarstellung:

• Größe des darstellbaren Zahlenbereichs (range)

• Genauigkeit (precision) der Zahlendarstellung

Diese beiden Kriterien sind prinzipiell unabhängig voneinander.

Wissenschaftliche Notation: n = a x rE

a Mantisse (Argument), r Radix (Basis), E Exponent (Charakteristik)

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (27)

Floating point - Zahlen in normierter Form:

n = (-1)s x a x 2E mit s als Vorzeichenbit und 1 = a < 2

Parameter für mögliche Darstellungen von Floating point - Zahlen :

• Anzahl der insgesamt verfügbaren Bits (Worte)

• jeweils für Mantisse bzw. Exponent:

– Darstellung

– Anzahl der verfügbaren Bits (Trade-off!)

– Lokalisierung

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (27a)

Darstellung im IEEE Standard 754:

32 Bits

Einfache Genauigkeit:

S

Vorzeichen

der Zahl

0 = “+”

1 = “-”

M

E’

23 Bit Mantisse

8 Bit vorzeichenbehafteter

Exponent

Excess-127

Darstellung

Darstellung entspricht:

Beispiel mit

Einfacher Genauigkeit:

±1,M · 2

E’-127

0 00101000 001010…

-87

Darstellung entspricht: 1,001010...0 · 2

64 Bits

Doppelte Genauigkeit:

S

E’

Vorzeichen 11 Bit

Excess-1023

Exponent

Darstellung entspricht:

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

M

52 Bit Mantisse

±1,M · 2

E’-1023

Computerarithmetik (28)

Truncation: Kappung überzähliger Bits durch

• chopping

• von Neuman - runden

• runden

Verallgemeinerter Additions/Subtraktions - Algorithmus:

• Rechtsshift auf der Mantisse des kleineren Operanden zur Angleichung der

Exponenten

• Exponent der Summe/Differenz := Exponent des größten Operanden

• Addition/Subtraktion der Mantissen und Bestimmung des Vorzeichens

• Wenn nötig, Normalisierung des Ergebnisses

Verallgemeinerter Multiplikations/Divisions- Algorithmus:

• Addiere/Subtrahiere die Exponenten und subtrahiere/addiere 127 10

• Multipliziere/Dividiere die Mantissen und bestimme das Vorzeichen

• Wenn nötig, normalisiere das Ergebnis

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett

Computerarithmetik (29)

Beispiel für die HW - Implementierung einer Addition/Subtraktion:

32 Bit Operanden

A: SA, E’A , M A

B: SB, E’B , MB

{

E’A

}

E’B

MA

8 Bit

Subtrahierer

Vertauscher

Vorzeichen

SA SB

n = [E’A - E’B ]

Addition /

Subtraktion

Addition

Subtraktion

kombinatorisches

SteuerungsNetzwerk

E’A

MB

Vorzeichen

Schieberegister

n Bit nach rechts

M von Zahlen

mit kleinerem E’

M von Zahlen

mit größerem E’

Mantisse

add. / sub.

E’B

Größe M

VornullenErkennung

Multiplexer

X

E’

Normalisieren

und Runden

8 Bit

Subtrahierer

E’ - X

{

R:

SR

E’R

Vorlesung Techn. Informatik II(1) SS 2001

MR

E. Nett

}

32 Bit Ergebnis:

R=A+B

Computerarithmetik (30)

Zusammenfassung:

•

Computerarithmetik ist endlich und kann folglich nicht übereinstimmen mit der

natürlichen Arithmetik

•

Selbst der IEEE 754 - Standard für die floating point - Darstellung, wie jede andere

auch, ist fast immer eine Approximation der realen Zahlen.

•

Rechnersysteme müssen dafür sorgen, den daraus resultierenden Unterschied

zwischen Computerarithmetik und Arithmetik in der realen Welt möglichst zu

minimieren, so etwa im einzelnen durch folgende Techniken:

– Carry-lookahead - Techniken für Addierer mit hoher Performanz

– Für schnelle Multiplizierer: Booth-Algorithmus und Methode des Bit-pairing zur

Reduzierung der Anzahl der benötigten Operationen für die Erzeugung des

Produkts, Carry-save - Addition zur nochmaligen substantiellen Reduzierung auf

letztlich zwei zu addierende Summanden nach der carry-lookahead - Technik.

•

Programmierer sollten sich dieser Zusammenhänge bewußt sein.

Vorlesung Techn. Informatik II(1) SS 2001

E. Nett