Vorlesungsziele

Werbung

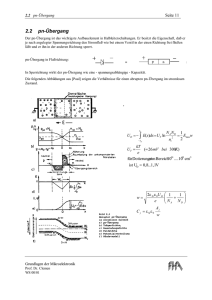

Mikrocomputertechnik Fachbereich Elektrotechnik Prof. Dr. Bayer Systembus Ein Mikroprozessor kommuniziert über den Systembus mit Speicher und I/O Der Ablauf erfolgt in zwei Schritten: o Anlegen von Adressen und Schreib/Lese-Richtung o Schreiben bzw. Lesen der Daten AB R/W DB Benötigt wird daher ein Zeitraster , d.h. ein Takt. Mikrocomputertechnik Fachbereich Elektrotechnik Prof. Dr. Bayer Zeitverhalten Festes Zeitraster : Synchroner Systembus Problem: Beim Anschluß unterschiedlich schneller Bausteine bestimmt der langsamste den Takt des Busses Variables Zeitraster : Asynchroner Systembus Zusätzliche Steuersignale bestimmen das Zeitverhalten Address Strobe : /AS Data Strobe : /DS Data Transfer Acknowledge : /DTACK AB /AS S R/W /DS DB /DTACK variabel (Prozessor) (Prozessor) (Speicher) Mikrocomputertechnik Fachbereich Elektrotechnik Prof. Dr. Bayer Mikrocomputertechnik Fachbereich Elektrotechnik Prof. Dr. Bayer Anschluß von Speicherbausteinen an einen Mikroprozessor Adressbus A0 – A23 Datenbus D0 - D7 Asynchroner Systembus Mikroprozessor: 1. Beispiel: 1 Speicherbaustein 16M x 8 Speicher CPU /DTACK Verz /AS /CS A0-A23 $FFFFFE $FFFFFE $FFFFFD Adressraum (24 Leitungen) Der Adressraum des Prozessors ist vollständig belegt $000002 $000001 $000000 7 0 Mikrocomputertechnik Fachbereich Elektrotechnik Prof. Dr. Bayer 2. Beispiel: 1 Speicherbaustein 4M x 8 Adressraum $C00000 Nur ¼ Adressraum des Prozessors ist belegt $800000 $400000 $000000 7 0 Speicher CPU /DTACK Verz /AS /CS A23 A22 A0-A21 Der Speicherbaustein erscheint 4 mal im Adressraum, er wird gespiegelt Mikrocomputertechnik Fachbereich Elektrotechnik Prof. Dr. Bayer 3. Beispiel: 1 Speicherbaustein 4M x 8 Adressraum $C00000 Nur ¼ Adressraum des Prozessors ist belegt $800000 $400000 $000000 7 0 Speicher CPU /DTACK /AS A23 A22 Verz CSLogik /CS A0-A21 Der Speicherbaustein erscheint nur einmal im Adressraum, wenn /CS nur bei der Kombination A22 = 0 und A23= 0 den Wert 0 hat. /CS = /AS + A23 + A22 Mikrocomputertechnik Fachbereich Elektrotechnik Prof. Dr. Bayer Weitere Kombinationen Speicherbaustein liegt ab der Adresse $400000 im Adressraum $C00000 $400000 = % 01 00 0000 0000 0000 0000 0000 $800000 /CS = /AS + A23 + !A22 $400000 $000000 7 0 Speicherbaustein liegt ab der Adresse $80000 im Adressraum $C00000 $800000 $800000 = % 10 00 0000 0000 0000 0000 0000 $400000 /CS = /AS + !A23 + A22 $000000 7 0 Speicherbaustein liegt ab der Adresse $C00000 im Adressraum $C00000 $C00000 = % 11 00 0000 0000 0000 0000 0000 $800000 /CS = /AS + !A23 + !A22 $400000 $000000 7 0 Mikrocomputertechnik Fachbereich Elektrotechnik Prof. Dr. Bayer Regel: Zur vollständigen Dekodierung einer Bausteinadresse werden alle niederwertigen Adressleitungen zum Baustein geführt, alle restlichen höherwertigen Adressleitungen werden in der ChipSelect-Logik zur Ermittlung des ChipSelect-Signals verwendet. Mikrocomputertechnik Fachbereich Elektrotechnik Prof. Dr. Bayer Bussystem des M68000 16 Bit Datenbus DB0 – DB15 asynchrones Busprotokoll /AS = Addressstrobe /DTACK = Data Transfer Acknowledge 24 Bit Adress-Bus Adressraum 16 Mbyte variable Busbreite d.h. es sind Wortzugriffe mit 16-Bit-Datenwort und Bytezugriffe mit 8-Bit Datenwort möglich (move.b und move.w ) Die Adresse des 68000 bezieht sich auf Byte. D.h. beim wortweisen Zugriff werden zwei Bytes gleichzeitig gelesen. Zum Zugriff auf das nächste Wort muss daher die Adresse um 2 erhöht werden. Realisierung: Statt der Adressleitung A0 verwendet der M68000 zwei DatastrobeLeitungen /UDS = Upper Data Strobe /LDS = Lower Data Strobe Mikrocomputertechnik Fachbereich Elektrotechnik Prof. Dr. Bayer 8Mx8 8Mx8 SA22 SA0 D7 D0 /CS 68000 A23 A1 SA22 SA0 /UDS D7 D0 /CS D15 D8 /LDS D7 D0 Adressleitung A1 – A23 werden mit den Adressleitungen der beiden Speichermodule SA0 – SA22 verbunden. Mit /UDS wird der Speicherblock bei geraden Byte-Adressen aktiviert, mit /LDS der Speicherblock für ungerade ByteAdressen. /UDS und /LDS sind gleichzeitig aktiv bei Wortzugriffen. Beispiele: Zugriff auf 16-Bit Wort MOVE.W #$AABB, $1000 ; /UDS = 0 und /LDS = 0 $1000 $AA $1001 $AABB wird an die Adressen $1000 und $1001 kopiert Zugriff auf gerade Byteadresse MOVE.B #$CC, $1010 ; /UDS = 0 und /LDS = 1 $CC wird an die Adresse $1011 kopiert $1010 $CC $1011 $BB Mikrocomputertechnik Fachbereich Elektrotechnik Prof. Dr. Bayer Zugriff auf ungerade Byteadresse MOVE.B #$CC, $1011 ; /UDS = 1 und /LDS = 0 $DD wird an die Adresse $1011 kopiert $1010 $1011 $DD Mikrocomputertechnik Fachbereich Elektrotechnik Prof. Dr. Bayer Übungsaufgabe: Anschluß von Speicher an den 68000 An einen 68000 Prozessor wird ein 256 KByte SRAM-Speicher angeschlossen, verwendet werden 128KByte Speicherbausteine. Der SRAM-Bereich beginnt bei Adresse $F00000. Wieviele Speicherbausteine sind nötig? Antwort: 2 Skizze: 68000 Decoder SRAM 128Kx8 128Kx8 /LDS /UDS /CS2 /CS /AS A23 D15 D7 A1 D8 D0 SA16 D15 – – SA0 D8 /CS1 A23-A18 A17-A1 Die logischen Gleichungen der Chipselectsignale lauten: /CS1 = !A23 + !A22 + !A21 + !A20 + A19 + A18 + /UDS + /AS /CS2 = !A23 + !A22 + !A21 + !A20 + A19 + A18 + /LDS + /AS /CS SA16 – SA0 D7 D0 Mikrocomputertechnik Fachbereich Elektrotechnik Prof. Dr. Bayer Statt 128Kx8 werden nun 64Kx8 verwendet. Wie sieht nun die Anschlußskizze aus und wie lauten die Gleichungen Benötigt werden nun 4 Bausteine 64Kx8 /CS 64Kx8 /CS /CS4 SA15 D15 – – SA0 D8 SA15 – SA0 D7 D0 Decoder SRAM 68000 /CS4 /LDS 64Kx8 64Kx8 /CS3 /UDS /CS /AS /CS2 A23 D15 D7 A1 D8 D0 SA15 D15 – – SA0 D8 /CS1 A23-A17 A16-A1 Die logischen Gleichungen der Chipselectsignale lauten: /CS1 = !A23 + !A22 + !A21 + !A20 + A19 + A18 + A17 + /UDS + /AS /CS2 = !A23 + !A22 + !A21 + !A20 + A19 + A18 + !A17 + /UDS + /AS /CS3 = !A23 + !A22 + !A21 + !A20 + A19 + A18 + A17 + /LDS + /AS /CS4 = !A23 + !A22 + !A21 + !A20 + A19 + A18 + !A17 + /LDS + /AS /CS /CS3 SA15 – SA0 A16-A1 D7 D0 Mikrocomputertechnik Fachbereich Elektrotechnik Prof. Dr. Bayer Statt 128Kx8 werden nun 128Kx4 verwendet. 68000 Decoder SRAM 128Kx4 128Kx4 128Kx4 128Kx4 /LDS /UDS /CS2 /CS /AS A23 D15 D7 A1 D8 D0 SA16 D15 – – SA0 D12 /CS1 A23-A18 /CS SA16 D11 – – SA0 D8 A17-A1 Die logischen Gleichungen der Chipselectsignale lauten: /CS1 = !A23 + !A22 + !A21 + !A20 + A19 + A18 + /UDS + /AS /CS2 = !A23 + !A22 + !A21 + !A20 + A19 + A18 + /LDS + /AS /CS SA16 D7 – – SA0 D4 /CS SA16 D3 – – SA0 D0