Wozu benötigt man AD/DA Wandler ? Digital-Analog

Werbung

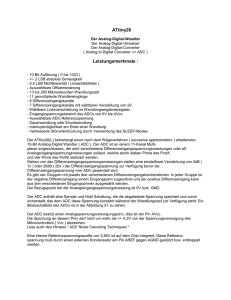

Lehrbehelf für Prozessregelung und Rechnerverbund, 3. Klasse HTL Wozu benötigt man AD/DA Wandler ? In der elektrischen Mess- und Steuerungstechnik werden oft analoge Größen wie Spannung, Widerstand, Leistung, Energie, Temperatur, Gewicht, Länge, Druck, Licht, Schall, Magnetfeld, Drehzahl, usw. gemessen. Die Messdaten werden oft in digitaler Form mit Mikroprozessoren oder Computern gespeichert, weiterverarbeitet, veranschaulicht und übertragen. Analog-Digital-Wandler übersetzen analoge Größen in digitale Zahlenwerte. Digital-Analog-Wandler übersetzen Binärwerte in analoge Strom- oder Spannungssignale, mit denen Motoren, Aktoren, analoge Regler und andere analoge Bauelemente angesteuert werden können. Digital-Analog-Wandler (ADW)= Digital-Analog-Umsetzer (ADU)= DigitalAnalog-Converter (ADC) Digital-Analog-Wandler (DAC) Eine wichtige Größe eines D/A-Wandlers ist die Auflösung. Sie gibt an in wie viel Stufen die maximale Ausgangsspannung untergeteilt werden kann. Je größer die Auflösung, desto genauer kann der digitale Wert in die analoge Ausgangsspannung gewandelt werden. Ua= Z*ULSB Wobei Z= digitaler Wert, Ua= Ausgangsspannung und ULSB= Spannung des Least Significant Bit sind. Beispiel: Ein acht Bit D/A-Wandler kann am Ausgang maximal 10V liefern. Wie groß ist die Auflösung des Wandlers, wie groß ist ULSB ? Lösung: acht Bit entspricht 256 Zahlenwerte von 0-255 (=Zmax), Auflösung=10V / 255=40mV (= ULSB= Spannung des Least Significant Bit) DAC - Parallelverfahren Ein Spannungsteiler teilt die Referenzspannung in verschiedene Ausgangsspannungen. Ein 1-aus-n-Decoder schließt den Schalter, dem die gewünschte Ausgangsspannung zugeordnet ist. Das Parallelverfahren erfordert Zmax Schalter (= teuer), da nur jeweils ein Schalter geschlossen ist. Ua= Uref*Z/ Zmax DA-, AD Converter (DAC/ ADC) 1/ 7 07.04.2003 1 Lehrbehelf für Prozessregelung und Rechnerverbund, 3. Klasse HTL Beispiel: Der nachfolgend gezeigte 3-Bit D/A-Wandler kann am Ausgang maximal 10V liefern. Zmax=7, Z=3 daraus folgt: Uref S7 Ua= 10V*3/ 7= 4,29V 1 aus 8 Ua Decoder Z Ua (V) R (3 to 8) 0 0 S6 1 1,43 2 2,86 3 4,29 4 5,71 5 7,14 6 8,57 7 10,00 R S5 R S4 Digitale Daten R S3 R S2 R R S1 S0 DAC - Wägeverfahren: D/A-Wandlung durch Addition von Teilströmen und der Referenzspannung Uref Jedem Bit der Dualzahl ist ein Schalter zugeordnet. Ist das entsprechende Bit „1“, dann schaltet der Schalter den PIN auf Uref. Wert „9“ bedeutet, dass PIN 1und PIN 8 mit Uref verbunden werden. Über gewichtete Widerstände wird die Ausgangsspannung aufsummiert. R/2 Diese Schaltung besteht aus einem OP, der als Summierverstärker geschaltet ist. Der Summierverstärker besitzt vier Eingänge an denen eine Dualzahl ansteht. Da die Eingänge verschiedene Wertigkeiten haben, müssen die Eingangswiderstände in bestimmten Verhältnissen zueinander stehen. Am Eingang 8, muss der Widerstand am kleinsten sein (R), da die gleiche Spannung am Eingang 8 einen doppelt so DA-, AD Converter (DAC/ ADC) 2/ 7 07.04.2003 2 Lehrbehelf für Prozessregelung und Rechnerverbund, 3. Klasse HTL großen Stromfluss zur Folge haben muss wie am Eingang 4 (2R). Die Widerstände müssen umgekehrt proportional der Wertigkeit der Eingänge sein. Durch den OP wird die Summe der Ströme und die analoge Ausgangsspannung gebildet. Z= digitaler Eingangswert (von 0 bis 15). Für Z=8 gilt: Uref= I* R, Ua= -I* R/ 2, daraus folgt: Ua= -Uref/ 2 Für Z=4 gilt: Uref= I* 2R, Ua= -I* R/ 2, daraus folgt: Ua= -Uref/ 4 Allgemein gilt: Ua= -Uref*Z/24 Vorteil: - Einfacher Aufbau. Nachteil: · Die Widerstände müssen sehr genau sein. · Die Referenzspannungsquelle wird nicht immer gleich belastet (Belastungswiderstand von 8R bis 8/15R) DAC - Wägeverfahren: DAC mit R-2R Leiternetzwerk und Referenzspannung Uref Ein OP ist als Addierer geschaltet. Über ein R-2R Netzwerk wird eine Referenzspannungsquelle in mehrere Spannungen geteilt und zwar immer um die Hälfte. Durch die Gleichheit der 2R Widerstände fließt somit ein Strom, der nach jeder R-2R Stufe auf die Hälfte sinkt. Für Z=8 gilt: Uref= I* 2R, Ua= -I* R, daraus folgt: Ua= -Uref* 2R/ R= -Uref/ 2 Allgemein gilt: Ua= -Uref * Z/ (Zmax+1) 2R R Vorteile: · Die Referenzspannungsquelle wird immer gleich belastet. · Die Schaltung wird nur mit einer Sorte Widerstände aufgebaut und eignet sich daher gut zur Herstellung integrierter Schaltungen. DA-, AD Converter (DAC/ ADC) 3/ 7 07.04.2003 3 Lehrbehelf für Prozessregelung und Rechnerverbund, 3. Klasse HTL 10-Bit DAC 7533 Das R-2R Netzwerk gibt es auch als integriertes Bauelement (z.B. 10-Bit DAC 7533). Ua= -Uref*(Rk/R)*Z/(210) Z= digitale Eingangswert (von 0 bis 1023) Rk=R, Uref= 10V daher: Ua= -10V*Z/210 Analog-Digital-Wandler (ADC) Ein Analog-Digital-Wandler quantisiert analoge Signale. Z= Ue/ ULSB, wobei Z= digitaler Wert, Ue= Eingangsspannung und ULSB= Spannung des Least Significant Bit sind. Je nach geforderter Genauigkeit und Geschwindigkeit und abhängig vom Preis gibt es folgende ADC-Verfahren: ADC - Zählverfahren (level at a time) Es ist nur eine Referenzspannung notwendig, der ADC ist aber langsam (1ms-1s), z.B. für Temperaturmessungen, Digitalvoltmeter. Geringer Schaltungsaufwand. ADC - Kompensationsverfahren - Zählverfahren Die einfachste Form eines ADC besteht aus einem n-Bit Binärzähler, einem DigitalAnalog-Umsetzer, einem Komparator und einem Taktgenerator. Der Taktgenerator gibt seine Impulse über das AND – Gatter, das die Impulse solange zum Binärzähler passieren lässt, wie der Komparator-Ausgang auf +Pegel liegt. Mit jedem Zählimpuls erhöht sich der Zählerstand und damit Spannung UDA am DA-, AD Converter (DAC/ ADC) 4/ 7 07.04.2003 4 Lehrbehelf für Prozessregelung und Rechnerverbund, 3. Klasse HTL Ausgang des DAC treppenförmig (Bild rechter Teil). Erreicht diese Spannung UMESS, so liefert der Komparator ein -Signal und sperrt das AND – Gatter. Der Zählvorgang wird beendet und der Zählerstand entspricht der Analogspannung UMESS. Der Zählvorgang beginnt stets bei Null, die Zeitdauer der Wandlung hängt von der Höhe der anliegenden Spannung ab. ADC - Sägezahn = Rampen = Single Slope Verfahren - Zählverfahren Die Eingangsspannung Ue und die zeitlich kontinuierlich ansteigende Spannung eines Sägezahngenerators Ux werden ständig im Komparator verglichen. Solange das Signal des Sägezahn-Generators kleiner als die Eingangsspannung ist, werden vom Binärzähler die Taktimpulse gezählt, da der Ausgang des Komparators „1“ ist. Die sich daraus ergebende Zeit tM ist proportional zum Eingangssignal Ue. Nach jedem Zählvorgang wird der Zähler auf Null zurückgesetzt. Typischerweise können pro Sekunde ein bis drei Messungen erfolgen. Z= Tau * f * Ue / Uref; Tau= RC (Zeitkonstante des Sägezahns); f= Taktfrequenz Rücksetzen Komparator + Ue - Binärzähler Ux SägezahnGenerator Ue Oszillator Takt 0 Zeit t Zählimpulse T Der Sägezahngenerators kann mit RC-Glied und Transistor realisiert werden. ADC - Wägeverfahren = Successive Approximation (digit at a time) Pro Schritt wird eine Stelle der Dualzahl ermittelt, man beginnt mit dem höchsten Bit MSB (most significant bit). Ein 10-Bit ADC braucht 10 Schritte (unabhängig von der Höhe der Spannung UMESS) und 10 Referenzspannungen. Der Aufbau unterscheidet sich nur wenig vom Single – Slope – Verfahren, jedoch mit effektiverer Ansteuerung des DAC. Die Steuerung setzt zunächst das MSB. Anschließend überprüft der Komparator, ob die für diese Bitkombination vom DigitalAnalog-Umsetzer ausgegebene Spannung kleiner als die Messspannung UMESS. Ist dies der Fall, bleibt das Bit gesetzt, wenn nicht wird es rückgesetzt (=Wägevorgang). Dieser Wägevorgang wird für jedes weitere Bit wiederholt, bis zum Schluss das LSB (least significant bit) feststeht. Z= (Zmax+1)* UMESS / Uref DA-, AD Converter (DAC/ ADC) 5/ 7 07.04.2003 5 Lehrbehelf für Prozessregelung und Rechnerverbund, 3. Klasse HTL 16-Bit ADC AD977 The AD977 is a high speed, low power 16-bit A/D converter that operates from a single 5 V supply. The AD977 throughput rate of 100 kSPS. Each part contains a successive approximation, switched capacitor ADC, an internal 2.5 V reference, and a high speed serial interface. ADC - Parallelverfahren = Flash Verfahren (word at a time) Die Eingangsspannung wird gleichzeitig mit n Referenzspannungen verglichen. Man erhält die Dualzahl in einem Schritt, der ADC ist sehr schnell. Die Ausgangssignale werden dann binär codiert. Für eine Auflösung von n Bits braucht man 2n -1 Komparatoren und 2 n-1 Referenzspannungen. Höhere Auflösungen werden dadurch sehr aufwändig und teuer. Ein 8-Bit ADC braucht 255 Komparatoren und 255 Referenzspannungen. DA-, AD Converter (DAC/ ADC) 6/ 7 07.04.2003 6 Lehrbehelf für Prozessregelung und Rechnerverbund, 3. Klasse HTL Prioritätsdecoder: Am Ausgang tritt eine Dualzahl auf, die der höchsten Eingangsnummer entspricht, an der „1“ anliegt. Die flankengetriggerten D-FF bestimmen den Abtastzeitpunkt. Z= Zmax * UMESS / Uref Uref R/2 X7 D UMESS Q Prioritäts Decoder (74148) C R X6 D C R X5 D Digitale Daten C R D X4 C R X3 D C R D X2 C R X1 D C R/2 Takt 8-Bit ADC MAX100 The MAX100, 250Msps, 8-bit analog-to digital converter (ADC) allows accurate digitizing of analog signals from DC to 125MHz. DA-, AD Converter (DAC/ ADC) 7/ 7 07.04.2003 7