Lektion9 - Nano

Werbung

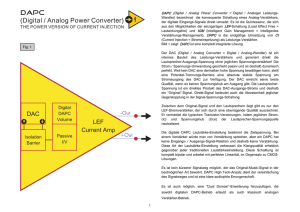

Elektronisch messen, steuern, regeln Digital-Analog-Wandler Analog-Digital-Wandler Abtastung 19.12.01 1 Prinzip des DAC (DAC = Digital - Analog - Converter) 1 2 0 R1 4Bit DAC 12/16 21 R1/ 2 8/16 22 R1/ 4 4/16 23 R1/ 8 Ra U0 Referenzspannung 0 Ua LSB = Least Significant Bit; 19.12.01 20= 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 LSB 21 = 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 22= 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 23= 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 MSB MSB = Most Significant Bit 2 DAC mit R - 2R Leitern R U0 U0/2 R U0/4 R 4Bit DAC U0/8 U0 2R 23 2R 22 2R 21 2R 2R 20 R Referenzspannung 19.12.01 Ua 3 Elektronische Wechselschalter R R 2R Logik Signal LSB = 20 2R 2R 2R 20 Inverter R R 19.12.01 N-Kanal FET's Ua Ua 4 DAC mit Stromquellen 23 U0 21 20 +5V Referenzspannung 10V 22 1/8 mA +1.4V 80k 1/8 mA R Ua 10V -15V 19.12.01 80k 10k 20k 40k 80k 5 Doppel Buffer DAC Mikroprocessor Bus High Byte B15 D7 C15 8 Bit Buffer D0 Ua 16 Bit Buffer DAC Ausgang 8 Bit Buffer B0 Low Byte 19.12.01 C0 Load DAC 6 Bipolar DAC 20 R1 21 R1/ 2 2 R1/ 4 23 R1/ 8 2 Unipolar 2 3 2 2 21 20 Referenzspannung Offset -U0 R1/8 Ra U0 R1 R1 Bipolar Ra Ua U0 Ua Referenzspannung 19.12.01 7 Offset Binär Code Two‘s Complement Code Spannung +7/8V +6/8V +5/8V +4/8V +3/8V +2/8V +1/8V 0/8V -1/8V -2/8V -3/8V -4/8V -5/8V -6/8V -7/8V -8/8V 1 0 -1 19.12.01 Offset Binär 1111 1110 1101 1100 1011 1010 1001 1000 0111 0110 0101 0100 0011 0010 0001 0000 2er Komplement 0111 0110 0101 0100 0011 0010 0001 0000 1111 1110 1101 1100 1011 1010 1001 1000 8 Analog - Digital - Messsystem Eingänge Logik S/H ADC Interface S/H Multiplexer S/H S/H 19.12.01 9 Sample and Hold Schaltung • Logiksignal: Sample • Ue CHold 19.12.01 • Ua • Das Signal am Eingang des ADC‘s darf sich während der Wandlungszeit nicht ändern. Wird der Schalter geschlossen, so lädt sich der Kondensator Chold auf Ue. Beim Öffnen des Schalters bleibt die Ausgangsspannung Ua auf dem letzten Wert von Ue stehen. Nur der Leckstrom des Schalters und der Eingangsstrom des zweiten Verstärkers lassen die Spannung am Chold langsam wegdriften. 10 Paralleler ADC UREF 2Bit Parallel DAC R • Sehr schneller ADC (Konversionszeit = <10 ns) 5/8UREF Bit 1 • Nur sinnvoll bis 8 Bit Auflösung: Aufwand = 256 Komparatoren Bit 0 • Grosser Aufwand: Anzahl Komparatoren = 2(Anzahl Auflösungs-Bit) 7/8UREF UInput R Logik 3/8UREF R 1/8UREF R/2 4 Komparatoren 19.12.01 • Aufwand zur Dekodierung steigt auch sehr rasch mit grösserer Auflösung 11 Prinzip des ADC (ADC = Analog - Digital - Converter) Komparator UInput Logik und Steuerung digitaler Ausgang n Bit DAC Register n Bit 19.12.01 • Das analoge Signal wird mit einem (provisorischen) Wert verglichen. • Der Vergleich liefert je nach Strategie die notwendigen Korrekturen, bis zur möglichst genauen Annäherung an den analogen Wert. 12 Sukzessiv Annäherungstyp Start Konversion • Clock Komparator UInput Logik und Schieberegister • digitaler Ausgang n Bit DAC Status Register n Bit 19.12.01 • • Vom MSB hinab zum LSB wird jedes Bit zuerst probeweise angelegt und das Resultat verglichen mit dem Eingangssignal. Wird der Wert des Eingangssignals beim Test überschritten, so wird das Bit wieder gelöscht, sonst in allen folgenden Tests als gesetzt betrachtet. Die Anzahl der Test = Anzahl Bit‘s z.B.: (12 Tests für 12 Bit Auflösung) 13 Zeitdiagramm SAR 1.00 Signal 0.75 0.50 0.25 0.00 0 1 2 3 4 5 Zeit 19.12.01 6 7 8 9 10 Zeitbereich 0-1: Start 1-2: Test B3=MSB 2-3: B3=0 3-4: Test B2 4-5: B2=1; (B3=0) 5-6: Test B1 6-7: B1=1; (B2=1; B3=0) 7-8: Test B0 =LSB 8-9: B0=0; (B1=1; B2=1; B3=0) 9-10: Ende B3 B2 B1 B0 = 0110 14 Dual Rampen ADC Clock Start Konversion Eingang 2R UIN 2R R Reset R C Status Logik Komparator UREF Integrator Referenzspannung Zähler Ausgang 19.12.01 15 Zeitdiagramm Dual Rampen ADC 1/2 (UIN+UREF) T = UREF T Amplitude T/T = 1/2 (UIN/UREF) + 1/ 2 1/2 (UIN+UREF) T/RC - UREF T/RC Reset Komparator schaltet bei 0V T T Wird die Integrationszeit T gleich der Periodendauer (oder einem ganz-zahligen Vielfachen) der allgegenwärtigen Netzfrequenz gewählt, so werden davon herrührende Störungen unterdrückt! Zeit 19.12.01 16 Abtastung 1 Amplitude Amplitude 1 0 -1 0 -1 0 5 10 15 20 25 0 Zeit Analog, kontinuierlich 19.12.01 5 10 15 20 25 Zeit ADC Digital, zeitdiskret 17 S/H ADC DAC Eingang 1.Filter Nach 2. Filter Nach 1. Filter Nach Abtastung Vor Abtastung Nach Abtastung Abtastung mit Rekonstruktion 2.Filter Ausgang weitere Verarbeitung 19.12.01 18 Signalfrequenz fS = fA * 1 / 25 fA = Abtastfrequenz Amplitude 1 0 Vor Abtastung Nach Abtastung Nach 1.Filter Nach Filter Filter Nach 2.Filter Nach 2.Filter Abtastperiodendauer -1 0 5 10 15 20 25 Zeit 19.12.01 19 Signalfrequenz fS = fA * 1 / 10 Amplitude 1 0 -1 0 5 10 15 20 25 Zeit 19.12.01 20 Signalfrequenz fS = fA * 1 / 5 Amplitude Amplitude 11 00 -1 00 55 10 10 15 20 25 Zeit Zeit 19.12.01 21 Signalfrequenz fS = fA * 1 / 2 Amplitude 1 0 -1 0 5 10 15 20 20 25 25 Zeit 19.12.01 22 Signalfrequenz fS = fA * 24 / 25 Amplitude 1 0 -1 0 5 10 15 20 25 Zeit 19.12.01 23 Signalfrequenz fS = fA * 26 / 25 Amplitude 1 0 -1 0 5 10 15 20 25 Zeit 19.12.01 24 Frequenzfaltung • Amplitude fA = Abtast Frequenz • fA 1 2 fA/2 19.12.01 2fA • • 3 fA Frequenz 2fA • Beim Abtasten werden folgende Frequenzen transformiert und dem Nutzfrequenzband „1“ überlagert: Band „2“ unterhalb fA wird gespiegelt und dem Band „1“ überlagert. Band „3“ oberhalb fA weitere Bänder ober- und unterhalb ganzzahliger Vielfachen von fA. Fazit: Vor der Abtastung sind aus dem Signal alle Frequenzen oberhalb fA/2 zu entfernen. 25 Antialias-Filter Amplitude fA = Abtast Frequenz Antialias Filter fA 1 2 fA/2 19.12.01 2fA 3 fA Frequenz Schneidet ein Antialias Filter alle Frequenzen oberhalb fA/2 vor dem Abtasten weg, so kann die Frequenz-Faltung vermieden werden. 2fA 26 Unter- und Über-Abtastung fA = Abtast Frequenz Amplitude fA 1 2 fA/2 3 Frequenz fA Übertaktverhältnis (over sampling ratio) = fA / fAmin Amplitude fA = Abtast Frequenz 2 1 fAmin/2 19.12.01 fAmin Frequenz 3 fA 27 1 Bit Sigma-Delta (S) ADC Integrator + Eingang S _ R Komparator Digital Filter C Ausgang Dezimations Filter 1Bit DAC Modulator 19.12.01 28 Dezimations Filter Amplitude Amplitude Dezimierungs-Filter Eingang Zeit Ausgang Zeit 19.12.01 Die hohe Abtastrate kann für den Ausgang ohne Informationsverlust wieder reduziert werden. 29 Amplitude S Signalverarbeitung • Analog Eingang fA = Abtast Frequenz Amplitude 5kHz fA = 5MHz Frequenz fA = 5MHz Frequenz fA = 5MHz Digital Filter Quantisierungs-Rauschen 5kHz Amplitude Frequenz Digital Filter Ausgang 5kHz 19.12.01 • Durch die hohe Übertaktrate von 500 = 5MHz/(2*5kHz), wird das hohe Quantisierungsrauschen über das grosse Frequenzband verteilt und damit reduziert. Die Filterung mit digitalen Filtern und die Dezimierung der Ausgabefrequenz ist kostengünstig zu realisieren. 30 Signal / Rausch Verhältnis (S ADC) Signal zu Rausch Verhältnis 200 150 dB Modulator 1.Ordnung 100 2.Ordnung 3.Ordnung 50 0 1 10 100 1000 Übertaktverhältnis (over sampling ratio) 19.12.01 31 Daten heutiger ADC ADC Typ S Sigma Delta SAR Sukzessive Aproximation Auflösung Abtast Rate Bemerkungen (sps= samples per second) 24 48k Dual Channel (Stereo) 16 500k mixed SAR/Flash 8 (parallel) 100M Leistungsaufnahme 120mW Flash (parallel) 750M Leistungsaufnahme 6.25W 19.12.01 8 32