9. Technologische Realisierung (Überblick) 9.1 Elektrotechnische

Werbung

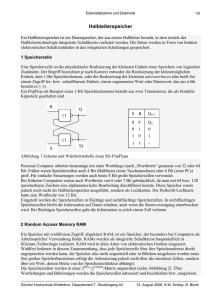

9. Technologische Realisierung (Überblick) Sehr schneller technologischer Wandel. Entwurfsverfahren für Schaltnetze und Schaltwerke weitgehend unabhängig von technologischer Realisierung. Daher hier nur grober Überblick. 9.1 Elektrotechnische Grundlagen Ohmsches Gesetz I U R (Ohmscher) Widerstand + R I U U R *I U I R - U Spannung in Volt [V] I Strom in Ampere [A] R Widerstand in Ohm Beispiel: U = 5V, R = 1k Strom oft in mA (10-3 A) oder µA (10-6 A) Widerstand in k (103 ) oder M (106 ) I U R 5V 1k 5mA Beschreibt den linearen Zusammenhang zwischen Strom und Spannung an einem Widerstand. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9-1 Widerstandsgerade R>0 sinkend I I R=0 R 8 wachsend U R U Gerade mit Steigung 1 , da I 1 U R R Sonderfälle: Kurzschluss: R=0 U=0 Leerlauf: R → I=0 INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9-2 Strom- und Spannungsmessung Multimeter + A - I U R Amperemeter messen den Strom I und werden in Serie zu Widerständen geschaltet. + - V R Voltmeter messen die Spannung U und werden parallel zu Widerständen geschaltet. In der Praxis meist Universal-Messgeräte Auf richtige Polung achten! INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9-3 Spannungsteiler U = U1 + U2 I U2 R2 U R1 R 2 R2 U2 2 R 1 U U 1 R U R U1 U R R1 Ableitbar mit Ohmschen Gesetz: U R I U1 R1 U2 R 2 1 2 2 Durch alle Widerstände fließt der gleiche Strom I R = R1 + R2 (Serienschaltung von Widerständen) Auf mehr als zwei Widerstände verallgemeinerbar! Spannungen verhalten sich im gleichen Verhältnis wie Widerstände. Beispiel: U = 5V, R1= 2k, R2 = 3k => R = 2k + 3k = 5k I = 5V/5k = 1mA U1 = U* R1/R = 5V * 2/5 = 2V, U2 = U* R2/R = 5V * 3/5 = 3V INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9-4 Spannungsteiler mit Widerstandsgeraden I I 5/2 mA R1 R2 5/3 mA R1 U1 R2 U2 U 3V 5V U 2 Gerade für R2 U I 2 R2 U2 = 0 => I = 0 Gerade für R1 U U U2 U U I 1 2 R1 R1 R1 R1 INSTITUT FÜR TECHNISCHE INFORMATIK U2 = U => I = 5V/3k = 5/3mA U2 = 0 => I = 5V/2k = 5/2mA U2 = U => I = 0 Technische Grundlagen der Informatik 9-5 Potentiometer Drehpotentiometer Einstellbarer Spannungsteiler R1 U1 U Trimmpotentiometer P R2 U2 Wird häufig zum Einstellen von Parametern genutzt (z. B. Lautstärkeregler, Helligkeitsregler) INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9-6 9.2 Halbleiterbauelemente Bipolartransistor Bipolarer npn-Transistor in Emitterschaltung kann als Schalter betrieben werden (C: Collektor, B: Basis, E: Emitter). +U Ra +U Symbol eines bipolaren npn- Transistors Ra C C IB UBE = UE T E B IC B IE INSTITUT FÜR TECHNISCHE INFORMATIK U/Ra I 0 E Ua UCE = Ua UE Technische Grundlagen der Informatik 9-7 Schnittbild: n: n-Dotierung p: p-Dotierung Reines Halbleitermaterial (Silizium, Germanium) hat einen temperaturabhängigen Widerstand, der für technische Nutzung wenig geeignet ist. Brechen Valenzelektronen bei der Temperaturerhöhung aus ihrer Bindung, entstehen bewegliche Ladungen in Form von Elektronen (negative Ladungsträger) Defektelektronen oder ‘Löcher‘ (positive Ladungsträger) Durch ‘Dotierung‘, d. h. Einbau von Störstellenatomen, kann man erreichen, dass temperaturunabhängig entweder Elektronenleitung (n-Dotierung) oder Löcherleitung (p-Dotierung) dominiert. Die dominierenden Ladungsträger werden auch als Majoritätsträger, die anderen als Minoritätsträger bezeichnet. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9-8 Bipolartransistor Vom Emitter werden Majoritätsträger in die niedrig dotierte, schmale Basiszone emittiert. Abhängig vom Basisstrom erreichen diese Elektronen den Kollektor und es fließt ein Strom zwischen Emitter und Kollektor. Ist der Basisstrom Null (IB = 0), sperrt die Basis den Emitter-Kollektor-Strom (Transistor sperrt). Fließt ein Basisstrom (IB > 0), fließt auch ein Emitter-Kollektor-Strom (Transistor öffnet). Transistor kann als Verstärker und/oder Schalter betrieben werden. Weitere Variante: pnp-Transistor (Spannungen umpolen!) INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9-9 Kennlinienfeld eines bipolaren npn-Transistors Widerstandsgerade für Ra = 2 k, U = 5 V Ausgangskennlinien Ic = f(UCE ) IB = Parameter (Emitterschaltung) Basis-Emitter-Sättigungsspannung UBE sat = f (IC ) Ic [mA] Ic [mA] Sättigungsbereich 6 IB = 0.08 mA 5 0.06 4 3 X 2 0 0 1 2 3 4 2 1 0 5 INSTITUT FÜR TECHNISCHE INFORMATIK 5 3 0.02 Y 6 25 ° 50°C 4 0.04 1 100°C 6 UCE [V] 0 0 0. 5 Technische Grundlagen der Informatik 1. UBE sat [V] 0 9 - 10 Arbeitspunkt X (Low): UCE = UCEX 0.3 V für IB 60 A Y (High): UCE = UCEY 4.2 V für IB 0 A Arbeitspunkt X im Sättigungsbereich - Sättigung: es werden mehr Ladungsträger in die Basis gepumpt als für die Steuerung von IC erforderlich sind (siehe UBEsat = f(IC)) - Vorteil: Unabhängigkeit von Bauteiletoleranzen Nachteil: Transistor schaltet langsamer Schaltung wirkt als Inverter und Verstärker! INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 11 Inverter mit Pegelanpassung durch Spannungsteiler (z. B. Re 40 k für Kennlinien oben) Ra 1 Ra C Re B UCE Ue Vorgänger, liefert UCE als Information UCE = Ua E UBE Inverter mit Pegelanpassung R e UCE = Ue = 4.2 V UBE 0 (kann aus Kennlinien auch genauer ermittelt werden) IB = 100 A => Re = Ue/IB = 4.2 V/0.1 mA = 42 k INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 12 Reales Verhalten eines Inverters iB(t) I1 ideales Eingangssignal t uC(t) 0,9 U U 0,1 U reales Ausgangssignal tr ts tf t tr : Anstiegszeit ts : Speicherzeit tf : Abfallzeit Keine Rechteckimpulse, sondern Anstiegs- und Abfallzeiten tr und tf. Gatterverzögerung (Speicherzeit ts). INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 13 Definition von 0 und 1 Es entstehen undefinierte Zustände durch die Anstiegs- und Abfallzeiten, die nicht eindeutig 0 oder 1 zugeordnet werden können ( bei Gatterlaufzeit berücksichtigen). Ein- und Ausgangsbelastung Kann das reale Signal noch zusätzlich verändern, daher vorgegebenen Maximalwerte abhängig von Technologie. FAN-IN: Zahl von Standardlasten, mit denen ein Eingang einen treibenden Ausgang belastet (z. B. TTL-Gatter: 1) FAN-OUT: Zahl von Standardlasten, die der Ausgang eines Bausteins treiben kann (z. B. TTL-Gatter: 10) INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 14 Diode Kennlinie idealisiert real I I [mA] I A K 100°C 25°C U U0 Diode sperrt für U < U0 INSTITUT FÜR TECHNISCHE INFORMATIK U 0.2 0.4 0.6 U [V] (U0 Schwellspannung) Technische Grundlagen der Informatik 9 - 15 Schnittbild (pn-Übergang): A K p n A: Anode K: Kathode Diffusionsströme Si pn-Übergang Unterschiedliche Ladungsträgerkonzentrationen an der Grenzfläche werden durch “Diffusionsströme” ausgeglichen. Diffusionsstrom verschwindet kurz hinter der Grenzfläche durch “Rekombination” (Elektronen verschwinden in Löchern) In der Übergangszone Raumladungsgebiet. INSTITUT FÜR TECHNISCHE INFORMATIK zwischen p- und n-Halbleitern Technische Grundlagen der Informatik bildet sich ein 9 - 16 Keine äußere Spannung: Diffusionsstrom wird durch umgekehrt gerichteten Feldstrom ausgeglichen (Verarmung an freien Ladungsträgern im Übergangsgebiet). Positive äußere Spannung: Spannung im pn-Übergang erniedrigt sich, Zone geringer Leitfähigkeit schrumpft. Oberhalb einer Schwellspannung U0 ist die innere Spannung abgebaut. Diode leitet (pn-Übergang hat keinen Widerstand mehr) Negative äußere Spannung: Innere Spannung am pn-Übergang erhöht sich, die an Ladungsträgern freie Zone wächst. Diode sperrt (stellt hohen Widerstand dar) Diode kann damit je nach Polung ebenfalls als Schalter verwendet werden. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 17 Schottky-Diode I nSilizium Metall U I U Statt pn-Übergang Schottky-Kontakt, der einen Übergang von schwach dotiertem Silizium zu einem aufgedampften Metallkontakt darstellt. Kennlinie ähnlich pn-Übergang! INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 18 Feldeffekttransistor (FET) p-Kanal MOS-FET (Metal-Oxide-Semiconductor) kann ebenfalls als Schalter betrieben werden. Gate Source S G + D - SiO2 p Drain p n Si Gate aus Metall (z.B. Aluminium) Substrat Liegt am Gate G keine Spannung an, fließt kein Strom von Source S zu Drain D (Transistor sperrt). Wird an G eine negative Spannung angelegt, werden positive Ladungsträger “Löcher” dicht unter den Gate angezogen (Enhancement), negative Ladungsträger (Elektronen) verdrängt. Es bildet sich ein leitender p-Kanal, über den Strom zwischen S und D fließt (Transistor öffnet). Vorteile: Es fließt praktisch kein Strom in G, die Steuerung erfolgt über die Spannung UGS (hochohmiger Eingang). Hohe Integrationsdichte durch einfachen Aufbau. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 19 Eingangskennlinie p-Kanal MOS-FET Ausgangskennlinie p-Kanal MOS-FET Ähnliches Verhalten wie Bipolartransistor, aber statt Basisstrom Steuerung über Gate-Source-Spannung (hochohmiger Eingang). INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 20 Depletion-MOS-FET S G p D p n Substrat Ohne Gate-Spannung fließt ein Strom durch den p-Kanal. Durch positive GateSpannung wird p-Kanal an Ladungsträgern verarmt, d. h. es fließt weniger bzw. kein Strom. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 21 Eingangskennlinien und Schaltsymbole Bei Depletion-MOS-FET ist Eingangsspannung zu positiven bzw. negativen GateSource-Spannungen hin verschoben. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 22 Inverter mit n-Kanal-Enhancement-MOS-FET UP R D G U2 S U1 Arbeitspunkte (Widerstandsgrade) Ermittlung analog zu Bipolartransistoren. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 23 Inverter mit selbstleitendem Depletion-MOS-FET statt Widerstand R UP D-MOS U2 U1 E-MOS Für integrierte Schaltungen günstiger, da Transistoren leichter zu realisieren sind als Widerstände! INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 24 9.2 Schaltkreisfamilien Bipolare Transistoren und MOS-Feldeffekttransistoren Beispiele: npn-Transistor (epitaxial) INSTITUT FÜR TECHNISCHE INFORMATIK p-Kanal MOS-Transistor (PMOS) Technische Grundlagen der Informatik 9 - 25 Bipolare Schaltkreisfamilien RTL (Resistor-Transistor-Logik): veraltet DTL (Dioden-Transistor-Logik): veraltet TTL (Transistor-Transistor-Logik): Standardfamilie ECL (Emitter-Coupled-Logic): sehr schnell I2L (Integrierte Injektionslogik): Mikroprozessoren, Gate-Arrays schnell, aber im Vergleich zu MOS niedrigere Integrationsdichten und höhere Ströme INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 26 MOS-Schaltkreisfamilien Beispiel: NAND-Gatter U - U P U P N A E1 + P P E2 PMOS E1 N E2 N A NMOS + P E1 N E2 N A CMOS hohe Integrationsdichten früher langsamer als bipolare Techniken (heute schnelle CMOS-Techniken bekannt) Standard bei VLSI-Bauelementen (Mikroprozessor, Speicher, kundenspezifische Schaltkreise) hoher Eingangswiderstand, geringe Ströme weitere Schaltkreisfamilien (z. B. Galliumarsenid) bisher nur für Spezialanwendungen von Bedeutung. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 27 Zuordnung von Spannungen zu logischen Zuständen Positive Logik: Dem positiveren von zwei definierten Spannungspegeln wird die logische ‘1‘, dem negativeren die ‘0‘ zugeordnet. Negative Logik: Dem negativeren von zwei definierten Spannungspegeln wird die logische ‘1‘, dem positiveren die ‘0‘ zugeordnet. Hier: nur positive Logik INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 28 Spannungspegel In realen Schaltungen müssen abhängig von der Schaltkreisfamilie den logischen Werten Spannungsbereiche zugeordnet werden. Beispiel: TTL-Pegel U1 U2 5V 5V “1“ 2V 0.8 V 0V TTL INVERTER Typisch 3.5 V “1“ 2.4 V nicht definiert “0“ U1 nicht definiert U2 0.4 V “0“ Unterschiedliche Bereiche für Ein- und Ausgabe. Pegel am Gatterausgang von der Last abhängig (d. h. Anzahl angeschlossener Gatter, vgl. Fan-out). INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 29 Beispiel: CMOS-Pegel U1 U2 10 V 9.95 V 10 V “1“ “1“ 7V Störspannungsabstand 3V “0“ CMOS INVERTER U1 0V U2 0.05 V “0“ Wesentlich größerer Störabstand als TTL. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 30 Schaltkreise mit diskreten Bauelementen Verwendung von diskreten Dioden, Transistoren, Widerständen, Kondensatoren, ... UND- bzw. ODER-Gatter aus Dioden und Widerständen Liegt mindestens ein Eingang auf ‘0‘, leitet die zugehörige Diode und der Ausgang ist A E2 ebenfalls ‘0‘. R Sind alle Eingänge auf ‘1‘, E1 sperren alle Dioden und der Ausgang ist ebenfalls ‘1‘. En A E2 ODER-Gatter: Liegt mindestens ein Eingang auf ‘1‘, leitet die Diode und R der Ausgang ist ‘1‘. En Sind alle Eingänge auf ‘0‘, ODER-Gatter UND - Gatter sperren alle Dioden und Ausgang ist ‘0‘. Real müssen noch die Diodenrestspannungen berücksichtigt werden. Wegen der Diodenrestspannung können nicht beliebig viele Gatter hintereinander geschaltet werden. Ausgänge sind nur gering belastungsfähig (kleiner FAN-OUT). UP E1 INSTITUT FÜR TECHNISCHE INFORMATIK UND-Gatter: Technische Grundlagen der Informatik 9 - 31 NAND-Gatter mit zwei Eingängen UP UP R1 R4 C A D1 E1 T R2 E2 R3 D2 UN Nachgeschalteter Transistor bildet Inverter, so dass aus UND-Gatter ein NAND-Gatter wird. Widerstand R2 dient der Pegelanpassung, Kondensator C der Erhöhung der Schaltgeschwindigkeit. Durch Verstärkerwirkung des Transistors höherer FAN-OUT, und es können beliebig viele Gatter hintereinander geschaltet werden. Für praktische Realisierungen vorzuziehen. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 32 Integrierte Schaltkreise Mehrere Gatter werden auf einem Chip untergebracht. SSI MSI LSI GSI VLSI Small Scale Integration (< 102 Gatterfunktionen) Medium Scale Integration (102 < Gatterfunktionen < 103) Large Scale Integration (103 < Gatterfunktionen < 104) Grand Scale Integration (104 < Gatterfunktionen < 105) Very Large Scale Integration (> 105 Gatterfunktionen) Heutige Mikroprozessoren: mehrere Millionen Gatterfunktionen! INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 33 Widerstands-Transistor-Logik NOR-Gatter in RTL-Technik (Resistor-Transistor-Logic) UP R3 A R11 E1 R12 E2 R2 Transistor leitet, wenn wenigstens ein Eingang auf hohem Potential liegt (Dimensionierung für mehr Eingänge schwierig!). INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 34 NOR-Gatter in DCTL-Technik (Direct-Coupled-Transistor-Logic) UP R2 A R 11 E1 R 12 E2 R 13 E3 Ausgang ‘0‘, wenn mindestens ein Transistor öffnet, d. h. am Eingang ‘1‘ anliegt. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 35 NAND-Gatter in RTL-Technik UP R2 A R 11 E1 R 12 E2 R 13 E3 Ausgang nur ‘0‘, wenn alle Transistoren öffnen, d. h. die Eingänge ‘1‘ sind. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 36 Dioden-Transistor-Logik (DTL) NAND-Gatter in DTL-Technik UP UP R1 D1 D3 R3 A D4 E1 R2 E2 D2 Dioden-UND-Gatter mit nachgeschaltetem Inverter (Dioden D3, D4 dienen der Pegelanpassung) INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 37 Transistor-Transistor-Logik (TTL) Heute noch weit verbreitete Standard SSI/MSI-Familie TTL-Grundschaltung (NAND) mit Multi-Emitter-Transistor) UP UP UP a) UP b) E1 ("0") E2 ("1") A ("1") E 1 ("1") E 2 ("1") A ("0") Multi-Emitter-Transistor leitet, wenn mind. ein Emitter auf ‘0‘ liegt. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 38 NAND-Gatter in TTL-Technik UP R1 UP R2 UP R3 T1 T3 E1 E2 T2 A D T4 R4 Höhere Schaltschwelle am Eingang von T2 durch Reihenschaltung zweier BasisEmitterstrecken T2 und T4 in sog. Darlington-Split-Schaltung. T3 und T4 arbeiten als Gegentaktendstufe, d. h. T3 leitet und T4 sperrt oder umgekehrt. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 39 Schottky-TTL-Technik Vermeiden der Sättigung durch Schottky-Clamp-Diode (Kollektorpotential sinkt mit wachsendem Basisstrom). Dadurch kürzere Schaltzeiten. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 40 TTL-NAND-Gatter mit ‘open Collector‘ UP UP R1 UP RL R2 externer Widerstand T1 E1 E2 T2 A T3 R3 Durch externen Widerstand können mehrere Ausgänge zu einem ‘wired-OR‘ zusammengeschaltet werden. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 41 Anwendung z. B. für Busanforderung durch mehrere Teilnehmer UP BUS A ADU & B BDU & C CDU & D DDU & INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik S 9 - 42 Tri-State-Logic UP UP UP R4 R1 R2 T3 T1 T4 E T2 I D R3 T5 T6 R5 INSTITUT FÜR TECHNISCHE INFORMATIK Durch speziellen Steuereingang I = 1 kann die Schaltung in einen hochohmigen Ausgangszustand versetzt werden, ansonsten für I = 0 wird Eingang E invertiert. Bei I = 1 wird zwar Ausgang A von T1 her auf 1 angesteuert, über Diode D jedoch die Darlington-Schaltung aus T3 und T4 gesperrt. Damit sind beide Ausgangstransistoren T4, T5 gesperrt, A d. h. hochohmiger Ausgangszustand. Anwendung z. B. für Bustreiber. Aktiver Teilnehmer legt seine Pegel auf den Bus, die passiven Teilnehmer werden in den Tri-State-Zustand versetzt. Technische Grundlagen der Informatik 9 - 43 Emittergekoppelte Logik (ECL) ECL-Grundschaltung Sättigung wird durch einen Differenzverstärker vermieden. UP R1 R2 A1 A2 E T1 T2 E REF U A1 U A2 UE U REF IE INSTITUT FÜR TECHNISCHE INFORMATIK UE = UREF: Strom IE aus der Stromquelle verteilt sich gleichmäßig auf beide Transistoren T1 und T2 (Voraussetzung R1 = R2) UE > UREF: T1 führt mehr Strom, T2 weniger Spannung an A1 sinkt, Spannung an A2 steigt UE < UREF: T2 führt mehr Strom, T1 weniger Spannung an A2 sinkt, Spannung an A1 steigt Schaltung kann daher mit Ausgang A1 als Inverter arbeiten, es liegen aber immer beide komplementären Ausgangspegel an A1 und A2 vor. Technische Grundlagen der Informatik 9 - 44 ODER-Gatter in ECL-Technik UP R1 R2 R3 T5 T1 E1 A T4 E2 T2 T3 UREF R4 R5 R6 R7 D1 D2 R8 Anstelle der ‘Stromquelle‘ wird Widerstand R6 eingesetzt. Referenzspannung UREF wird durch Dioden D1, D2 und Transistor T4 erzeugt. Ausgangssignal A wird über einen Emitterfolger T5 (Transistor in Kollektorschaltung) an R2 abgegriffen. T5 bewirkt Pegelanpassung (A < UP) an nachfolgende Stufe und vermeidet Sättigung. Vorteil: kleine Schaltzeiten (1 nsec) Nachteil: hoher Stromverbrauch (es fließt immer Strom!), niedrige Integrationsdichte INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 45 MOS-Schaltkreise NOR-Gatter in NMOS-Technik UP Kollektorwiderstand ist durch selbstleitenden Transistor T3 (Depletion-n-Kanal-Transistor) realisiert. T3 A T1 PMOS analog. T2 E1 E2 CMOS-Schaltkreise Kombination aus n-Kanal und p-Kanal-MOS-Transistoren, die stets komplementär arbeiten. Ein Transistor sperrt immer, wenn der andere leitet und umgekehrt. Stromverbrauch daher nur beim Pegelwechsel, nicht im Ruhezustand, d. h. insgesamt niedriger Stromverbrauch. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 46 CMOS-Inverter E = 0: Negative Spannung UGS = -Up am Gate von p-Kanal-Transistor T1 T1 leitet UP T1 S G D A E Nullpotential am Transistor T2 T2 sperrt Ausgang: A = 1 Gate von n-Kanal- D G S T2 (1 ˆ U p ,0 ˆ OV ) INSTITUT FÜR TECHNISCHE INFORMATIK E = 1: Positive Spannung UGS = Up am Gate von n-Kanal-Transistor T2 T2 leitet UGS = 0 für p-Kanal-Transistor T1 T1 sperrt Ausgang: A = 0 Technische Grundlagen der Informatik 9 - 47 CMOS-NAND-Gatter UP T1 UP T2 A Parallelschaltung von p-Kanal-Transistoren T1, T2 Serienschaltung von n-Kanal-Transistoren T3, T4 E1 T3 E2 T4 INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 48 CMOS-NOR-Gatter UP E1 T1 Serienschaltung von p-KanalTransistoren T1, T2 E2 T2 A T3 INSTITUT FÜR TECHNISCHE INFORMATIK T4 Parallelschaltung von n-KanalTransistoren T3, T4 Technische Grundlagen der Informatik 9 - 49 9.3 Integrierte Schaltungen für digitale Systeme Integrierte Schaltungen Fest vorgegeben Standard Anwenderspezifisch Anwenderprogrammierbar Anwender Teilentwicklung Programmierbar Reprogrammierbar Gate-Arrays Standardzellen Voll Anwenderspezifisch Standardschaltungen - Entwickler sucht sich aus einem Spektrum angebotener Bausteine die passenden aus. - fest vorgegeben oder programmierbar (einmal oder mehrmals) Anwenderspezifische Schaltungen (ASICs = Application Specific Integrated Circuits) - Entwickler trägt einen Teil oder alles zur Entwicklung der Schaltung bei. - Gate Arrays: Hersteller fertigt Gatterstruktur, Entwickler legt Verbindungsstruktur fest. - Standardzellen: Bibliothek von Zellen, die der Entwickler mittels CAD-System zum Entwurf kombiniert. - voll anwenderspezifisch: Anwender entwickelt vollständige Schaltung. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 50 Standardschaltungen Fest vorgegebene Schaltungen Beispiel: TTL-Bausteinfamilie (7400 – 4 NAND-Gatter) V VCC = 5 V CC 14 13 12 11 10 9 8 DIL (Dual In Line) Package Heute meist Low-Power Schottky 74LSx oder CMOS (74HCx) 1 2 3 4 5 6 7 GND 74er-Reihe: Praktisch alle Grundschaltungen in niedriger bis mittlerer Integrationsdichte verfügbar. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 51 Anwenderprogrammierbare Schaltungen (PLDs - Programmable Logic Devices) PROM (Programmable Read Only Memory) Eingänge (Adresse) I1 I0 PROM-Struktur ODER-Matrix I1 I0 Wort 0 UND-Matrix entspricht Wort 1 Wort 2 Sicherung Wort 3 Adressdekoder INSTITUT FÜR TECHNISCHE INFORMATIK O1 O2 Speichern der Wahrheitstafel Ausgänge Technische Grundlagen der Informatik 9 - 52 Sicherung (Fuse) vor und nach der Programmierung beim PROM Unprogrammed Fuse INSTITUT FÜR TECHNISCHE INFORMATIK Programmed Fuse Technische Grundlagen der Informatik 9 - 53 SPLD (Simple Programmable Logic Device) Ähnlich PROM mit programmierbarer UND-Matrix, ODER-Matrix oder beidem. Darstellung: Normale Darstellung A B D=A•B•C C PALPLD-Darstellung A B C D=A•B•C INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 54 Beispiel: PAL (Programmable Array Logic) programmierbare UND-Matrix, feste ODER-Matrix I0 I1 In • • • • • • • UND Matrix progammierbar ODER• • • Matrix • • • fest O0 INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik • • • • • • • • • Om 9 - 55 Realisierung einer einfachen logischen Funktion mit PAL A A•B B A•B Sicherung durchgebrannt Sicherung intakt AABB A A•B A•B B INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 56 PAL mit Register zur Realisierung von Schaltwerken Die Ausgänge der ODER-Matrix werden zum Zeitpunkt t in einem Register (taktflankengesteuerte Flipflops) gespeichert. Eingänge • • • • • • • UND • • • programmierbar fest • • • • • Matrix Takt • • progammierbar • • • • • Matrix ODER - Register Ausgänge INSTITUT FÜR TECHNISCHE INFORMATIK Die linken Ausgänge des Registers werden auf die Eingänge der UND-Matrix gegeben und bestimmen zusammen mit den Eingängen des SPLDs den Folgezustand zum Zeitpunkt t + 1. Der rechte Teil des Registers enthält die Ausgaben des SPLDs. Der Zustand des Automaten ist damit in dem linken Teil des Registers gespeichert. Technische Grundlagen der Informatik 9 - 57 Reprogrammierbare Schaltungen EPROM (Erasable Programmable Read Only Memory) FAMOS-Transistoren (Floating Gate Avalanche Injection MOS) nicht kontaktiertes Gate Ucc Aluminium Dielektrikum SiO2 p +-Si n-Substrat Nicht kontaktiertes Gate kann durch hohe Spannung beim Programmieren geladen werden (Avalanche-Durchbruch) und hält dann die Ladung, die den MOS-Transistor öffnet oder sperrt. permanente Speicherung einer 0 oder 1 Löschen durch Bestrahlung mit UV-Licht (nur alle Zellen gemeinsam). Es gibt auch EEPROMS (Electrically Erasable PROMs), die elektrisch gelöscht werden können. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 58 GAL (Generic Array Logic) Prinzipieller Aufbau wie PAL, aber reprogrammierbar A A B B +V +V +V +V Besonders für die Entwicklung (Prototyping) und die Ausbildung geeignet. Spezielles Programmiergerät erforderlich! INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 59 Beispiel: PAL/GAL 16V8 Input I/O Bis zu 16 Pins, die als Inputs genutzt werden können. Bis zu 8 Pins, die als Output genutzt werden können. I/O Pins können als Input oder Output konfiguriert werden Makrozellen (OLMC – Output Logic MacroCell) für konfigurierbare Ausgabelogik PLCC Package (oder DIL) INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 60 OLMC im Simple Mode (Input/Output für Schaltnetze) Konfiguration über Fuses AC0, AC1 und XOR, SYN Rückkopplung (Feedback) für mehrstufige Schaltnetze Ausgabe reagiert sofort auf Eingabe (kein Takt) Ausgabepins können auch als Eingabepins konfiguriert werden INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 61 OLMC im Registered Mode (Input/Output für Schaltwerke) D-Flipflop für Zustand mit Rückkopplung in UND-Matrix, externer Takt (CLK) und Output Enable (OE) Schaltnetz-Ausgabe mit Output Enable INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 62 Schaltungsbeispiel: Mod-4 Zähler DA QA DB QB QA QB QA QB QA DECODE QB QA INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 63 CPLD (Complex Programmable Logic Device) In-SystemProgrammierung, d.h. kein Programmiergerät erforderlich, sondern ‚Download‘ der Schaltung über spezielle serielle Schnittstelle in das Chip möglich. Reprogrammierbare PLDs Aufbau aus mehreren PLD-Blöcken, die über eine programmierbare Verbindungsmatrix verbunden sind. Ein/Ausgabepins ebenfalls flexibel programmierbar (z. B. invertiert/nichtinvertiert, mit/ohne Latch) INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 64 Beispiel: Altera MAX7000 I/O control block Logic array block General-purpose (LABinputs A) Logic array block (LAB B) PIA I/O control block Macrocell 1 Macrocell 1 I/O pins I/O pins 8Ð16 Macrocell 2 36 36 16 16 8-16 Macrocell 16 Macrocell 16 8-16 INSTITUT FÜR TECHNISCHE INFORMATIK Macrocell 2 8-16 Technische Grundlagen der Informatik 9 - 65 Makrozellen des MAX 7000 Maximal 5 UND-Terme, die über Expander erweitert werden können. Parallel expanders from other macrocells Product-term selection matrix Associated logic To I/O control block Expander example Shared expander 36 lines from PIA 15 expander product terms from other macrocells INSTITUT FÜR TECHNISCHE INFORMATIK Über Expander können Produktterme an andere Makrozellen weitergereicht werden. A B C E +F Technische Grundlagen der Informatik ABC(E + F)=ABCE + ABCF EF Product term from another macrocell in same LAB 9 - 66 Einige Zellen besitzen Flipflops für Schaltwerke Parallel expanders from other macrocells Global Global clear clock MUX 5 MUX 1 Productterm selection matrix PRE D/T Q From I/O To I/O C MUX 2 VCC EN CLR MUX 3 Shared expander MUX 4 36 lines from PIA 15 expander product terms from other macrocells INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 67 FPGAs (Field Programmable Logic Arrays) Logikblöcke und E/A-Blöcke, die durch den Anwender mittels einstellbarer Verbindungsstrukturen verschaltet werden können. Einstellung durch Laden von außen in flüchtige Speicherzellen (Entwicklungsphase PC, später kleines ROM) Ein- / Ausgabeblock IOB Konfigurierbarer Logikblock LB Verbindungsbereich INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 68 Struktur eines typischen FPGA-Logikblockes Comb. Logic Meist Look-Up Table (LUT), mit der alle Schaltfunktionen realisierbar sind (Speichern der Wahrheitstafel) INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 69 Struktur eines typischen FPGA-E/A-Blockes INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 70 Beispiel: XILINX Virtex II CLB CLB PLL Segmented routing single lines M SelectI/O Pins single lines hex lines Vector Based Interconnect delay=f(vector) single lines Block SelectRAM Memory Pass-transistor SSTL3 hex lines 66 MHz PCI Distributed SelectRAM Memory single lines INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 71 CLB Frames as Atomic Configuration Units Dynamische partielle Rekoniguration: Teile des FPGAs können während des Betriebs umkonfiguriert werden. (nur bei XILINX Virtex) Block-RAM INSTITUT FÜR TECHNISCHE INFORMATIK IOB Technische Grundlagen der Informatik 9 - 72 Vergleich verschiedener Typen programmierbarer Logikbausteine PAL/GAL Architektur CPLD Architektur FPGA Architektur Logik-Ressourcen Wenige und sehr einfache Ressourcen Komplexe Logik nur mit Hilfe von Feedbacks Wenige, komplexe Ressourcen Viele, sehr einfache Logikelemente Komplexer Logik erfordert viele Module Verbindungsaufbau Verdrahtungsmatrix Schaltmatrix Logik kann nur lokal genutzt werden (Routing) Geschwindigkeit Sehr schnell Langsam bei Einsatz von Feedbacks Schnell Abhängig von Verdrahtung und Platzierung Zeitliches Verhalten Vorhersagbar Vorhersagbar Nicht vorhersagbar!! Software PLD-Compiler Mapper / Fitter Place and Route, Simulation INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 73 Unterschiedliche Verdrahtung (Routing) bei FGPA und CPLD INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 74 Anwenderspezifische Schaltungen (ASICs - Application Specific Integrated Circuits) Gate Arrays Beispiel: NAND-Gatter Gatter, Flipflops etc. sind vorgegeben, Verbindungen werden im letzten Integrationsschritt hergestellt und können vom Anwender definiert werden. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 75 Prinzipielle Struktur eines Gate-Arrays INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 76 Standardzellen Logische Blöcke (Zähler, ALUs, Register) vorgegeben, die der Anwender per Integrationsmaske verbinden lassen kann. Voll integrierte Schaltung (Full Custom Design) Anwender liefert komplettes Design. Flexibelste und schnellste, aber auch aufwendigste und teuerste Lösung. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 77 9.4 Hilfsmittel für den Entwurf logischer Schaltungen (CAD = Computer-Aided Design) CAD-Systeme mit graphischen Benutzeroberflächen auf Workstations oder PCs. Enthalten neben schematischer oder textueller Eingabe i. Allg. leistungsfähige Simulatoren zum Austesten der Schaltung. Ausgabe liefert dann Daten zur Programmierung von Bausteinen oder für den Chipentwurf (z. B. Gate Arrays) beim Hersteller. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 78 Beispiel: Entwurfswerkzeuge für SPLDs Entwurfs-Editor Schematischer Entwurf Logische Gleichungen PLDBibliothek Zustandsdiagramme PLDCompiler Zeitdiagramme LogikSimulator kein Fehler Fehler PLDProgrammierung INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 79 Werkzeugkette (Tool Chain) zum Entwurf von CPLDs und FPGAs Design entry Schematic HDL Synthesis Timing simulation Functional simulation Implementation Device programming (downloading) HDL: Hardware Description Language INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 80 Graphische Eingabe als Schaltplan (Schematic Entry) INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 81 Textuelle Eingabe z. B. in VHDL A A LED1 R Q Q Q QNot entity S_RLatch is port (A, B: in bit; Q, QNot: inout bit); end entity S_RLatch; B C D LED1 <= ((D XOR C) XOR B) XOR A; INSTITUT FÜR TECHNISCHE INFORMATIK B S architecture Behavior of S_RLatch is begin Q <= not A or not QNot; QNot <= not B or not Q; end architecture Behavior; Technische Grundlagen der Informatik 9 - 82 Funktionelle Simulation INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 83 Synthese (Optimierung und Generierung der Netzliste) net1 net2 and1 net3 net5 net4 net6 and2 net7 net9 net8 inv1 I1 net14 A0 net11 net12 and3 net15 net13 inv2 I2 net17 A1 inv3 I3 inv4 I4 net16 net18 and4 net20 net19 net23 A2 A3 net10 net21 net22 and5 net25 net24 INSTITUT FÜR TECHNISCHE INFORMATIK O1 or1 net26 Z Netlist (Logic3) net<name>: instance<name>, <from>; <to>; instances: and1, and2, and3, and4, and5, or1, inv2, inv3, inv4; Input/outputs: I1, I2, I3, I4, O1; net1: and1, inport1; I1; net2: and1, inport2; I2; net3: and1, inport3; I3; net4: and1, inport4; I4; net5: and1, outport1; or1, inport1; net6: and2, inport1; I1; net7: and2, inport2; I3; net8: and2, inport3; inv2,outport1 net9: and2, inport4; inv4,outport1 net10: and2, outport1; or1,inport2; net11: and3, inport1; inv2,outport1 net12: and3, inport2; inv3,outport1 net13: and3, inport3; I4; net14: and3, inport4; I1; 5: and3 Technische Grundlagen der Informatik 9 - 84 Implementierung Abbildung der Netzliste auf die Zielhardware INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 85 Analyse des Zeitverhaltens (Timing) mittels Simulation Waveform Editor 1 s Name: 4 s 8 s 12 s 16 s A0 0 A1 0 A2 0 A3 0 Z Glitch X Timing-Fehler (z. B. Glitches) können noch leicht behoben werden! INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 86 Herunterladen auf Zielhardware und Test Einsatz von Messinstrumenten (Impulsgenerator, Oszilloskop etc.) INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 87 9.5 Zusammenfassung Integrierte Schaltungen Fest vorgegebene Logik 74er Reihe: Standardchips niedriger Integrationsdichte (Gatter, Flipflops, Register, ALUs etc.), die zu komplexeren Schaltungen verdrahtet werden können. Technologie: bipolar (Low Power Schottky) oder CMOS. Anwenderprogrammierbare Logik (PLDs) SPLDs: Programmierbare Logikbausteine mit mittlerer Integrationsdichte zur Realisierung von Schaltnetzen oder einfachen Schaltwerken (Mooreoder Mealy-Automaten). Technologie: meist CMOS. Einfache CADEntwurfswerkzeuge und separate Programmiergeräte. Einmal- und mehrfachprogrammierbare Varianten (PALs bzw. GALs). 74er-Reihe und PAL/GALs heute nur noch für sehr einfache Anwendungen und als Ergänzung zu höher integrierten Chips von Bedeutung. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 88 CPLDs: Reprogrammierbare Logikbausteine höherer Integrationsdichte aus mehreren SPLDs plus programmierbarer Verdrahtung. Technologie: CMOS. Im System programmierbar und nichtflüchtig. Ausgefeilte CAD-Werkzeuge (meist VHDL-basiert). Für komplexere Schaltwerke geeignet. FPGAs: Reprogrammierbare Logikbausteine hoher bis sehr hoher Integrationsdichte aus Zellen plus programmierbaren Verbindungsstrukturen. Technologie: CMOS. Im System programmierbar, aber flüchtig (Booten von PROM). Ausgefeilte CAD-Werkzeuge (meist VHDL-basiert). Für hochkomplexe Schaltungen geeignet bis hin zu SoCs (System on Chip) mit Prozessorkernen, Speichern, Peripherie etc. Einsatz von PLDs heute hauptsächlich bei kleineren Stückzahlen und Prototypen oder Anwendungen, die häufig aktualisiert werden müssen. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 89 Anwenderspezifische integrierte Schaltungen (ASICs) Gate Arrays: Vorgegebene Gatter, die anwenderspezifisch verdrahtet werden. Technologie: meist CMOS. Komplexe CAD-Werkzeuge. Standardzellen: Wie Gate Arrays, aber komplexere vorgegebene logische Blöcke wie Register, ALUs etc. Full Custom Design: voll kundenspezifisch bis auf Transistorebene. ASIC-Entwurf sehr aufwendig, langwierig und teuer. Daher nur für sehr große Stückzahlen geeignet, besonders Full Custom Design. Trend zu programmierbarer Logik, insbesondere FPGAs. Rekonfigurierbares Rechnen durch dynamische Rekonfiguration als Ergänzung/Alternative zu herkömmlichen Prozessoren. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 90 9.6 Speicher Speicherhierarchie - prozessorinterne Register (geringe Kapazität, Zugriffszeit ns-Bereich und kleiner) - Hauptspeicher (Primärspeicher) (mittlere Kapazität, Zugriffszeit Zig-ns-Bereich) - Hintergrundspeicher (Sekundärspeicher) (große Kapazität, Zugriffszeit ms und größer) INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 91 Zeitverhalten (Timing) Zugriffszeit tac: Zeit vom Anlegen der Adresse bis zur Gültigkeit der gelesenen Daten. Zykluszeit tcycle: Zeit vom Anlegen der Adresse bis zum möglichen Anlegen der nächsten Adresse. Beispiel: Zeitdiagramm eines Lesezyklus Hinweis: Bei manchen Speicherarten ist die Zykluszeit länger als die Zugriffszeit (z.B. DRAMs) INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 92 Zugriffsarten Wahlfreier Zugriff Address buffer X Y mx my m Speicher mit wahlfreiem Zugriff, RAM (Random Access Memory) • Auf die Speicherelemente kann in beliebiger Reihenfolge zugegriffen werden. Zugriffszeit und Zykluszeit sind konstant und unabhängig von der Adresse. •• Row address decoder ••• Storage cell array ••• Column address decoder Typische Realisierungsformen für Speicherelemente: Flipflops, Ladungsspeicher (Kondensatoren), früher auch Magnete (Kernspeicher) Address bus INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 93 Serieller Zugriff Speicher mit seriellem Zugriff Zugriffszeit und Zykluszeit sind von der Adresse abhängig. Typische Realisierungsformen: Magnetband, Magnetplatte, optische Platte, früher auch Lochstreifen INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 94 9.6.1 Prozessorinterne Register Realisierung mittels Flipflops in gleicher Technologie wie die zugehörigen Gatter für Schaltnetze. Prinzipiell auf Basis von rückgekoppelten NAND- bzw. NOR-Gattern implementierbar. + Beispiel: RSFF in RTLTechnologie + RC RC R3 R1 Q Q T2 T1 R4 R2 S R In manchen Technologien (z. B. CMOS) auch optimierte Implementierungen vor allem für D-Flipflops. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 95 Verwandte Schaltung: Rechteckgenerator + RC R RC R Q Q C C T2 T1 f 1 2 ln 2 R C f 1 2 RC Entsteht aus Flipflop (bistabiler Multivibrator) durch Kondensatoren in den Rückkopplungszweigen, die sich auf- und entladen. Schaltung wird dadurch astabil und pendelt zwischen beiden Zuständen hin und her (astabiler Multivibrator). Die Frequenz wird durch die Größen von R und C bestimmt. Kann als Taktgenerator (Clock Generator) verwendet werden. In der Praxis meist noch Schwingquarze zur Frequenzstabilisierung. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 96 9.6.2 Hauptspeicher (Primärspeicher) RAMSpeicher auf Halbleiterbasis Memory -cell array C0,0 Vb Power Vc C0,1 2D-Feld von 1-Bit Speicherzellen C1,0 AdressDekoder (1-aus-n) 1/4 address decoder C1,1 C2,0 C2,1 C3,0 C3,1 Adressdekoder wählt jeweils eine Zeile aus, die parallel geschrieben oder gelesen wird Kontrollsignale: A0 A1 Address CS CE WE Control lines INSTITUT FÜR TECHNISCHE INFORMATIK X0 X1 Data input Z0 Z1 Data output Technische Grundlagen der Informatik CS: Chip Select CS=1 Chip aktiviert CS=0 Chip deaktiviert WE: Write Enable WE=1: Write WE=0: Read 9 - 97 RAM-Speichertypen RandomAccess Memory (RAM) Bits stored in a semiconductor latch or flip-flop Static RAM (SRAM) Asynchronous SRAM (ASRAM) Synchronous SRAM with burst feature (SB SRAM) INSTITUT FÜR TECHNISCHE INFORMATIK Bits stored as charge on a capacitor Dynamic RAM (DRAM) Fast Page Mode DRAM (FPM DRAM) Extended Data Out DRAM (EDO DRAM) Technische Grundlagen der Informatik Burst EDO DRAM (BEDO DRAM) Synchronous DRAM (SDRAM) 9 - 98 Statischer Speicher (SRAM) Row Select 0 Flipflop als Speicherzelle Row Select 1 Memory cell Row Select 2 Flüchtiger Speicher (d. h. Inhalt geht beim Ausschalten verloren)! Row Selectn Data Input/Output Buffers and Control Data I/O Bit 0 Data I/O Bit 1 INSTITUT FÜR TECHNISCHE INFORMATIK Data I/O Bit 2 Data I/O Bit 3 Technische Grundlagen der Informatik 9 - 99 SRAM-Speicherzelle Flipflop aus rückgekoppelten Invertern und Transistoren zur Ansteuerung 1 0 „1“ „1“ 1 0 Select = 1 Bit Bit Schreiben: Lesen: Select-Leitung (vom Adressdekoder) schaltet beide Tranistoren durch. Wert auf Bit- bzw. Bit-Leitung (Datenleitungen) wird in Flipflop übernommen. Bit-Leitung und Bit-Leitung werden auf 1 voreingestellt (Precharging). Impuls auf Select-Leitung schaltet beide Transistoren durch und erzeugt Impuls auf BitLeitung bei gespeicherter 0 bzw. Bit-Leitung, bei gespeicherter 1 (zerstörungsfreies Lesen). INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 100 Beispiel für eine SRAM-Zelle mit 6 CMOS-Transistoren INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 101 Asynchrones SRAM Lesezyklus: • Adresse liegt auf Adressbus • CS (Chip Select) ist LOW • OE (Output Enable) ist LOW • Daten werden auf Datenbus ausgelesen Memory array Row decoder Address lines Schreibzyklus: • Adresse liegt auf Adressbus • CS (Chip Select) ist LOW • WE (Write Enable) ist LOW • Daten liegen auf dem Datenbus I/O0 Input data control I/O7 SB SRAM Synchronisation mit Prozessortakt und Zugriff auf mehrere aufeinanderfolgender Wörter nach Anlegen einer einzigen Adresse (Burst), typ. 4 Worte INSTITUT FÜR TECHNISCHE INFORMATIK CS WE OE G1 256 rows x 128 columns x 8 bits Column I/O Output data Column decoder Address lines G2 Technische Grundlagen der Informatik 9 - 102 Dynamischer Speicher (DRAM) Beispiel für eine DRAM-Zelle Address line Kondensatoren C als Speicherzellen Schreiben: 1 auf Adressleitung schaltet Transistor durch und lädt C bei 1 auf Datenleitung auf bzw. entlädt C bei 0. Lesen: 1 auf Adressleitung schaltet Transistor durch. Wenn C geladen war (1 gespeichert), fließt ein Strom über die Datenleitung, der vom Leseverstärker detektiert wird, bei ungeladenem C kein Strom (0 gespeichert). T C Data line D Ground Wesentlich einfacher als SRAM-Zelle, daher höhere Integrationsdichte und damit größere Kapazität pro Chip. Aber deutlich langsamer als SRAM! INSTITUT FÜR TECHNISCHE INFORMATIK C wird beim Lesen entladen und muss zurückgeschrieben werden! C verliert mit der Zeit seine Ladung und muss in regelmäßigen Abständen wiederaufgefrischt werden (Refresh). Technische Grundlagen der Informatik 9 - 103 Aufbau dynamischer Speicher (DRAMs) Beispiel: DRAM mit Organisation 220 x 1 Multiplexen von Adressleitungen Addresses Refresh control and timing RAS Refresh counter CAS Row address is latched when RAS is LOW Column address is latched when CAS is LOW Flüchtiger Speicher! 1 2 Memory array Address lines Nach Anlegen der Zeilenadresse (Row Address) wird eine ganze Zeile in den I/O-Puffer ausgelesen, danach mit Spaltenadresse (Column Adress) ein Bit ausgewählt und gelesen bzw. geschrieben. Dann Rückschreiben der ganzen Zeile in das Speicherfeld. Refresh-Logik zum zeilenweisen Wiederauffrischen des Speicherinhalts (msec-Bereich). INSTITUT FÜR TECHNISCHE INFORMATIK A0/A1 0 A1/A11 A2/A1 2 A3/A1 3 A4/A1 4 A5/A1 5 A6/A1 6 A7/A1 7 A8/A1 8 A9/A1 9 Data selector Row decoder 1024 rows 1024 columns Row address latch 1024 1 2 1 2 Column address latch 1024 Input/Output buffers and Sense amplifier Column decoder DOUT DIN 1024 CAS RAS Technische Grundlagen der Informatik R/W E 9 - 104 Varianten von DRAMs Fast Page Mode (FPM DRAM) Sukzessive Read/Write-Operationen von Spaltenadressen, die in der gleichen Zeile liegen. RAS CAS R/W Addresses Row address Column 1 address Column 2 address Valid data Valid data Column 3 address Column n address DOUT Valid data Valid data Mit Zeilenadresse wird gleich eine gesamte Zeile ausgelesen. Anschließend kann nur durch Anlegen der Spaltenadresse auf die Daten innerhalb der Zeile (‚Page‘) zugegriffen werden, ohne Zeileadresse erneut anlegen zu müssen. => Schnellerer Zugriff auf benachbarte Daten innerhalb einer Page INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 105 Weitere Varianten für schnelleren Zugriff EDO DRAM Extended Data Output DRAM: wie FPM DRAM, aber mit erneutem Lesen, auch wenn vorheriges Datum noch nicht abgeholt wurde. BEDO DRAM Burst Extended Data Output DRAM: wie EDO, aber unterstützt zusätzlich Bursts (siehe SB SRAM). SDRAMS Synchonous DRAM: wie bei SB SRAM Synchronisation mit Prozessortakt und Burst Mode. DDR-SDRAM Double Data Rate SDRAM: wie SDRAM, aber mit doppelter Datenrate durch Nutzung der aufsteigenden und abfallenden Taktflanke. DRAMs heute Standard als Hauptspeicher bei PCs und Servern, SRAMs bei kleinen schnellen Speichern wie z. B. Caches INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 106 Nur-Lesespeicher (Read-Only Memory – ROM) Read-Only Memory (ROM) Mask ROM Programmable ROM (PROM) Erasable PROM (EPROM) Ultraviolet EPROM (UV EPROM) Electrically Erasable PROM (EEPROM) Nichtflüchtige Speicher, die während des Betriebs nur gelesen werden können. Programmierung erfolgt offline. Varianten mit und ohne Löschmöglichkeit. Speichern von Programmen und Tabellen (z. B. Boot-ROM zum Urladen von Betriebssystemen), zum Laden von FPGAs oder zur Realisierung von Schaltfunktionen. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 107 Ausführungsformen von Nur-Lese-Speichern ROM PROM EPROM Read Only Memory Speicherbaustein kann nur gelesen, aber nicht beschrieben werden. Einmalige Programmierung, z. B. durch Masken bei der Chip-Herstellung. Programmable Read Only Memory Speicherbaustein kann einmal beschrieben (programmiert), danach jedoch nur noch gelesen werden. Programmierung z. B. durch Durchbrennen von Sicherungen (Fuses) mit hoher Spannung. Erasable Programmable Read Only Memory PROM, welches als Ganzes nach dem Programmieren wieder gelöscht und danach erneut programmiert werden kann (Löschen erfolgt durch Bestrahlung mit UV-Licht). Realisierung mittels Floating Gate MOS-Transistoren. EEPROM Electrically Erasable Programmable ROM EPROM, welches durch Anlegen einer Löschspannung gelöscht werden kann (keine UV-Bestrahlung mehr erforderlich). Kann im System programmiert werden. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 108 Flash-Speicher Flash-Speicherzelle Nichtflüchtig! Floating gate Control gate – – – – – – – – – – – – Drain Durch 1-Transistorzelle sehr hohe Packungsdichte. MOS transistor symbol Langsamer als DRAM vor allem beim Schreiben Source – logic 0 is stored – Anwendung wie ROM und als Sekundärspeicher (USB-Stick) logic 1 is stored Daten werden durch Ladung eines Floating Gate gespeichert (quantenmechanische Effekte). Schreiben: Durch hohe Spannung auf Control Gate wird Floating Gate geladen (‚0‘) oder nicht (‚1‘). Lesen: Selektion durch normale Spannung am Control Gate. Es fließt entweder ein Strom durch den Transistor (‚0‘ gespeichert) oder nicht (‚1‘ gespeichert). Löschen: Entfernen der Ladung vom Control Gate nur blockweise möglich. Voraussetzung für Wiederbeschreiben => Schreiben deutlich langsamer als Lesen! INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 109 Organisationsformen von RAM-Speichern RAM. RAM-Chips besitzen Organisation 2mx n mit n = 1, 2, 4 oder 8 m bits m bits RAM 1 m 2 n m bits RAM 2 2m n Address bus RAM 2m 2n Data in/out n bits Data in/out n bits Control bus 2n bits Data bus Größere Wortlängen durch Parallelschalten von RAM-Chips: Gemeinsamer Adress- und Kontrollbus, separater Datenbus INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 110 RAM 2M 8 Address bus 21 bits RAM 1 1M 8 EN 20 bits 8 bits Control bus 8 bits 20 bits Data bus RAM 2 1M 8 EN 8 bits Größere Speicherkapazität durch Hintereinanderschalten von RAM-Chips: Gleicher Datenbus (meist Tristate) und Kontrollbus, Selektion von jeweils einem Chip durch höchstwertige Adressbits Andere Speicherarten (ROM, EPROM, Flash) etc. ganz entsprechend)! INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 111 Bauformen von RAM-Speichern Heute oft als Speicherriegel mit 2m x 1 Chips und Wortlänge von 8 Bit (Byte-Adressierung) 1 Byte Wortlänge SIMM or DIMM Socket on system board SIMM: Single In-Line Memory Module (einseitig bestückt) DIMM: Dual In-Line Memory Module (beidseitig bestückt) Eventuell zusätzliche Chips für Paritätsbits zur Fehlererkennung oder -korrektur. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 112 9.6.3 Magnetschichtspeicher Serielle Datenspeicherung durch Magnetisierung einer Magnetschicht in entgegengesetzten Richtungen zur Speicherung von 0 bzw. 1. Speicherung auch ohne Versorgungsspannung (nichtflüchtig) INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 113 Magnetbänder hohe Speicherkapazität (GByte- oder TByte-Bereich) Zugriffszeiten: Sekunden bis Minuten Historische Bandgeräte (bis ca. 80er Jahre) INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 114 Bandarchiv mit Roboter Bandkasette Einsatz zur Datensicherung und Archivierung großer Datenmengen. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 115 Hard-Disks (Festplatten) Speicherkapazität bis zu einigen hundert GByte Zugriffszeit: 1 bis 10 ms-Bereich Kreisförmige Magnetspuren, auf die über Bewegliche Schreib/Leseköpfe zugegriffen wird. I. Allg. mehrere Platten pro Platteneinheit (Disk Drive) mit eigenen Schreib/Leseköpfen. Platten sind in Spuren (Tracks) eingeteilt, diese wieder in Sektoren (Sectors). Menge der Spuren in gleicher radialer Position werden Zylinder (Cylinder) genannt. Ansteuerung durch Platten-Kontrolleinheit, die (Standard-)Schnittstelle zum Prozessor enthält. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 116 Heute meist Winchester-Disks in geschlossenen Gehäusen Spindle Platters Standard-Sekundärspeicher in PCs, Notebooks und Servern Actuator arms Read/Write heads Case Trend: Flash-Speicher (‚Solid State Disks‘) beginnen Magnetplatten zu verdrängen! Floppy-Disk Speicherkapazität im 1 MByte-Bereich Zugriffszeiten: 100 ms bis 1 s ‚Weicher‘ wechselbarer Plattenspeicher Heute durch USB-Sticks mit Flash-Speicher abgelöst! INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 117 9.6.4 Optische Speicher Aufzeichnungsprinzip optischer Speicherelemente Mittels Laser werden verschiedenartig reflektierende Bereiche (Pit und Land) abgetastet und damit eine Folge von Nullen und Einsen gelesen. Übergang 0/1 und 1/0 entspricht ‚1‘, Land oder Pit einer Folge von Nullen. Verwendung von fehlerkorrigierenden Codes (ECC Error Correcting Code) zur Erhöhung der Datensicherheit. INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 118 CD (Compact Disk) ROM Datenspeicher auf Audio-CD-Basis, Nur-Lese-Speicher Speicherkapazität bis zu ca. 1 GByte-Bereich Zugriffszeit im 100 ms bis Sekundenbereich Auch schreib- und wiederbeschreibbare Varianten (mit Laser) DVDs (Digital Versatile Disks) (ca. 10 GByte) Kurzwelligerer Laser, daher feinere Strukturen. Blue-Ray (25-50 GB) Blauer Laser mit sehr kurzer Wellenlänge. Anwendung optischer Speicher als Wechselspeicher z. B. für Programme oder Multimedia-Daten (Texte, Bilder, Audio, Video etc.) INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 119 9.7 Ausblick: Mikrocontroller-Platinen (Boards) Beispiel: Ethernut 2.3 (Fa. Egnite – Open Source) •ATmega128 RISC microcontroller (14 MHz) •Full duplex 10/100 Mbps Ethernet controller •Two serial ports, RS-232 half duplex RS-485 •128 KByte Flash ROM and 512 KByte serial Dataflash •4 KByte in-system programmable EEPROM •32 KByte SRAM plus 480 KByte banked SRAM •Up to 28 programmable digital I/O lines •8-channel, 10-bit analog/digital converter •Two 8-bit and two 16-bit timer/counters •Watchdog timer for enhanced reliability •LED indicators for power supply and Ethernet activity •Single power supply 9-12V DC INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 120 Blockschaltbild SMD-Technik (Surface Mounted Devices), d. h. Chips werden direkt auf Platine von oben aufgelötet (keine Löcher für Pins!). Hochintegrierte Chips: Mikrocontroller, Speicher (Flash und SRAM), Ethernet Controller CPLD: Memory Controller Niedrig integrierte Chips: Serielle Schnittstellen (RS 232, RS485), Spannungsregler Glue Logic (aus TTL-Familie in CMOS) in Miniatur SMD-Gehäusen Diskrete Bauelemente: Widerstände, Leuchdioden (LEDs), Kondensatoren zur Spannungspufferung, Quarze für Takterzeugung in Miniatur-SMD-Ausführung INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 121 Schaltplan (Ausschnitt) RS232 Mikrocontroller RS485 Quarz Programmierschnittstelle INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 122 Glue Logic RAM Flash CPLD Stecker INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 123 Anwendungen •Networked sensors •Remote monitoring equipment •Alarm service providing •Remote diagnose and service •Industrial Ethernet applications •Home and building control •Mobile Robotics Beispiel: Unterwasserroboter Monsun (ITI) Trend: Immer höherer Leistung und immer mehr Funktionen auf einem Chip integriert System-on-Chip (SoC) INSTITUT FÜR TECHNISCHE INFORMATIK Technische Grundlagen der Informatik 9 - 124