Newsletter - RWTH AACHEN UNIVERSITY IT Center

Werbung

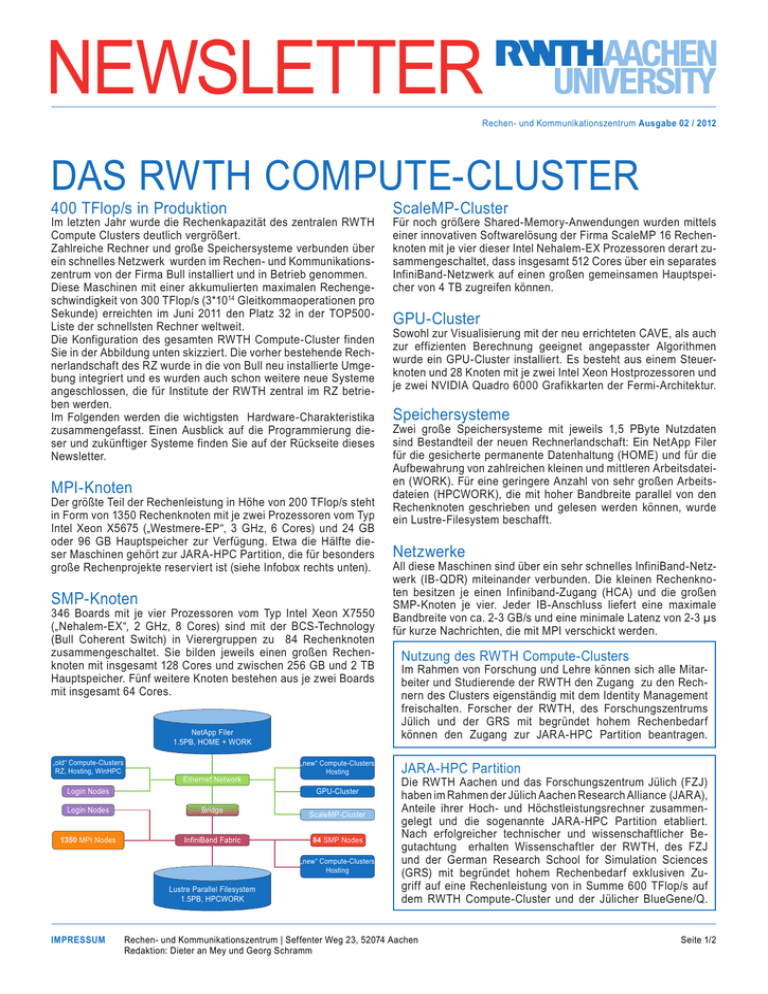

Newsletter Rechen- und Kommunikationszentrum Ausgabe 02 / 2012 Das RWTH Compute-Cluster 400 TFlop/s in Produktion Im letzten Jahr wurde die Rechenkapazität des zentralen RWTH Compute Clusters deutlich vergrößert. Zahlreiche Rechner und große Speichersysteme verbunden über ein schnelles Netzwerk wurden im Rechen- und Kommunikationszentrum von der Firma Bull installiert und in Betrieb genommen. Diese Maschinen mit einer akkumulierten maximalen Rechengeschwindigkeit von 300 TFlop/s (3*1014 Gleitkommaoperationen pro Sekunde) erreichten im Juni 2011 den Platz 32 in der TOP500Liste der schnellsten Rechner weltweit. Die Konfiguration des gesamten RWTH Compute-Cluster finden Sie in der Abbildung unten skizziert. Die vorher bestehende Rechnerlandschaft des RZ wurde in die von Bull neu installierte Umgebung integriert und es wurden auch schon weitere neue Systeme angeschlossen, die für Institute der RWTH zentral im RZ betrieben werden. Im Folgenden werden die wichtigsten Hardware-Charakteristika zusammengefasst. Einen Ausblick auf die Programmierung dieser und zukünftiger Systeme finden Sie auf der Rückseite dieses Newsletter. MPI-Knoten Der größte Teil der Rechenleistung in Höhe von 200 TFlop/s steht in Form von 1350 Rechenknoten mit je zwei Prozessoren vom Typ Intel Xeon X5675 („Westmere-EP“, 3 GHz, 6 Cores) und 24 GB oder 96 GB Hauptspeicher zur Verfügung. Etwa die Hälfte dieser Maschinen gehört zur JARA-HPC Partition, die für besonders große Rechenprojekte reserviert ist (siehe Infobox rechts unten). SMP-Knoten 346 Boards mit je vier Prozessoren vom Typ Intel Xeon X7550 („Nehalem-EX“, 2 GHz, 8 Cores) sind mit der BCS-Technology (Bull Coherent Switch) in Vierergruppen zu 84 Rechenknoten zusammengeschaltet. Sie bilden jeweils einen großen Rechenknoten mit insgesamt 128 Cores und zwischen 256 GB und 2 TB Hauptspeicher. Fünf weitere Knoten bestehen aus je zwei Boards mit insgesamt 64 Cores. NetApp Filer 1.5PB, HOME + WORK „old“ Compute-Clusters RZ, Hosting, WinHPC Ethernet Network Login Nodes „new“ Compute-Clusters Hosting GPU-Cluster Login Nodes Bridge 1350 MPI Nodes InfiniBand Fabric ScaleMP-Cluster 84 SMP Nodes „new“ Compute-Clusters Hosting Lustre Parallel Filesystem 1.5PB, HPCWORK ScaleMP-Cluster Für noch größere Shared-Memory-Anwendungen wurden mittels einer innovativen Softwarelösung der Firma ScaleMP 16 Rechenknoten mit je vier dieser Intel Nehalem-EX Prozessoren derart zusammengeschaltet, dass insgesamt 512 Cores über ein separates InfiniBand-Netzwerk auf einen großen gemeinsamen Hauptspeicher von 4 TB zugreifen können. GPU-Cluster Sowohl zur Visualisierung mit der neu errichteten CAVE, als auch zur effizienten Berechnung geeignet angepasster Algorithmen wurde ein GPU-Cluster installiert. Es besteht aus einem Steuerknoten und 28 Knoten mit je zwei Intel Xeon Hostprozessoren und je zwei NVIDIA Quadro 6000 Grafikkarten der Fermi-Architektur. Speichersysteme Zwei große Speichersysteme mit jeweils 1,5 PByte Nutzdaten sind Bestandteil der neuen Rechnerlandschaft: Ein NetApp Filer für die gesicherte permanente Datenhaltung (HOME) und für die Aufbewahrung von zahlreichen kleinen und mittleren Arbeitsdateien (WORK). Für eine geringere Anzahl von sehr großen Arbeitsdateien (HPCWORK), die mit hoher Bandbreite parallel von den Rechenknoten geschrieben und gelesen werden können, wurde ein Lustre-Filesystem beschafft. Netzwerke All diese Maschinen sind über ein sehr schnelles InfiniBand-Netzwerk (IB-QDR) miteinander verbunden. Die kleinen Rechenknoten besitzen je einen Infiniband-Zugang (HCA) und die großen SMP-Knoten je vier. Jeder IB-Anschluss liefert eine maximale Bandbreite von ca. 2-3 GB/s und eine minimale Latenz von 2-3 µs für kurze Nachrichten, die mit MPI verschickt werden. Nutzung des RWTH Compute-Clusters Im Rahmen von Forschung und Lehre können sich alle Mitarbeiter und Studierende der RWTH den Zugang zu den Rechnern des Clusters eigenständig mit dem Identity Management freischalten. Forscher der RWTH, des Forschungszentrums Jülich und der GRS mit begründet hohem Rechenbedarf können den Zugang zur JARA-HPC Partition beantragen. JARA-HPC Partition Die RWTH Aachen und das Forschungszentrum Jülich (FZJ) haben im Rahmen der Jülich Aachen Research Alliance (JARA), Anteile ihrer Hoch- und Höchstleistungsrechner zusammengelegt und die sogenannte JARA-HPC Partition etabliert. Nach erfolgreicher technischer und wissenschaftlicher Begutachtung erhalten Wissenschaftler der RWTH, des FZJ und der German Research School for Simulation Sciences (GRS) mit begründet hohem Rechenbedarf exklusiven Zugriff auf eine Rechenleistung von in Summe 600 TFlop/s auf dem RWTH Compute-Cluster und der Jülicher BlueGene/Q. ImpressumRechen- und Kommunikationszentrum | Seffenter Weg 23, 52074 Aachen Redaktion: Dieter an Mey und Georg Schramm Seite 1/2 Newsletter Rechen- und Kommunikationszentrum Ausgabe 02 / 2012 Multicore, manycore, too many cores? Multi-Core-Prozessoren Seit dem Jahr 2005 erobern Mehrkernprozessoren den Massenmarkt, da die Leistungsverbesserung von Prozessoren durch die weitere Erhöhung der Taktrate sich als nicht wirtschaftlich erweist. Verbesserungen der Prozessorarchitektur, die von der zunehmenden Anzahl von Transistoren pro Chipfläche profitieren, führten zu steigender Komplexität bei nur moderatem Geschwindigkeitsgewinn für die Mehrzahl der Anwendungen. Seither wird die Leistungsfähigkeit der Prozessorchips vor allem durch die Erhöhung der Anzahl der auf einem Chip angeordneten Rechenkerne (Cores) erreicht. Entsprechend gewinnt die SharedMemory-Parallelisierung an Bedeutung zur effizienten Nutzung moderner Prozessoren. Der De-facto-Standard OpenMP, dessen erste Version im Oktober vor 15 Jahren verabschiedet wurde, hat sich durchgesetzt und wird heute von allen namhaften Compilern unterstützt. Message Passing Nach wie vor wird die Parallelisierung im Hochleistungsrechnen durch das Message-Passing-Paradigma mit MPI dominiert, denn nur so lässt sich eine große Anzahl von Rechnern, die durch ein schnelles Netzwerk miteinander verbunden sind, effizient für eine Simulationsrechnung koppeln (ausgenommen von Speziallösungen wie der erwähnten Software von ScaleMP). Doch bei einer wachsenden Anzahl von Rechenkernen pro Clusterknoten, die sehr wohl alle einen MPI-Prozess ausführen können, erweist sich immer häufiger die Kombination von MPI und OpenMP als profitabel, denn alle MPI-Prozesse benötigen Platz im Hauptspeicher und müssen sich den Zugang zum Netzwerk teilen. Many-Core-Prozessoren Die Stromkosten heutiger Rechner, über deren Lebenszeit akkumuliert, erreichen ihre Anschaffungskosten und werden damit zu einem bedeutenden Kostenfaktor. Das hat die Popularität von Grafikkarten (GPU) zum Rechnen beschleunigt, da sie ein besseres Verhältnis von Watt zu Flop/s versprechen. Aber um GPUs effizient einzusetzen, ist in der Regel ein beachtlicher Programmieraufwand erforderlich. Nach der anfänglichen Programmierung mit OpenGL, dann mit CUDA und OpenCL zeichnet sich jetzt der Trend zum direktiven-basierten Programmieren von GPUs ab, der zu der neuen OpenACC-Spezifikation geführt hat. Es besteht begründete Hoffnung, dass auch hier die kommende OpenMPVersion eine Vereinheitlichung bringen wird, die einen guten Kompromiss zwischen Performance und Programmierbarkeit erlaubt und zudem auch die Portierbarkeit und Langlebigkeit von Programmen erhöht. Die Antwort des dominierenden Prozessorherstellers Intel auf den Trend zum Rechnen mit GPUs ist der zum Jahresende erwartete Xeon Phi Prozessor, der mehr als 50 Kerne auf einem Chip vereint, die zudem noch mehrere – voraussichtlich vier - Threads gleichzeitig verarbeiten können. Intel’s Versprechen lautet, dass die Programmierung dieses Many-Core-Prozessors weitgehend kompatibel ist zur Nutzung der bekannten Xeon-Prozessoren und dass die bekannten im HPC gebräuchlichen Programmiersprachen und Parallelisierungsparadigmen MPI und OpenMP voll unterstützt werden. Too Many Cores? Auch wenn mit OpenACC und künftig mit OpenMP die GPU-Programmierung vereinfacht wird und wenn Intel auf den Xeon Phi Prozessoren eine vollständige Programmierungumgebung mitliefert, so wollen diese neuen Rechenbeschleuniger – auch Akzeleratoren genannt – sorgfältig programmiert werden, damit sie einen wirklichen Vorteil bieten. Weiterhin gilt, eine höhere Rechengeschwindigkeit erfordert zunehmend skalierbare Parallelisierung. Wir im RZ möchten - mit den 128 Rechenkernen in jedem SMP-Knoten und den 512 Rechenkernen des ScaleMP-Clusters den Studenten und Wissenschaftlern heute eine Rechnerplattform anbieten, die es ihnen erlaubt ihr Know-how und ihre Software für zukünftige Prozessorarchitekturen vorzubereiten. Ferner sind wir ständig bestrebt, Ihnen Möglichkeiten zu bieten, zukunftsweisende Prozessoren zu nutzen und deren Programmiertechniken kennen zu lernen (siehe unten). Wir beraten und kooperieren gerne. Veranstaltungen ■■ aiXcelerate 2012 - Tuning for bigSMP HPC Workshop am 8.-10. Oktober 2012 ■■ OpenACC Tutorial and Workshop am 11.-12. Oktober 2012 ■■ PPCES 2013 - Einführung in die Parallelprogrammierung am 11.-15. März 2013 Nützliche Links ■■ Die JARA-HPC Partition: http://www.rz.rwth-aachen.de/jara ■■ Weitere Informationen zu den Veranstaltungen: http://www.rz.rwth-aachen.de/hpcevents ■■ Für weitere Informationen besuchen Sie bitte unsere Webseiten zum Thema Hochleistungsrechnen (HPC): http://www.rz.rwth-aachen.de/hpc ImpressumRechen- und Kommunikationszentrum | Seffenter Weg 23, 52074 Aachen Redaktion: Dieter an Mey und Georg Schramm Seite 2/2